你有沒有想過一個問題:如果外部中斷來的頻率足夠快,上一個中斷沒有處理完成,新來的中斷該如何處理?

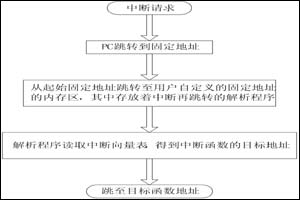

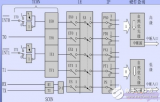

中斷一般是由硬件(例如外設(shè)、外部引腳)產(chǎn)生,當(dāng)某種內(nèi)部或外部事件發(fā)生時,MCU的中斷系統(tǒng)將迫使 CPU 暫停正在執(zhí)行的程序,轉(zhuǎn)而去進行中斷事件的處理,中斷處理完畢后,又返回被中斷的程序處,繼續(xù)執(zhí)行下去,所有的Cortex-M 內(nèi)核系統(tǒng)都有一個用于中斷處理的組件NVIC,主要負(fù)責(zé)處理中斷,還處理其他需要服務(wù)的事件。嵌套向量式中斷控制器(NVIC: Nested Vectored Interrupt Controller)集成在Cortex-M0處理器里,它與處理器內(nèi)核緊密相連,并且提供了中斷控制功能以及對系統(tǒng)異常的支持。

處理器中的NVIC能夠處理多個可屏蔽中斷通道和可編程優(yōu)先級,中斷輸入請求可以是電平觸發(fā),也可以是最小的一個時鐘周期的脈沖信號。每一個外部中斷線都可以獨立的使能、清除或掛起,并且掛起狀態(tài)也可以手動地設(shè)置和清除。

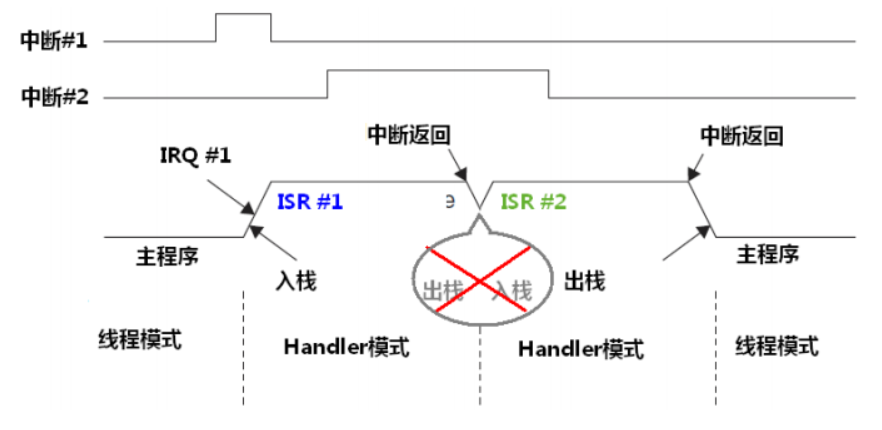

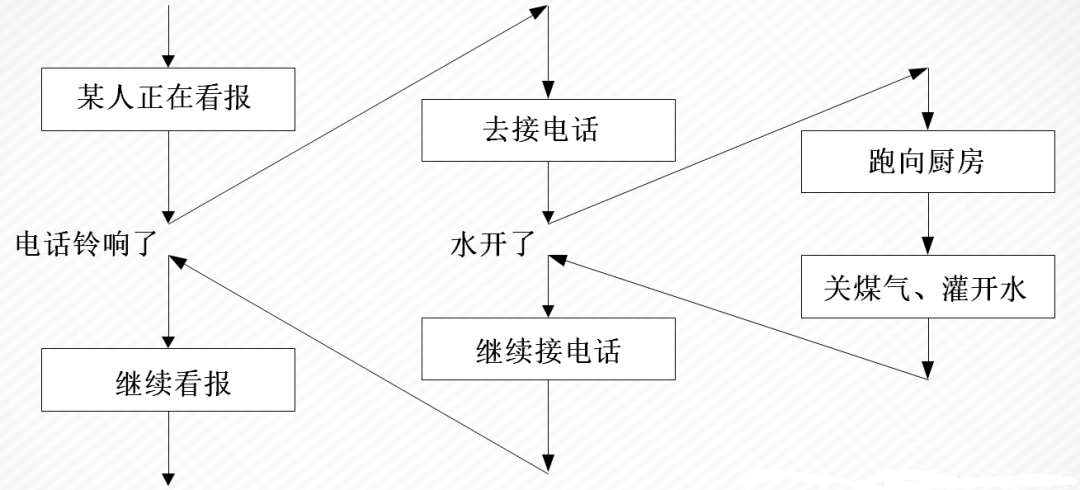

主程序正在執(zhí)行,當(dāng)遇到中斷請求(Interrupt Request)時,暫停主程序的執(zhí)行轉(zhuǎn)而去執(zhí)行中斷服務(wù)例程(Interrupt Service Routine,ISR),稱為響應(yīng),中斷服務(wù)例程執(zhí)行完畢后返回到主程序斷點處并繼續(xù)執(zhí)行主程序。多個中斷是可以進行嵌套的。正在執(zhí)行的較低優(yōu)先級中斷可以被較高優(yōu)先級的中斷所打斷,在執(zhí)行完高級中斷后返回到低級中斷里繼續(xù)執(zhí)行,采用“咬尾中斷”機制。

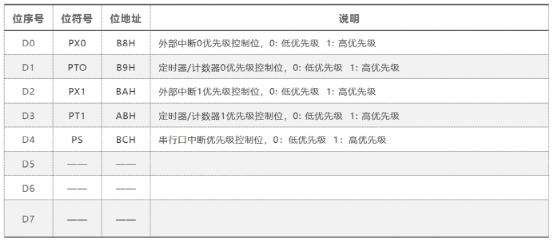

內(nèi)核中斷(異常管理和休眠模式等),其中斷優(yōu)先級則由SCB寄存器來管理,IRQ的中斷優(yōu)先級是由NVIC來管理。

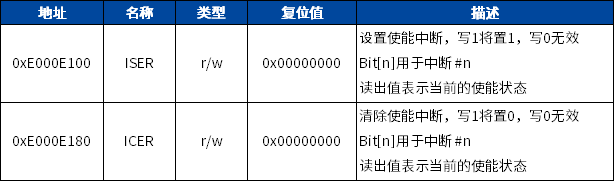

NVIC的寄存器經(jīng)過了存儲器映射,其寄存器的起始地址為0xE000E100,對其訪問必須是每次32bit。

SCB寄存器的起始地址:0xE000ED00,也是每次32bit訪問,SCB寄存器主要包含SysTick操作、異常管理和休眠模式控制。

NVIC具有以下特性:

靈活的中斷管理:使能清除、優(yōu)先級配置

硬件嵌套中斷支持

向量化的異常入口

中斷屏蔽

1. 中斷使能和清除使能

arm將處理器的中斷使能設(shè)置和清除設(shè)置寄存器分在兩個不同的地址,這種設(shè)計主要有如下優(yōu)勢:一方面這種方式減少了使能中斷所需要的步驟,使能一個中斷NVIC只需要訪問一次,同時也減少了程序代碼并且降低了執(zhí)行時間,另一方面當(dāng)多個應(yīng)用程序進程同時訪問寄存器或者在讀寫操作寄存器時有操作其他的中斷使能位,這樣就有可能導(dǎo)致寄存器丟失,設(shè)置和清除分成兩個寄存器能夠有效防止控制信號丟失。

因此我可以獨立的操作每一個中斷的使能和清除設(shè)置。

1.1 C代碼

*(volatile unsigned long) (0xE000E100) = 0x4 ; //使能#2中斷 *(volatile unsigned long) (0xE000E180) = 0x4 ; //清除#2中斷

1.2 匯編代碼

__asm void Interrupt_Enable() { LDR R0, =0xE000E100 ;

//ISER寄存器的地址

MOVS R1, #04 ; //設(shè)置#2中斷

STR R1, [R0] ;

//使能中斷#2 } __asm void Interrupt_Disable()

{ LDR R0, =0xE000E180 ; //ICER寄存器的地址 MOVS R1, #04

; //設(shè)置#2中斷 STR R1, [R0]

; //使能中斷#2 }

1.3 CMSIS標(biāo)準(zhǔn)設(shè)備驅(qū)動函數(shù)

//使能中斷#IRQn __STATIC_INLINE void __NVIC_EnableIRQ(IRQn_Type IRQn) {

if ((int32_t)(IRQn) 》= 0) {

NVIC-》ISER[0U] = (uint32_t)(1UL 《《 (((uint32_t)(int32_t)IRQn) & 0x1FUL));

} } //清除中斷#IRQn __STATIC_INLINE void __NVIC_DisableIRQ(IRQn_Type IRQn) {

if ((int32_t)(IRQn) 》= 0) {

NVIC-》ICER[0U] = (uint32_t)(1UL 《《 (((uint32_t)(int32_t)IRQn) & 0x1FUL));

__DSB();

__ISB();

} } //讀取使能中斷#IRQn __STATIC_INLINE uint32_t __NVIC_GetEnableIRQ(IRQn_Type IRQn) {

if ((int32_t)(IRQn) 》= 0) {

return((uint32_t)(((NVIC-》ISER[0U] & (1UL 《《 (((uint32_t)(int32_t)IRQn) & 0x1FUL))) != 0UL) ? 1UL : 0UL));

}

else {

return(0U); } }

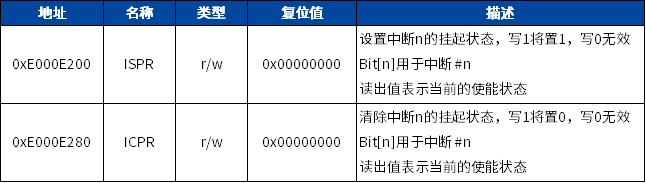

2. 中斷掛起和清除掛起

如果一個中斷發(fā)生了,卻無法立即處理,這個中斷請求將會被掛起。掛起狀態(tài)保存在一個寄存器中,如果處理器的當(dāng)前優(yōu)先級還沒有降低到可以處理掛起的請求,并且沒有手動清除掛起狀態(tài),該狀態(tài)將會一直保持。可以通過操作中斷設(shè)置掛起和中斷清除掛起兩個獨立的寄存器來訪問或者修改中斷掛起狀態(tài),中斷掛起寄存器也是通過兩個地址來實現(xiàn)設(shè)置和清除相關(guān)位。這使得每一個位都可以獨立修改,并且無需擔(dān)心在兩個應(yīng)用程序進程競爭訪問時出現(xiàn)的數(shù)據(jù)丟失。

中斷掛起狀態(tài)寄存器允許使用軟件來觸發(fā)中斷。如果中斷已經(jīng)使能并且沒有被屏蔽掉,當(dāng)前還沒有更高優(yōu)先級的中斷在運行,這時中斷的服務(wù)程序就會立即得以執(zhí)行。

2.1 C代碼

*(volatile unsigned long)(0xE000E100) = 0x4 ; //使能中斷

#2 *(volatile unsigned long)(0xE000E200) = 0x4 ; //掛起中斷

#2 *(volatile unsigned long)(0xE000E280) = 0x4 ; //清除中斷#2的掛起狀態(tài)

2.2 匯編代碼

__asm void Interrupt_Set_Pending() { LDR R0, =0xE000E100 ;

//設(shè)置使能中斷寄存器地址

MOVS R1, #0x4 ;

//中斷#2 STR R1, [R0]

; //使能#2中斷 LDR R0, =0xE000E200

; //設(shè)置掛起中斷寄存器地址 MOVS R1, #0x4

; //中斷#2 STR R1, [R0]

; //掛起#2中斷 } __asm void Interrupt_Clear_Pending() { LDR R0, =0xE000E100 ;

//設(shè)置使能中斷寄存器地址 MOVS R1,

#0x4

; //中斷#2 STR R1, [R0]

; //使能#2中斷 LDR R0, =0xE000E280

; //設(shè)置清除中斷掛起寄存器地址 MOVS R1, #0x4

; //中斷#2 STR R1, [R0] ;

//清除#2的掛起狀態(tài) }

2.3 CMSIS標(biāo)準(zhǔn)設(shè)備驅(qū)動函數(shù)

//設(shè)置一個中斷掛起 __STATIC_INLINE void __NVIC_SetPendingIRQ(IRQn_Type IRQn) {

if ((int32_t)(IRQn) 》= 0) { NVIC-》ISPR[0U] = (uint32_t)(1UL 《《 (((uint32_t)(int32_t)IRQn) & 0x1FUL));

} } //清除中斷掛起 __STATIC_INLINE void __NVIC_ClearPendingIRQ(IRQn_Type IRQn) { if ((int32_t)(IRQn) 》= 0) {

NVIC-》ICPR[0U] = (uint32_t)(1UL 《《 (((uint32_t)(int32_t)IRQn) & 0x1FUL));

} } //讀取中斷掛起狀態(tài) __STATIC_INLINE uint32_t __NVIC_GetPendingIRQ(IRQn_Type IRQn) {

if ((int32_t)(IRQn) 》= 0) {

return((uint32_t)(((NVIC-》ISPR[0U] & (1UL 《《 (((uint32_t)(int32_t)IRQn) & 0x1FUL))) != 0UL) ? 1UL : 0UL));

} else { return(0U); } }

NVIC屬于處理器內(nèi)核部分,因此在MM32 MCU芯片的用戶手冊中只有簡單的提及,沒有重點講述,需要深入了解相關(guān)寄存器和功能需要參考《Cortex-M0技術(shù)參考手冊》。

編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評論