基準(zhǔn)可讓您比較處理器,但仍有大量可變性。了解和運(yùn)行標(biāo)準(zhǔn)基準(zhǔn)可以讓設(shè)計(jì)人員更深入地了解和控制他們的應(yīng)用程序。

比較微處理器從來(lái)都不是一件容易的事。即使比較通常具有相同基本架構(gòu)的所有變體的處理器的臺(tái)式機(jī)或筆記本電腦也可能令人沮喪,因?yàn)榕c“更差”的計(jì)算機(jī)相比,具有更快數(shù)字的計(jì)算機(jī)可能運(yùn)行得非常慢。在嵌入式世界中事情變得更加艱難,處理器和配置的數(shù)量實(shí)際上是無(wú)限的。

基準(zhǔn)測(cè)試是解決這個(gè)難題的常用方法。多年來(lái),Dhrystone 基準(zhǔn)(對(duì) Whetstone 基準(zhǔn)的一種發(fā)揮,其中包括 Dhrystone 省略的浮點(diǎn)運(yùn)算)是城里唯一的游戲。但是,它存在許多重大問(wèn)題。其中最主要的是它不反映任何真實(shí)世界的計(jì)算,它只是試圖模仿各種操作的統(tǒng)計(jì)頻率。此外,編譯器通常可以在編譯時(shí)完成大部分計(jì)算,這意味著在運(yùn)行基準(zhǔn)測(cè)試時(shí)不必完成這些工作。

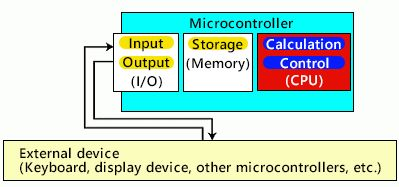

對(duì)基準(zhǔn)的真正測(cè)試是,在詳細(xì)查看結(jié)果(尤其是那些最初看起來(lái)很奇怪的結(jié)果)時(shí),您可以合理化為什么結(jié)果看起來(lái)如此。一個(gè)理想的基準(zhǔn)測(cè)試將提供一個(gè)純粹反映處理器性能能力的分?jǐn)?shù),而與系統(tǒng)的其余部分無(wú)關(guān)。不幸的是,這是不可能的,因?yàn)闆](méi)有處理器是孤立地運(yùn)行的:所有處理器都必須與內(nèi)存交互——高速緩存、數(shù)據(jù)內(nèi)存和指令內(nèi)存,其中每一個(gè)都可能會(huì)或可能不會(huì)以完整的處理器頻率運(yùn)行。此外,這些處理器必須都運(yùn)行編譯器生成的代碼,不同的編譯器生成不同的代碼。

根據(jù)您在編譯代碼時(shí)選擇的優(yōu)化設(shè)置,即使是同一個(gè)編譯器也會(huì)生成不同的代碼。這種差異是無(wú)法避免的,但要避免的主要事情是優(yōu)化實(shí)際的基準(zhǔn)代碼。

盡管結(jié)果可能取決于編譯器和內(nèi)存,但您應(yīng)該能夠僅根據(jù)處理器本身、編譯器(和設(shè)置)和內(nèi)存速度來(lái)解釋任何此類結(jié)果。Dhrystone 基準(zhǔn)測(cè)試并非如此。然而,來(lái)自嵌入式微處理器基準(zhǔn)聯(lián)盟 (EEMBC) 的最新 CoreMark 基準(zhǔn)已經(jīng)克服了這些缺陷,并被證明更加成功。

EEMBC 于 2009 年開發(fā)并公開發(fā)布了 CoreMark 基準(zhǔn)測(cè)試(現(xiàn)已有 4,100 多名用戶下載)。它已適用于包括 Android 在內(nèi)的眾多平臺(tái)。開發(fā)人員特別注意避免舊基準(zhǔn)的陷阱。通過(guò)查看 CoreMark 基準(zhǔn)測(cè)試的工作原理以及一些示例結(jié)果,我們可以看到它不僅可以作為可靠的性能指標(biāo),還可以幫助確定微控制器和編譯器性能可以改進(jìn)的地方。

CoreMark 基準(zhǔn)測(cè)試程序

CoreMark 基準(zhǔn)測(cè)試程序使用三種基本數(shù)據(jù)結(jié)構(gòu)來(lái)表示實(shí)際工作。第一個(gè)結(jié)構(gòu)是鏈表,它執(zhí)行指針操作。第二個(gè)是矩陣;矩陣運(yùn)算通常涉及緊密優(yōu)化的循環(huán)。最后,狀態(tài)機(jī)需要難以預(yù)測(cè)的分支,并且其結(jié)構(gòu)遠(yuǎn)不如用于矩陣運(yùn)算的循環(huán)。

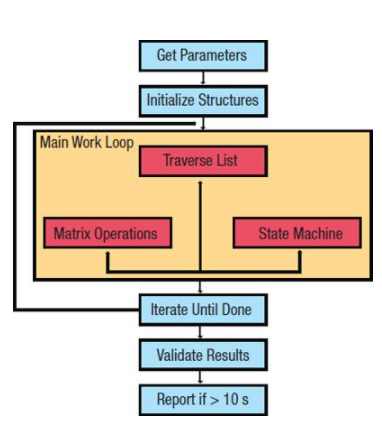

為了讓盡可能多的嵌入式系統(tǒng)(無(wú)論大小)都能訪問(wèn),該程序的代碼占用空間為 2 kb。圖 1 說(shuō)明了該程序的工作原理。前兩個(gè)步驟可能看起來(lái)微不足道,但它們實(shí)際上至關(guān)重要——它們是確保編譯器無(wú)法預(yù)先計(jì)算任何結(jié)果的步驟。直到運(yùn)行時(shí)才知道要使用的輸入數(shù)據(jù)。

圖 1:CoreMark 基準(zhǔn)測(cè)試流程。

大部分基準(zhǔn)測(cè)試工作量發(fā)生在主工作循環(huán)中。掃描其中一種數(shù)據(jù)結(jié)構(gòu),一個(gè)鏈表。每個(gè)條目的值決定了要執(zhí)行矩陣運(yùn)算還是狀態(tài)機(jī)運(yùn)算。重復(fù)此決策操作步驟,直到列表用盡。至此,單次迭代就完成了。重復(fù)工作循環(huán),直到經(jīng)過(guò)至少 10 秒。強(qiáng)制要求 10 秒以確保有足夠的數(shù)據(jù)提供有意義的結(jié)果。如果它運(yùn)行的時(shí)間少于這個(gè),那么基準(zhǔn)程序?qū)⒉粫?huì)報(bào)告結(jié)果。但是,如果用戶在模擬器上運(yùn)行基準(zhǔn)測(cè)試,則可以修改此時(shí)間要求。

主要工作完成后,利用通用循環(huán)冗余校驗(yàn)(CRC)功能;它充當(dāng)自檢以確保在執(zhí)行期間沒(méi)有出現(xiàn)任何問(wèn)題(意外或其他原因)。假設(shè)一切順利,程序會(huì)報(bào)告 CoreMark 結(jié)果。這個(gè)數(shù)字表示每秒執(zhí)行時(shí)間主工作循環(huán)的迭代次數(shù)。

雖然大多數(shù)基準(zhǔn)測(cè)試用戶都是誠(chéng)實(shí)的,但確保任何基準(zhǔn)測(cè)試方案都具有防止濫用的保護(hù)措施始終很重要。有人可以嘗試篡改結(jié)果的主要方式有兩種:編輯代碼(在移植層內(nèi)除外),因?yàn)榇a必須以源代碼形式提供,以及簡(jiǎn)單地偽造結(jié)果。CRC 有助于檢測(cè)代碼損壞時(shí)可能出現(xiàn)的任何問(wèn)題,EEMBC 技術(shù)中心的認(rèn)證是最終仲裁者。沒(méi)有人需要對(duì)其結(jié)果進(jìn)行認(rèn)證,但認(rèn)證增加了顯著的可信度,因?yàn)樗_認(rèn)中立的第三方獲得了相同的數(shù)字。

調(diào)整基準(zhǔn)測(cè)試運(yùn)行

雖然程序會(huì)根據(jù)用戶參數(shù)來(lái)初始化數(shù)據(jù),但您并沒(méi)有明確提供原始數(shù)據(jù)。那將是太多的工作,而且它還可以通過(guò)仔細(xì)選擇初始化數(shù)據(jù)來(lái)進(jìn)行操作。相反,程序會(huì)查找必須由用戶設(shè)置的三種子值。

這些數(shù)字以對(duì)用戶不透明的方式指導(dǎo)數(shù)據(jù)結(jié)構(gòu)中值的初始化。雖然它們充當(dāng)“種子”,但其中沒(méi)有隨機(jī)因素。這些結(jié)構(gòu)是完全確定的,使用相同種子多次運(yùn)行基準(zhǔn)測(cè)試將導(dǎo)致相同的執(zhí)行和結(jié)果。

您可能還需要調(diào)整基準(zhǔn)以考慮系統(tǒng)分配內(nèi)存的方式。擁有充足資源的系統(tǒng)可以簡(jiǎn)單地使用 heap 和 malloc() 調(diào)用。這允許在需要時(shí)進(jìn)行每次內(nèi)存分配,并且準(zhǔn)確地分配所需的內(nèi)存量。然而,這種靈活性是有代價(jià)的,更好的系統(tǒng)需要更快的內(nèi)存使用方式。

最快的方法是完全預(yù)分配內(nèi)存,但使用鏈表操作是不可行的。一種中間方法是創(chuàng)建許多預(yù)定義的內(nèi)存塊(內(nèi)存池),可以根據(jù)需要分配這些內(nèi)存塊。權(quán)衡是您無(wú)法選擇在每個(gè)塊中獲得多少內(nèi)存——您獲得的是固定大小的塊。移植層允許您使基準(zhǔn)測(cè)試適應(yīng)被評(píng)估系統(tǒng)上使用的內(nèi)存分配方案的類型。如果您的系統(tǒng)支持,并行性是您可以利用的另一個(gè)特征。您可以為并行操作構(gòu)建 CoreMark 基準(zhǔn),指定在執(zhí)行期間要生成的上下文(線程或進(jìn)程)的數(shù)量。但是,您應(yīng)該避免使用 CoreMark 來(lái)表示處理器的多核性能,因?yàn)檫@個(gè)基準(zhǔn)測(cè)試肯定會(huì)擴(kuò)展到 99。

理解結(jié)果

當(dāng)然,您對(duì)基準(zhǔn)測(cè)試結(jié)果所做的事情可能會(huì)導(dǎo)致混淆(有意或無(wú)意)。為此,EEMBC 提出了嚴(yán)格的報(bào)告要求。CoreMark 網(wǎng)站 http://www.coremark.org 有一個(gè)報(bào)告結(jié)果的地方,您不能只輸入一個(gè) CoreMark 分?jǐn)?shù)。還有一些其他關(guān)鍵變量可能會(huì)影響您的結(jié)果。

最大的是編譯基準(zhǔn)時(shí)使用的編譯器和設(shè)置的選項(xiàng)。您必須在提交結(jié)果時(shí)報(bào)告該信息。

第二個(gè)主要影響因素是分配內(nèi)存的方式——如果它不是堆(malloc),您必須報(bào)告所采用的方法。

相關(guān)的第三個(gè)因素是并行化。您必須報(bào)告創(chuàng)建的上下文數(shù)量。

還有另一種方法可以報(bào)告結(jié)果。您可以規(guī)范化時(shí)鐘頻率,而不是指定原始 CoreMark 值,以便單獨(dú)關(guān)注架構(gòu)效率。這是一個(gè) CoreMark/MHz 值,用于測(cè)量每百萬(wàn)時(shí)鐘周期的迭代次數(shù)。如果您報(bào)告這個(gè)數(shù)字,那么您還必須報(bào)告相對(duì)于處理器時(shí)鐘速度的內(nèi)存速度。如果可以相對(duì)于處理器頻率配置高速緩存頻率,則還必須報(bào)告該配置。

查看一些具體結(jié)果有助于了解各種所需的報(bào)告元素如何與不同的基準(zhǔn)分?jǐn)?shù)相關(guān),以及為什么在報(bào)告結(jié)果時(shí)識(shí)別這些元素很重要。以下所有數(shù)字均來(lái)自 CoreMark 網(wǎng)站上的公開結(jié)果列表。

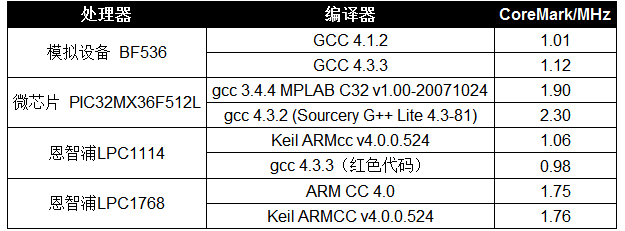

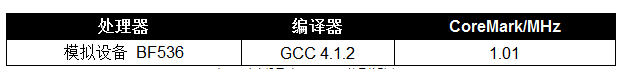

編譯器版本的簡(jiǎn)單影響可以從表 1 的結(jié)果中看出。ADI 處理器顯示,使用較新的編譯器版本可實(shí)現(xiàn) 10% 的加速,這可能表明新編譯器的性能更好。Microchip 示例顯示了兩個(gè)更遠(yuǎn)的 GNU C 編譯器 (gcc) 版本之間的更大差異。對(duì)于兩個(gè) NXP 處理器,所有編譯器都是同一版本的細(xì)微變化,從而最大限度地減少了差異。

表 1:不同編譯器對(duì) CoreMark 結(jié)果的影響。

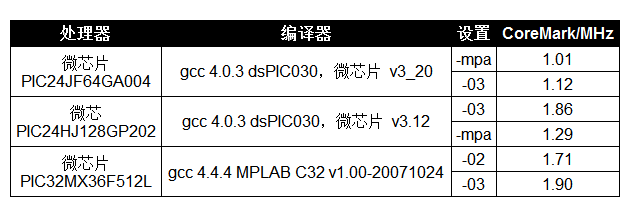

即使使用相同的編譯器,不同的設(shè)置當(dāng)然也會(huì)產(chǎn)生不同的結(jié)果,因?yàn)榫幾g器會(huì)嘗試以不同的方式優(yōu)化程序。表 2 顯示了一些示例結(jié)果。

表 2:更改編譯器設(shè)置會(huì)產(chǎn)生不同的 CoreMark 結(jié)果。

在第一個(gè)示例 (PIC24JF64GA004) 中,針對(duì)更小的代碼大小進(jìn)行優(yōu)化是以降低大約 10% 的基準(zhǔn)性能為代價(jià)的。第二種情況的差異更為顯著,當(dāng)設(shè)置了過(guò)程抽象優(yōu)化標(biāo)志 (-mpa) 時(shí),運(yùn)行速度會(huì)慢 30%。最后一個(gè)處理器上編譯器設(shè)置之間的差異也反映了優(yōu)化量的差異,大約 10% 受益于 –O3 設(shè)置提供的更高速度優(yōu)化。

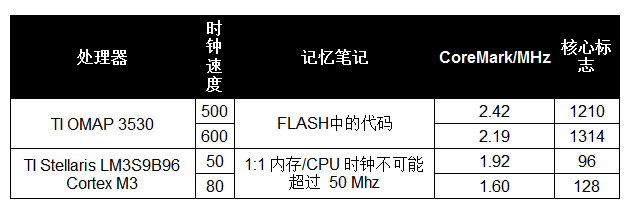

內(nèi)存的影響可以在表 3 中看到。在第一種情況下,當(dāng)時(shí)鐘頻率超過(guò)閃存可以處理的頻率時(shí),會(huì)引入等待狀態(tài),從而減少 CoreMark/MHz 數(shù)。同樣,在第二種情況下,DRAM 跟不上 50 MHz 以上的處理器,因此內(nèi)存和處理器之間的時(shí)鐘頻率比下降到 1:2,降低了 CoreMark/MHz 數(shù)。

表 4:更改緩存大小對(duì) CoreMark 結(jié)果的影響。

然而,在這兩種情況下,時(shí)鐘頻率的增加都大于運(yùn)行效率的下降,因此原始 CoreMark 數(shù)字仍然隨著時(shí)鐘頻率的增加而上升;它只是沒(méi)有增加頻率。

最后,緩存大小的影響可以在表 4 中看到。這里,代碼適合第一個(gè)配置的 2 kb 緩存,但它完全填滿了緩存。堆棧上的函數(shù)參數(shù)都不適合,因此會(huì)有一些緩存未命中。在第二種情況下,緩存的容量是第一個(gè)示例的兩倍,這意味著它不會(huì)遭受與第一個(gè)示例相同的緩存未命中,從而獲得更高的分?jǐn)?shù)。

表 3:內(nèi)存設(shè)置對(duì) CoreMark 結(jié)果的影響。

請(qǐng)注意,與第一種情況的三級(jí)管道相比,第二種情況有一個(gè)五級(jí)管道。由于狀態(tài)機(jī)示例的廣泛分支,較長(zhǎng)的管道會(huì)導(dǎo)致性能下降。當(dāng)分支被錯(cuò)誤預(yù)測(cè)時(shí),更長(zhǎng)的管道需要更長(zhǎng)的時(shí)間來(lái)重新填充。因此,較高的 CoreMark 分?jǐn)?shù)表明較大的緩存足以彌補(bǔ)這種退化。

所有這些例子中的分?jǐn)?shù)都證明了兩個(gè)事實(shí)。首先,單個(gè)數(shù)字(在本例中為 CoreMark/MHz)可以準(zhǔn)確地表示底層微控制器架構(gòu)的性能;后面的例子清楚地證明了這一點(diǎn)。然而,第二個(gè)事實(shí)是背景很重要。編譯器可以影響它生成的代碼的執(zhí)行情況。這幾乎是顯而易見的——人們花費(fèi)大量時(shí)間開發(fā)和改進(jìn)編譯器來(lái)改進(jìn)他們創(chuàng)建的結(jié)果,但“好的”結(jié)果取決于你的目標(biāo)是快速代碼還是小代碼。更快的代碼會(huì)運(yùn)行得更快,而更小的代碼則不會(huì)(除了那些實(shí)際上有助于優(yōu)化內(nèi)存或緩存利用率的情況)。

然而,這些例子顯示的最重要的事情是結(jié)果之間的差異有合理的解釋。它們不是由實(shí)際基準(zhǔn)測(cè)試代碼的某些虛構(gòu)可能導(dǎo)致一種微控制器架構(gòu)優(yōu)于另一種,或者由編譯器直接丟棄代碼引起的。從這個(gè)意義上說(shuō),CoreMark 基準(zhǔn)測(cè)試是公平和平衡的,它真實(shí)反映了編譯器和架構(gòu),并且只反映了編譯器和架構(gòu)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論