單片機(jī)電容知識(shí)大全

2014-03-27 12:26:08

如何判斷晶振是否在工作?單片機(jī)電路會(huì)存在哪些問(wèn)題?如何去排查這些問(wèn)題?

2021-07-06 07:20:12

單片機(jī)是嵌入式系統(tǒng)的核心元件,使用單片機(jī)的電路要復(fù)雜得多,但在更改和添加新功能時(shí),帶有單片機(jī)的電路更加容易實(shí)現(xiàn),這也正是電器設(shè)備使用單片機(jī)的原因。那么在單片機(jī)電路的設(shè)計(jì)中需要注意的難點(diǎn)有哪些?一

2022-01-24 08:29:57

單片機(jī)是嵌入式系統(tǒng)的核心元件,使用單片機(jī)的電路要復(fù)雜得多,但在更改和添加新功能時(shí),帶有單片機(jī)的電路更加容易實(shí)現(xiàn),這也正是電器設(shè)備使用單片機(jī)的原因。那么在單片機(jī)電路的設(shè)計(jì)中需要注意的難點(diǎn)有哪些?你都

2021-06-01 06:30:00

單片機(jī)電路設(shè)計(jì)中的10個(gè)難點(diǎn)

2022-01-10 07:05:22

旁路電容是把電源或者輸入信號(hào)中的交流分量的干擾作為濾除對(duì)象;去耦電容是芯片的電源管腳,兩者有啥區(qū)別了?詳細(xì)請(qǐng)看附件(內(nèi)有福利哦~~)

2021-09-08 10:02:18

` 本帖最后由 eehome 于 2013-1-5 10:08 編輯

去耦電容和旁路電容的區(qū)別`

2012-08-14 11:49:42

去耦電容在PCB板設(shè)計(jì)中的應(yīng)用在板設(shè)計(jì)中應(yīng)充分考慮電磁兼容方面的問(wèn)題,合理地使用去耦電容在PCB板防止電磁干擾中具有重要作用, 本文就去耦電容的容量及其具體應(yīng)用作了較為全面、詳細(xì)的敘述,同時(shí)還介紹了增強(qiáng)去耦電容效果的一些實(shí)用方法。[hide][/hide]

2009-12-09 14:08:29

旁路是把輸入信號(hào)中的干擾作為濾除對(duì)象,去耦是把輸出信號(hào)的干擾作為濾除對(duì)象。旁路電容要盡量靠近負(fù)載器件的供電電源引腳和地引腳,這樣能夠很好的防止輸入值過(guò)大而導(dǎo)致的地電位抬高和噪聲。去耦電容起到一個(gè)電池

2019-05-22 08:22:54

信號(hào)完整性之去耦電容與旁路電容

2019-11-19 14:52:05

去耦電容分為哪幾種?如何去放置去耦電容呢?在設(shè)計(jì)中如何防止上電及正常工作時(shí)出現(xiàn)總線沖突呢?

2021-11-03 07:17:04

“自偏”,但是對(duì)(交流)信號(hào)而言,這同時(shí)又是一個(gè)負(fù)反饋,為了消除這個(gè)影響,就在這個(gè)電阻上并聯(lián)一個(gè)足夠大的點(diǎn)容,這就叫旁路電容。后來(lái)也有的資料把它引申使用于類似情況。 去耦電容在集成電路電源和地之間

2012-03-08 23:42:09

去耦電容和旁路電容的區(qū)別詳解

2017-01-19 09:06:12

電子線路中的同一個(gè)電容,有時(shí)候會(huì)稱它去耦電容,有時(shí)候又會(huì)稱它為旁路電容。 電子電路中,去耦電容和旁路電容都是起到抗干擾的作用,但是,當(dāng)我們從不同的角度去看時(shí),它所起的作用是不同的,所以才有

2021-05-25 06:14:19

器(C1 和C2)情況下用于驅(qū)動(dòng) R-C 負(fù)載的緩沖電路。我們注意到,在不使用去耦電容器的情況下,電路的輸出信號(hào)包含高頻 (3.8MHz) 振蕩。對(duì)于沒有去耦電容器的放大器而言,通常會(huì)出現(xiàn)穩(wěn)定性低、瞬態(tài)響應(yīng)

2018-09-20 15:44:35

問(wèn)題。圖 1:采用去耦和不采用去耦的緩沖電路(測(cè)量結(jié)果)圖 2 闡述了為什么去耦非常重要。需要注意的是,電源線跡的電感將限制暫態(tài)電流。 去耦電容與器件非常接近,因此電流路徑的電感很小。在暫態(tài)過(guò)程中,該電容

2018-12-26 14:19:56

去耦電容的有效使用方法之一是用多個(gè)(而非1個(gè))電容進(jìn)行去耦。使用多個(gè)電容時(shí),使用相同容值的電容時(shí)和交織使用不同容值的電容時(shí),效果是不同的。

2019-08-02 06:56:29

。假設(shè)信號(hào)在電路板上的傳播速度為 166ps/inch,則波長(zhǎng)為 47.9 英寸。電容去耦半徑為 47.9/50=0.958英寸,大約等于 2.4 厘米。本例中的電容只能對(duì)它周圍 2.4 厘米范圍內(nèi)

2015-08-26 21:56:00

何為去耦技術(shù)?正確去耦有何必要性?去耦電容有哪些類型?不良去耦技術(shù)對(duì)性能的影響是什么

2021-03-11 08:14:14

)也應(yīng)該連在G上。一個(gè)雙電源運(yùn)放電路會(huì)有另外對(duì)于負(fù)電源的去耦電容,同樣應(yīng)該連在G上。有一個(gè)方案可以建立一個(gè)具有上述節(jié)點(diǎn)G接地特性的電路板。規(guī)則很簡(jiǎn)單——輸入端的地到電阻R1的線路應(yīng)該是一條干凈的路徑

2018-09-20 16:31:25

1.電源附近去耦電容的選擇很多IC管腳的VCC會(huì)增加一個(gè)0.1uf的去耦電容,因?yàn)?b class="flag-6" style="color: red">電容的濾波曲線在谷底最低的位置濾波效果最好。當(dāng)IC內(nèi)部的邏輯門頻率是是10MHz-50MHz的時(shí)候,0.1uf電容

2021-12-31 07:29:16

在高速時(shí)鐘電路中,尤其要注意元件的RF去耦問(wèn)題。究其原因,主要是因?yàn)樵?huì)把一部分能量耦合到電源/地系統(tǒng)之中。這些能量以共模或差模RF的形式傳播到其他部件中。陶瓷片電容需要比時(shí)鐘電路要求的自激

2018-11-27 15:19:23

一個(gè)原型設(shè)計(jì)電路板省去了比較麻煩的去耦電容器;但獲得的任何結(jié)果都無(wú)法與預(yù)期結(jié)果相匹配。最后,添加一個(gè)去耦電容器,問(wèn)題解決了。什么我們需要使用去耦電容器?它的作用到底是什么?

2021-04-02 07:46:38

在做高速電路設(shè)計(jì)的時(shí)候,為什么要有那么多去耦電容?到底什么是去耦?到底需要多大的去耦電容呢?為什么是很多個(gè)小電容并聯(lián)而不是用一個(gè)大電容(值是一樣大的啊)?為什么說(shuō)小電容要靠近電源管腳而大電容可以

2019-05-07 06:22:23

去耦旁路電路,不同規(guī)格的電容在PCB布局時(shí)該怎么擺

2021-03-17 07:33:04

去耦陶瓷電容在電源和地引腳的作用是什么?

2023-04-21 18:07:13

的影響。形成懸浮地或是懸浮電源,在復(fù)雜的系統(tǒng)中完成各部分地線或是電源的協(xié)調(diào)匹配,有源器件在開關(guān)時(shí)產(chǎn)生的高頻開關(guān)噪聲將沿著電源線傳播。去耦電容的主要功能就是提供一個(gè)局部的直流電源給有源器件,以減少開關(guān)噪聲在

2020-12-02 09:34:28

在單相電動(dòng)機(jī)電路中電容起什么作用呢?

2023-05-06 15:10:26

我知道在電源設(shè)計(jì)中,電源輸入與輸出都要濾波和去耦合,請(qǐng)問(wèn)下怎么叫去耦電容?什么叫旁路電容啊??我知道概念,它們兩者區(qū)別在于:旁路電容是把輸入信號(hào)中的干擾信號(hào)去掉,而去耦電容是把輸出信號(hào)中的干擾信號(hào)去掉;但是我不知道具體怎么區(qū)分?難道左邊的是旁路電容,右邊的是去耦電容嗎?

2024-01-08 11:30:57

,只是在電路上的位置不同而已。 旁路一般位于信號(hào)輸入端,去耦一般位于信號(hào)輸出端。 所以旁路電容濾除的是前級(jí)電源的干擾,一般是濾除高頻噪聲,在輸入電源管腳上加小容值電容,一般是0.1uF

2021-01-11 16:31:51

,濾除輸入信號(hào)的干擾。 2. 去耦電容 用于去耦電路中的電容叫做去耦電容,多用于多級(jí)放大器的直流電壓供給電路中,以消除每級(jí)放大器間的耦合干擾,濾除輸出信號(hào)的干擾。如下圖所示。 3. 中和 用于中和電路中

2017-09-21 10:33:05

輸入信號(hào)的干擾。2. 去耦電容用于去耦電路中的電容叫做去耦電容,多用于多級(jí)放大器的直流電壓供給電路中,以消除每級(jí)放大器間的耦合干擾,濾除輸出信號(hào)的干擾。3. 中和用于中和電路中的電容叫做中和電容,多用

2016-11-15 10:37:10

信號(hào)的干擾。去耦電容用于去耦電路中的電容叫做去耦電容,多用于多級(jí)放大器的直流電壓供給電路中,以消除每級(jí)放大器間的耦合干擾,濾除輸出信號(hào)的干擾。如下圖所示。中和用于中和電路中的電容叫做中和電容,多用

2017-10-11 20:59:45

在 EMC 設(shè)計(jì)中,電容是應(yīng)用最廣泛的元件之一,主要用于構(gòu)成各種低通濾波器或用作去耦電容和旁路電容。大 量實(shí)踐表明:在 EMC 設(shè)計(jì)中,恰當(dāng)選擇與使用電容,不僅可解決許多 EMI 問(wèn)題,而且能

2022-04-13 11:39:48

去耦的主要原因。3、等效并聯(lián)電阻EPR RL :就是我們通常所說(shuō)的電容器泄漏電阻,在交流耦合應(yīng)用、存儲(chǔ)應(yīng)用(例如模擬積分器和采樣保持器)以及當(dāng)電容器用于高阻抗電路時(shí),RL 是一項(xiàng)重要參數(shù),理想電容器中

2009-08-16 13:38:19

對(duì)于已經(jīng)知道了電容的具體特性和適用范圍,以及去耦原理,那么就知道了去耦的具體方法了嗎?不是的,下面我們將講解一下,具體安裝到電路板上之后的去耦原理以及具體如何防止電容的準(zhǔn)則!

2021-03-04 08:11:41

4片,每一片各10個(gè)管腳,四片共40個(gè)電源管腳,單片如圖 Demo給出的去耦電容一共十幾個(gè),貌似容值還有規(guī)律0.1u 0.1p 1p的各四組等 去耦電容如圖 我的第一個(gè)問(wèn)題是去耦電容 為什么要這么選擇

2016-12-13 09:34:14

`各位大神,請(qǐng)問(wèn)FPGA去耦電容如何布局、布線?1.根據(jù)文檔,一般去耦電容的數(shù)量都少于電源引腳,那么去耦電容要放到哪些管腳旁邊呢?2.以下三種方案哪種好?2.1電容放在PCB top層FPGA外圍

2017-08-22 14:57:10

想為cyclone V 系列的5CEFA7F27這款FPGA設(shè)計(jì)去耦電容電路,但是不知道該如何下手。參考了altera公司的一塊開發(fā)板,給出的FPGA的去耦電容電路如下所示,但是感覺這個(gè)去耦電容電路

2016-07-09 10:11:21

的電容必須具有較低的引線和PC走線電感,因此,各電源電容必須非常靠近它去耦的IC的兩個(gè)引腳。選擇內(nèi)部電感較低的電容也很重要,通常使用陶瓷電容。許多IC中的電路會(huì)在電源端產(chǎn)生高頻噪聲,這種噪聲也必須通過(guò)跨接

2019-05-15 04:24:21

還要考慮電容的介質(zhì),一個(gè)比較保險(xiǎn)的方法就是多并幾個(gè)電容?去耦電容在集成電路電源和地之間的有兩個(gè)作用:一方面是本集成電路的蓄能電容,另一方面旁路掉該器件的高頻噪聲?數(shù)字電路中典型的去耦電容值是0.1μF?

2019-08-26 09:41:50

和地引腳的排列位置,一般都是均勻分布在芯片的四個(gè)邊上的。因此,電壓擾動(dòng)在芯片的四周都存在,去耦也必須對(duì)整個(gè)芯片所在區(qū)域均勻去耦。如果把上圖中的680pF電容都放在芯片的上部,由于存在去耦半徑問(wèn)題,那么

2018-09-18 15:56:26

1.6nH,那么其安裝后的諧振頻率為125.8MHz,諧振周期為7.95ps。假設(shè)信號(hào)在電路板上的傳播速度為166ps/inch,則波長(zhǎng)為47.9英寸。電容去耦半徑為47.9/50=0.958英寸,大約

2018-09-12 10:46:08

2.4厘米。不同的電容,諧振頻率不同,去耦半徑也不同。對(duì)于大電容,因?yàn)槠渲C振頻率很低,對(duì)應(yīng)的波長(zhǎng)非常長(zhǎng),因而去耦半徑很大,這也是為什么我們不太關(guān)注大電容在電路板上放置位置的原因。對(duì)于小電容,因去耦半徑很小,應(yīng)盡可能的靠近需要去耦的芯片,這正是大多數(shù)資料上都會(huì)反復(fù)強(qiáng)調(diào)的,小電容要盡可能近的靠近芯片放置。

2018-09-17 17:40:22

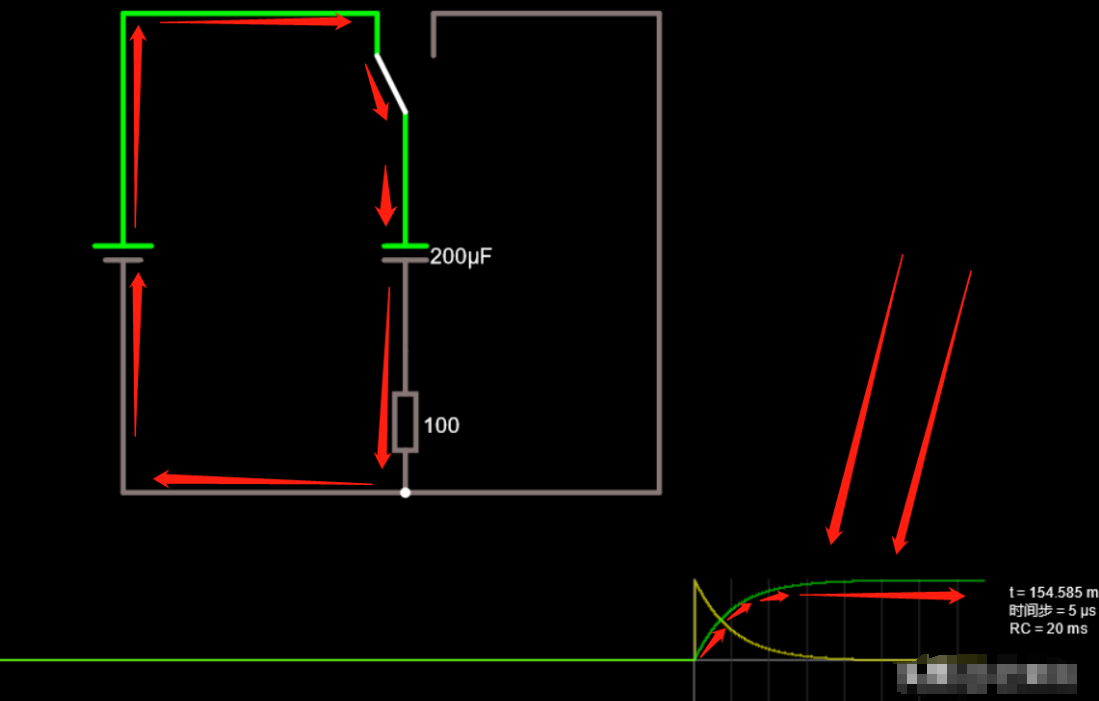

電容在集成電路電源和地之間的有兩個(gè)作用:一方面是本集成電路的蓄能電容,另一方面旁路掉該器件的高頻噪聲。數(shù)字電路中典型的去耦電容值是 0.1μF。這個(gè)電容的分布電感的典型值是 5μH。0.1μF 的去耦

2011-02-24 14:30:32

7.95ps。假設(shè)信號(hào)在電路板上的傳播速度為166ps/inch,則波長(zhǎng)為47.9英寸。電容去耦半徑為47.9/50=0.958英寸,大約等于2.4厘米。 本例中的電容只能對(duì)它周圍2.4厘米范圍內(nèi)的電源噪聲

2023-04-11 16:26:00

、IC2角度來(lái)進(jìn)行分析判斷,在實(shí)際電路中進(jìn)一步理解去耦電容和旁路電容。1、電源模塊角度站在電源模塊的角度,我們不希望電源模塊自身的干擾傳到下一級(jí)IC1中。下圖顯示了電源模塊輸出會(huì)含有高頻噪聲和低頻紋波

2022-11-04 22:29:20

輸入信號(hào)的干擾。2.去耦電容用于去耦電路中的電容叫做去耦電容,多用于多級(jí)放大器的直流電壓供給電路中,以消除每級(jí)放大器間的耦合干擾,濾除輸出信號(hào)的干擾。如下圖所示。3.中和用于中和電路中的電容叫做中和電容

2017-09-28 13:09:53

中可能沒有給出實(shí)際的PSRR,數(shù)據(jù)轉(zhuǎn)換器和其他混合信號(hào)IC的性能也會(huì)隨著電源上的噪聲而降低。電源噪聲也會(huì)以多種方式影響數(shù)字電路,包括降低邏輯電平噪聲容限,由于時(shí)鐘抖動(dòng)而產(chǎn)生時(shí)序錯(cuò)誤。? 適當(dāng)?shù)木植?b class="flag-6" style="color: red">去耦

2019-08-23 10:48:34

。? 適當(dāng)?shù)木植?b class="flag-6" style="color: red">去耦在PCB上是必不可少的 典型的4層PCB通常設(shè)計(jì)為接地層、電源層、頂部信號(hào)層和底部信號(hào)層。表面貼裝IC的接地引腳通過(guò)引腳上的過(guò)孔直接連接到接地層,從而最大限度地減少接地連接中的無(wú)用阻抗

2022-05-11 10:26:35

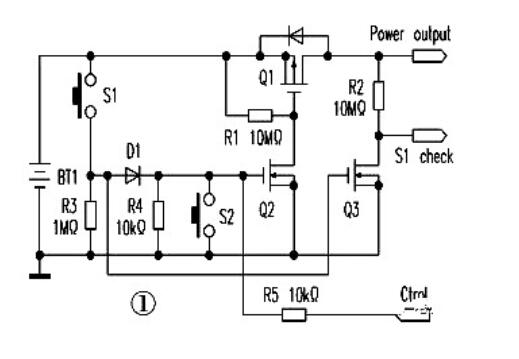

一、前言因?yàn)槌蕴澚耍也恍。l(fā)個(gè)貼記錄下,以后長(zhǎng)記性。問(wèn)題是由于不做光耦隔離,電路不穩(wěn)定,做了光耦隔離,上電和斷電瞬間被隔離器件上電抖動(dòng)一下,明顯不可以。錯(cuò)誤的示范我就不發(fā)圖了。二、環(huán)境12V電源

2021-11-26 07:46:36

TDA2030,單接每級(jí)電路都是正常工作,可是連一起就失真了,請(qǐng)問(wèn)這是這個(gè)原因嗎?還有一個(gè)問(wèn)題,去耦電容是加在每塊芯片的輸入端還是電源上啊,比如LM324,是加在3腳還是4腳啊?請(qǐng)?jiān)徫业臒o(wú)知,謝謝!

2013-05-09 19:41:13

`關(guān)于去耦電容旁路電容的總結(jié)`

2012-08-20 14:01:15

`南華大學(xué)黃智偉 注意去耦電路中電容器的使用`

2013-04-06 09:18:18

`南華大學(xué)黃智偉 注意去耦電路中電容器的使用之一`

2013-07-13 05:00:02

單片機(jī)電路板收購(gòu)多少錢,帝歐電子 專業(yè)電子收購(gòu),迅速為您報(bào)價(jià)!!【收購(gòu)主板聯(lián)系電話:135-3012-2202】【主板回收在線QQ: 8798-21252 】 單片機(jī)電路板回收,高價(jià)回收單片機(jī)電路

2021-09-07 17:48:21

多個(gè)傳感器怎么接入51單片機(jī)電路中?誰(shuí)有相關(guān)的資料,求幫忙

2017-04-07 12:05:23

怎么分清濾波電容、去耦電容、旁路電容?其實(shí)并不難~

2021-01-22 07:53:58

快速的反應(yīng)過(guò)來(lái),并且提供短時(shí)間內(nèi)的瞬態(tài)電流!這樣就不會(huì)相互影響了!在實(shí)際的電路設(shè)計(jì)中,關(guān)于電容去耦的一個(gè)重要問(wèn)題就是電容的去耦半徑,想必大家都知道很多的芯片手冊(cè)都會(huì)說(shuō)某個(gè)芯片管腳需要一個(gè)去耦電容,請(qǐng)把

2015-09-27 15:29:48

17種常見的單片機(jī)電路設(shè)計(jì)模塊

2020-12-29 07:37:50

噪聲,切斷其通過(guò)供電回路進(jìn)行傳播的通路;三是防止電源攜帶的噪聲對(duì)電路構(gòu)成干擾。在電子電路中,去耦電容和旁路電容都是起到抗干擾的作用,電容所處的位置不同,稱呼就不一樣了。對(duì)于同一個(gè)電路來(lái)說(shuō),旁路

2012-02-10 17:10:05

Walt Kester了解基于電源抑制參數(shù)的去耦需求在上一篇文章中,我們強(qiáng)調(diào)了保持低阻抗接地層對(duì)提供數(shù)字和模擬回路電流路徑的重要性。本文將討論同等重要并相關(guān)的主題:通過(guò)電源去耦來(lái)保持電源進(jìn)入集成電路

2018-10-19 10:49:11

Walt Kester在上篇文章中,我們介紹了去耦的基礎(chǔ)知識(shí)及其在實(shí)現(xiàn)集成電路(IC)期望性能方面的重要性。在本篇文章中,我們將詳細(xì)探討用于去耦的基本電路元件——電容。實(shí)際電容及其寄生效應(yīng)圖1所示為

2018-10-19 10:58:00

沿著電源線傳播。去耦電容的主要功能就是提供一個(gè)局部的直流電源給有源器件,以減少開關(guān)噪聲在板上的傳播和將噪聲引導(dǎo)到地。 從電路來(lái)說(shuō),總是存在驅(qū)動(dòng)的源和被驅(qū)動(dòng)的負(fù)載。如果負(fù)載電容比較大,驅(qū)動(dòng)電路要把電容充電

2018-12-07 09:39:59

旁路電容是把輸入信號(hào)中的干擾作為濾除對(duì)象,而去耦電容是把輸出信號(hào)的干擾作為濾除對(duì)象,防止干擾信號(hào)返回電源。這應(yīng)該是他們的本質(zhì)區(qū)別。去耦電容相當(dāng)于電池,避免由于電流的突變而使電壓下降,相當(dāng)于濾紋波

2019-05-23 06:37:11

的蓄能電容;二是濾除該器件產(chǎn)生的高頻噪聲,切斷其通過(guò)供電回路進(jìn)行傳播的通路;三是防止電源攜帶的噪聲對(duì)電路構(gòu)成干擾。 在電子電路中,去耦電容和旁路電容都是起到抗干擾的作用,電容所處的位置不同,稱呼

2013-03-08 16:33:18

濾波電容用在電源整流電路中,用來(lái)濾除交流成分。使輸出的直流更平滑。 去耦電容用在放大電路中不需要交流的地方,用來(lái)消除自激,使放大器穩(wěn)定工作。 旁路電容用在有電阻連接時(shí),接在電阻兩端使交流信號(hào)順利通過(guò)。

2010-12-24 17:12:57

的主要作用是給交流信號(hào)提供低阻抗的通路;去耦電容的主要功能是提供一個(gè)局部的直流電源給有源器件,以減少開關(guān)噪聲在板上的傳播和將噪聲引導(dǎo)到地,加入去耦電容后電壓的紋波干擾會(huì)明顯減小;濾波電容常用于濾波電路中

2018-02-05 15:13:14

電源攜帶的噪聲對(duì)電路構(gòu)成干擾。 在電子電路中,去耦電容和旁路電容都是起到抗干擾的作用,電容所處的位置不同,稱呼就不一樣了。對(duì)于同一個(gè)電路來(lái)說(shuō),旁路(bypass)電容是把輸入信號(hào)中的高頻噪聲作為濾除對(duì)象

2019-01-02 15:31:11

) y& A/ v3 C在電子電路中,去耦電容和旁路電容都是起到抗干擾的作用,電容所處的位置不同,稱呼就不一樣了。對(duì)于同一個(gè)電路來(lái)說(shuō),旁路(bypass)電容是把輸入信號(hào)中的高頻噪聲作為濾除對(duì)象

2012-04-04 23:29:40

瓷片電容、鉭電容、電解電容區(qū)別---電源設(shè)計(jì)中的去耦電容應(yīng)用實(shí)例轉(zhuǎn)自:張飛實(shí)戰(zhàn)電子電源往往是我們在電路設(shè)計(jì)過(guò)程中最容易忽略的環(huán)節(jié)。其實(shí),作為一款優(yōu)秀的設(shè)計(jì),電源設(shè)計(jì)應(yīng)當(dāng)是很重要的,它很大程度影響了

2021-11-11 08:12:14

。假設(shè)信號(hào)在電路板上的傳播速度為166ps/inch,則波長(zhǎng)為47.9英寸。電容去耦半徑為47.9/50=0.958英寸,大約等于2.4厘米。 本例中的電容只能對(duì)它周圍2.4厘米范圍內(nèi)的電源噪聲進(jìn)行

2019-09-06 18:13:24

電容在集成電路電源和地之間的有兩個(gè)作用: 一方面是本集成電路的蓄能電容,另一方面旁路掉該器件的高頻噪聲。 數(shù)字電路中典型的去耦電容值是0.1μF。這個(gè)電容的分布電感的典型值是5μH。 0.1μF的去耦

2017-05-04 10:48:07

wm-g-mr 17、18、25腳的去耦電容在主機(jī)電平為3.3V時(shí)是不是可以直接不接

2019-04-10 06:36:15

我知道在電源設(shè)計(jì)中,電源輸入與輸出都要濾波和去耦合,請(qǐng)問(wèn)下怎么叫去耦電容?什么叫旁路電容啊??我知道概念,它們兩者區(qū)別在于:旁路電容是把輸入信號(hào)中的干擾信號(hào)去掉,而去耦電容是把輸出信號(hào)中的干擾信號(hào)去掉;但是我不知道具體怎么區(qū)分?難道左邊的是旁路電容,右邊的是去耦電容嗎?

2018-10-23 09:32:13

;nbsp; 在此,需要說(shuō)明我們引入的去耦電容是為了去除比電源的去耦電容沒有濾除的更高頻率的噪聲,例如在電路板級(jí)參數(shù)中串聯(lián)電感約為L(zhǎng)serial=5nH,那么電源的退耦

2009-03-27 14:55:46

高頻干擾,以上所講述的邏輯狀態(tài)也不能被邏輯元件正確識(shí)別。 引入耦合電容,利用電容的充電和放電這一基本特性,其目的是提供充足的動(dòng)態(tài)電壓和電流。通過(guò)在電路走線和電源層上確保一個(gè)低阻抗電壓源來(lái)實(shí)現(xiàn)去耦

2018-11-23 15:59:57

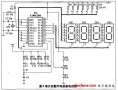

單片機(jī)數(shù)字電容表電路如下圖所示:電路由單片機(jī)電路、電容充電測(cè)量電路和數(shù)碼顯示電路等部分組成。P1.0除了做比較器同相輸入端外還作測(cè)試電容CX的放電回路。數(shù)碼管采用的是共陰

2012-07-19 09:21:55 4859

4859

單片機(jī)電路設(shè)計(jì)2,感興趣的小伙伴們可以看看。

2016-07-26 10:26:39 21

21 數(shù)字電容表protues仿真 基于51單片機(jī)電容表設(shè)計(jì)仿真源程序電容表

2017-01-14 22:32:46 49

49 本文檔的主要內(nèi)容詳細(xì)介紹的是STM8單片機(jī)電路原理圖免費(fèi)下載。

2018-11-15 11:32:30 41

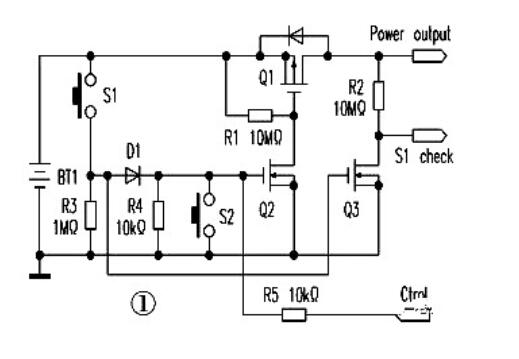

41 電路圖功用:運(yùn)用一個(gè)輕觸開關(guān)按鍵分離單片機(jī)軟件控制來(lái)完成單片機(jī)電源的“開”和“關(guān)”,在關(guān)機(jī)狀態(tài)下電路功耗極低,是一個(gè)適用性很強(qiáng)的電路。

2019-12-20 09:33:17 29918

29918

單片機(jī)是嵌入式系統(tǒng)的核心元件,使用單片機(jī)的電路要復(fù)雜得多,但在更改和添加新功能時(shí),帶有單片機(jī)的電路更加容易實(shí)現(xiàn),這也正是電器設(shè)備使用單片機(jī)的原因。那么在單片機(jī)電路的設(shè)計(jì)中需要注意的難點(diǎn)

2020-02-14 11:52:47 2169

2169 單片機(jī)電路設(shè)計(jì)中的10個(gè)難點(diǎn)

2021-11-29 15:06:04 20

20 電容在單片機(jī)電子電路中百分之九十九都會(huì)有用到。電容種類也非常多,比如安規(guī)電容,電解電容,CBB電容,貼片電容等待。安規(guī)電容一般是過(guò)EMC的時(shí)候會(huì)有用到,電解電容一般用于儲(chǔ)能濾波,貼片電容一般用于過(guò)濾雜波,CBB電容一般用于阻容降壓等待。

2023-03-27 13:52:17 2265

2265

89c51單片機(jī)電路

2023-04-20 09:15:42 2

2

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論