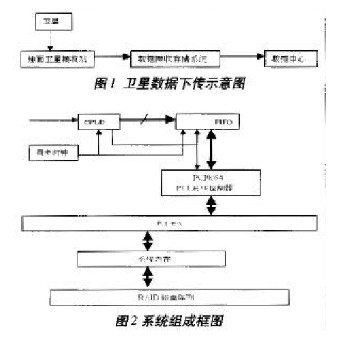

PCI總線接口芯片PCI9054及其應用

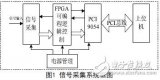

PCI9054是PLX公司推出的一種PCI主模式橋芯片。本文主要介紹了它的特性、功能及應用,說明了以PCI9054作為接口芯片,開發PCI總線擴展卡的硬件框架圖,最后給出一個簡單的實例。關鍵詞:PCI總線;局部總線;PCI9054

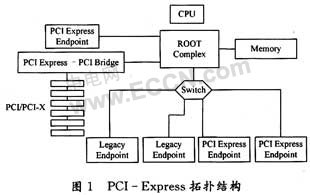

一、 引言 PCI 總線是英特爾公司推出的一種高性能局部總線,其數據總線為32 位,且可擴展成64 位,最大數據傳輸速率為128- 256MB/ s,遠遠大于ISA總線5Mbyte/s的速度,是目前使用廣泛的一種總線,可以支持突發傳送。PCI總線與CPU無關,與時鐘頻率也無關,因此它可以應用于各種平臺,支持多處理器和并發工作。

PCI總線協議比較復雜,用戶可以根據具體實際需求選擇相應的開發方式,一般,PCI總線開發采用兩種方式, 一是采用CPLD來設計控制接口。它的最大好處是比較靈活,用戶可以根據自己的需要開發出適合于特定功能的芯片,而不必實現PCI的全部功能。現在有許多生產可編程邏輯器件的廠商,如Xilinx的LogiCore和Altera的AMPP都提供經過嚴格測試的PCI接口功能模塊,用戶只要進行組合設計即可。由于PCI總線協議復雜,設計PCI控制接口難度較大,對于產品不大又有時限的工程項目來說,成本巨大,不劃算。 二是采用通用PCI接口芯片,例如南京沁恒公司的CH365,AMCC 公司的AMCC S5920、AMCC S5933,PLX 公司的PLX9054、PLX9080 等,通過專用芯片可以實現完整的PCI主控模塊和目標模塊的功能,將復雜的PCI總線接口轉換為相對簡單的用戶接口,用戶只要設計轉換后的總線接口即可,它能實現PCI規范所要求的所有硬件接口信號和配置空間寄存器,專用接口芯片具有較低的成本和通用性,能夠有效降低接口設計的難度,縮短開發時間, 并能獲得較好的數據傳輸性能。下面將主要介紹PLX公司的PCI9054接口芯片。

二、 概述 PCI9054是由美國PLX公司生產的先進的PCI I/O加速器,采用了先進的PLX數據流水線結構技術,是32位、33MHz的PCI總線主I/O加速器;符合PCI本地總線規范2.2版,突發傳輸速率達到132MB/s,本地總線支持復用/非復用的32位地址/數據;有M、C、J三種模式;針對不同的處理器及局總線特性可選,盡量減少中間邏輯;具有可選的串行E2PROM接口,本地總線時鐘可和PCI時鐘異步。PC9054內部有6種可編程的FIFO,以實現零等待突發傳輸及本地總線和PCI總線之間的異步操作;支持主模式、從模式、DMA傳輸方式,因其強大的功能可應用于適配卡和嵌入式系統中。PCI 9054是一種性比高的PCI橋路芯片,比PCI9080、PCI9050等性能更優越。

PCI9054內部圖

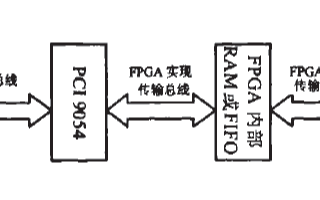

PCI 9054其內部框圖如圖所示。它采用了先進的PLX數據管道結構技術,是32Bit、33MHz的PCI總線主I/O加速器。 PCI9054主要特性如下: PCI總線接口 PCI總線狀態機 FIFO本地總線狀態機 本地總線接口 內部寄存器 串行EEPROM初始值 控 制 邏 輯 9054內部圖本地總線 PCI總線 ·符合PCI V2.1,V2.2規范,包含PCI電源管理特性。 ·支持VPD(Vital Product Data)的PCI擴展。 ·支持PCI雙地址周期,地址空間高達4GB ·具備I2O準備報文單元,完全兼容I2O V1.5規范。 ·提供了兩個獨立的可編程DMA控制器,每個通道均支持塊和Scatter/Gather的DM方式,DMA通道0支持請求DMA方式。 ·在PCI啟動模式下,PCI 9054可插入類型1和類型2的配置周期。 ·PCI和Local Bus數據傳送速率高達132MB/S。 ·支持本地總線直接接口Motorola MPC850或MPC860系列、Intel i960系列、IBMPPC401系列及其它類似總線協議設備。 ·本地總線速率高達50MHz;支持復用/非復用的32bit地址/數據;本地總線有三種模式;M模式、C模式和J模式,可利用模式選擇引腳加以選擇。 ·具有可選的串行EEPROM接口。 ·具有8個32bit Mailbox寄存器和2個32位Doorbell寄存器。

三、 功能描述

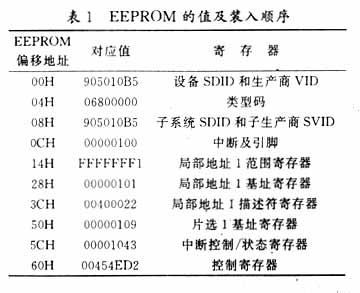

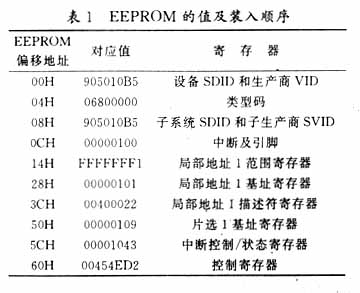

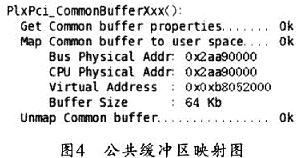

1、PCI9054的物理總線接口

PCI9054提供了三種物理總線接口:PCI總線接口,LOCAL總線接口,及串行EPROM接口。LOCAL總線的數據寬度為32位,時鐘頻率可達到50MHZ, 并且支持數據預取功能。 PCI9054的總線操作包括PCI總線操作和本地總線操作。對于PCI總線操作,它完全遵守2.2版本PCI規范。PCI9054本地總線支持非多路復用32位地址/數據總線,多路復用32位和8位,16位或32位本地總線設備從屬訪問,運行速率高達50MHz,可以獲得200MB/S的本地總線突發傳輸速率。 PCI9054的LOCAL總線與PCI總線之間數據傳輸有三種方式:主模式(Direct Master),從模式(Direct Slave),DMA方式。其內部具有兩個DMA數據通道,雙向數據通路上各有6個FIFO進行數據緩沖,可同時進行高速的數據接收和發送。8個32位Maibox寄存器可為雙向數據通路提供消息傳送。PCI9054還提供了一個串行EEPROM接口,容量2K字節。在配置存儲器中存放了廠家標示、設備標示以及本地總線的基地址空間、I/O空間、中斷控制信號等信息。當初始化時,系統自動將串行EEPROM中的配置參數裝入PCI配置寄存器,并根據本地總線對內存、I/O端口和中斷的需求統一劃分,自動配置。其中本地端寄存器也可以由本地CPU讀寫,直接進行配置。

2、PCI9054工作模式

PCI9054有3種工作模式,分別為C、M和J模式。M模式主要是針對Motorola公司高性能MPC850/860的應用而設計的,主要應用在電信領域,J模式的接口設計相對比較復雜,通常用的是C模式。 C模式下PCI9054分為PCI Initiator操作和PCI Target操作。在PIC Initiator操作過程中,本地處理器或本地總線主控設備能夠直接通過PCI9054訪問PCI總線,發起Local-to-PCI的數據傳輸。而在PCI Target操作過程中,PCI總線主控設備可以以可編程的等待狀態、總線寬度和突發傳輸功能訪問PCI9054的三個本地空間(空間0,空間1和擴充ROM空間)。

3、PCI9054的DMA突發模式

PCI9054集成了兩個互相獨立的DMA通道,每個通道都支持Block DMA和Scatter/Gather DMA,通道0還支持Demand DMA傳輸方式 Block DMA要求PCI主機或Local主機提供PCI和Local的起始地址、傳輸字節數、傳輸方向。主機設定DMA開始位啟動數據傳輸,一旦傳輸完成,PCI9054設定DMA"傳輸結束位"結束DMA,如果中斷允許位被使能,在傳輸結束時PCI9054將向主機申請中斷。在DMA傳輸中,PCI9054既是PCI總線的主控器又是Local總線的主控器。 Scatter/Gather DMA要求主機在PCI空間或Local空間設定Descriptor模塊,模塊包括PCI和Local的起始地址、傳輸字節數、傳輸方向和下一個Descriptor模塊的地址。PCI9054載入第一個Descriptor模塊并發起傳輸,連續加載下一個模塊,直到它偵測到"鏈結束位"有效,PCI 9054設置"傳輸結束位",或者申請PCI或Local中斷。這種模式下,PCI9054也可以在每個模塊加載時有效中斷信號結束DMA傳輸。若Descriptor模塊在本地存儲空間,可以編程使DMA控制器在每次DMA傳輸結束后清除傳輸字節數。

4、PCI9054寄存器

PCI9054內部提供了5種寄存器:PCI配置寄存器,本地端配置寄存器,運行時間RUNTIME寄存器,DMA寄存器和I2O信息寄存器。,下面對PCI配置寄存器和本地端配置寄存器的功能做簡要介紹。 PCI配置寄存器也就是我們常說的PCI配置空間,他提供了配置PCI的一些信息。其中VenderID,DeviceID,RevisionID,HeaderType,ClassCode用于PCI設備的識別。 命令寄存器(Command)包含設備控制位,包括允許存儲器讀寫響應等。 狀態寄存器(Status)用于記錄PCI總線的相關事件。 PCI配置寄存器提供了6個基地址寄存器,這些基地址都是在系統中的物理地址范圍內,其中BASE0和BASE1都是用來訪問其他配置寄存器的基地址,BASE1是其他配置寄存器映射到PCI端內存的基地址,BASE2是其他寄存器映射到PCI端I/O的基地址。 所以可以通過PCI端內存和PCI端I/O來訪問LOCAL配置寄存器與其他3種寄存器。BASE2~5四個空

間提供了訪問本地端所接的4個芯片(當然可以少于4個),他們將本地端的芯片通過本地端地址(在LOCAL配置寄存器中設)翻譯成PCI的地址,也就是將本地的芯片映射到系統的內存或I/O口。這樣使得用程序操作這一段內存(或I/O)實際上就是對本地的芯片操作。 本地端配置寄存器提供了本地端的一些信息

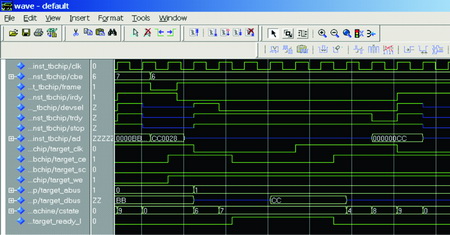

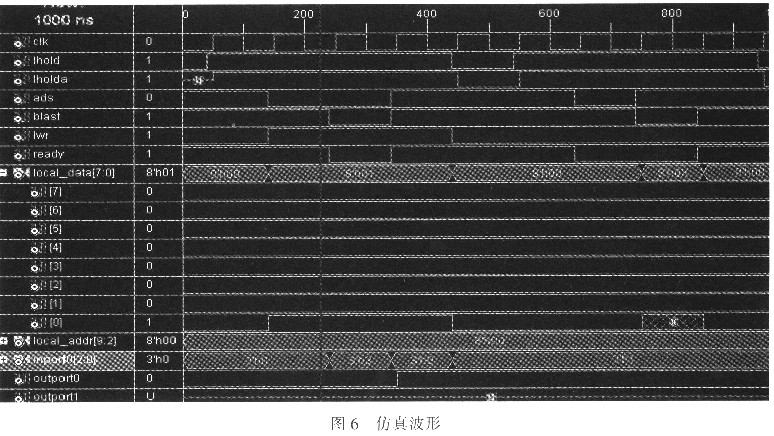

5、C模式部分時序圖

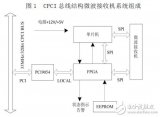

局部總線仲裁(LHOLD和LHOLFA) LCLK:輸入信號,時鐘信號 LHOLD:輸入信號,申請使用本地總線。 LHOLFA:輸入信號,對LHOLD應答。 四、 基于PCI9054的PCI接口設計 PCI 9054 以其強大的功能和簡單的用戶接口,為PCI總線接口的開發提供了一種簡潔的方法,設計者只需設計出本地總線接口控制電路,即可實現與PCI總線的高速數據傳輸。 下圖是應用PCI9054作為接口芯片,開發PCI總線擴展卡的總體硬件框架圖

下面簡單介紹以PCI9054為接口芯片的網卡設計,

1、 硬件設計 8051 RAM8位鎖存器029AS

第一部分是9054和PCI插槽間的連接信號線。這些信號包括地址數據復用信號AD[31:0],總線命令信號C/BE[3:0]#和PCI協議控制信號PAR、FRAME#、IRDY#、TRDY#、STOP#、IDSEL、PERR#、SERR#、 第二部分是9054與EEPROM的連線。這里有四根信號線:EESK、EEDO、EEDI、EECS,串行EEPROM的數據通過燒寫編程的方式,也可以通過本地CPU直接編程的方式來完成初始化 第三部分就是9054與應用電路的連接。其中LA地址總線、LD數據總線、LBE#字節使能信號和CPLD相連;LW/R讀寫信號、BLAST#、READY#、ADS#和8051單片機相連。 PCI9054工作在初始化器模式時,要求本地端的總線是32位的。在這里,用CPLD實現將80C51單片機的8位數據與16位地址轉換成32位的數據和地址,使用RAM的目的是提高8051的數據傳輸速度和處理復雜的TCP/IP協議,EEPROM用來保存些相關的信息狀態等。

2、軟件設計 軟件程序主要分為兩大部分,一是對PCI9054芯片的PCI端配置寄存器和本地端配置寄存器進行正確的編程配置;二是網絡通訊,包括網卡初始化、發送控制和接受控制3部分 五、 結束語 在實踐開發中證明,用PCI9054開發各種高速數據采集系統、圖象處理系統等PCI設備,能夠減少許多相應的外圍器件,降低了開發難度,縮短了開發周期,并且使成本有了大幅度的降低。

參考文獻: [1 ] 李貴山,戚德虎. PCI局部總線開發者指南.西安:西安電子科技大學出版社,2001 [2 ] PCI Local Bus Specification Revision 2.2 December 18, 1998 [ 3 ] PCI9054 Data Book V2.1,PLX公司.2000 [4 ] 采用8位單片機驅動PCI總線網卡的設計方案,西安理工大學.閆全成,李琦, 楊延西 作者:黃身錁,司職于福州南南信息科技有限公司,從事PCI總線、USB總線開發

電子發燒友App

電子發燒友App

評論