本文選用DSP與FPGA作為運動控制器的核心部件,設計了通用型運動控制器。其中DSP用于運動軌跡規劃、速度控制及位置控制等功能;FPGA完成運動控制器的精插補功能,用于精確計算步進電機或伺服驅動元件的控制脈沖,同時接收并處理脈沖型位置反饋信號。本文對該運動控制器的總體結構、硬件設計和軟件設計進行了描述。

1 系統總體設計

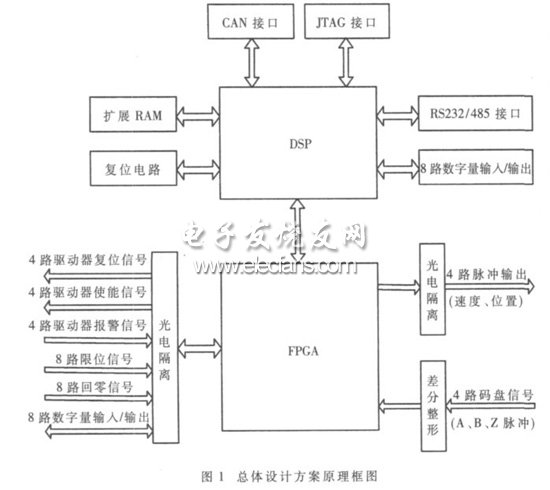

運動控制器的總體性能指標為:作為一個單獨的運動控制器使用,控制信號采用數字量方式輸出,能控制四軸的伺服電機;最高脈沖輸出頻率為4MP/s,能處理的編碼器反饋信號最高頻率為4MP/s;能接收和處理4路編碼器反饋信號;可以處理原點信號、正負方向信號、到位信號以及急停信號等數字量輸入信號;提供16路數字量輸出信號和16路數字量輸入信號接口。運動控制器采用DSP與FPGA芯片作為主控芯片,主要包括DSP模塊、FPGA模塊、FPGA外圍電路模塊和數字量輸入輸出接口模塊。

采用基于DSP與FPGA的運動控制器,能夠實時完成復雜的軌跡運算,而且利用DSP的高速數字信號處理功能和FPGA功耗低、主頻高的優點,能充分顯示該運動控制器的優點。采用DSP與FPGA相結合的運動控制器可以方便地對系統的控制策略進行修改,對控制參數進行修正,并可使設備具有良好的可靠性、可維修性,而且還降低了成本。系統還可以采用更多的智能控制策略,結構靈活,有較強的通用性,適合于模塊化設計,能夠提高算法效率,且易于維護和擴展。總體設計方案原理框圖如圖1所示。

?

2 系統硬件設計

2.1 DSP模塊

本控制器采用TI公司的TMS320F2812為主控芯片,它是32位的控制專用DSP,內含FLASH,主頻高達150MHz,具有數字信號處理、事件管理和嵌入式控制功能,適用于大批量數據處理的場合。

選用TI公司生產的TPS767D318芯片來實現TMS320-F2812的電源設計,將5V電源分別轉換為3.3V和1.8V。

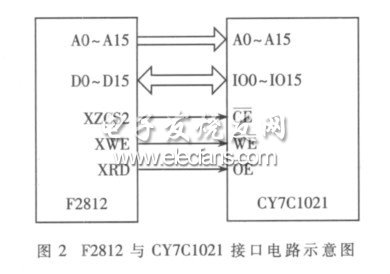

SRAM是DSP常用的外圍存儲器,它具有接口簡單、讀寫速度快等優點,所以選擇大小為64KB的隨機存儲器CY7C1021作為存儲器擴展芯片。DSPF2812與CY7C1021接口電路如圖2所示。

?

復位電路設計采用TI公司的TPS382x系列電壓監控電路,此系列電路不需要外圍電路即可組成監控電路。SCI模塊用于擴展RS-232和RS-485串行通信接口;CAN模塊和外部CAN工業現場總線相連;外部接口用于與FPGA連接和擴展數字量輸入輸出。

2.2 FPGA模塊

FPGA芯片選用Altera公司的Cyclone系列EP1C6TC44C8,這是一款高性能、低功耗的FPGA。EP1C6TC44C8具有2個鎖相環,包含5980個邏輯單元,相當于12萬門的規模,同時還包含了最高頻率200MHz、92160bit的內部RAM。該芯片所擁有的邏輯門數量、頻率和引腳I/O等資源都能很好地滿足運動控制器的設計要求。由于本系統的控制對象是伺服電機,所以設計中主要利用EP1C6TC44C8的I/O口設計電機控制信號的輸入輸出、編碼器信號的輸入與部分數字量輸入輸出。另外,該芯片在整個硬件系統設計完畢后還可以通過JTAG接口對硬件進行重配置,可以增加系統設計的靈活性。

2.3 FPGA外圍電路模塊

?

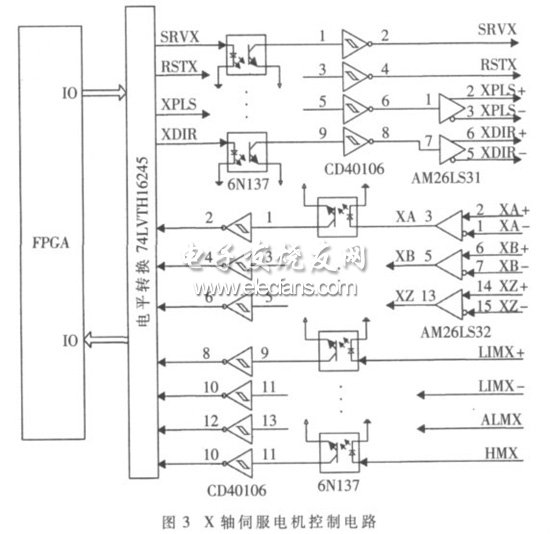

X軸伺服電機控制電路如圖3所示。Y軸、Z軸、U軸伺服電機控制電路與X軸相同。

(1)輸入輸出開關量接口設計。

輸入信號主要包括限位開關信號LIMX+、LIMX-~LIMU+、LIMU-,伺服報警信號ALMX~ALMU和回零信號HMX~HMU。輸出信號主要包括伺服使能信號SRVX~SRVU和復位信號RSTX~RSTU。當檢測到這些信號后,確定具體觸發的信號,限位信號觸發,則立即停止對應電機該方向的運動,直到限位消除,電機才能在該方向繼續運動;回零信號觸發,則電機等待Index信號的輸入后立即讓電機反向運行用戶設定的回零距離作為機械零點;伺服報警信號輸入時,程序立即停止該電機的運動,直到用戶將報警清除。

(2)輸出控制脈沖電路設計。

輸出控制脈沖信號為伺服電機的4路脈沖控制輸出信號。此控制采用“脈沖+方向”指令,由于每個控制軸分別有脈沖和方向信號,所以4路共8個輸出信號。輸出控制脈沖信號由FPGA輸出,要先經過電平轉換,將FPGA的I/O引腳的3.3V變為5V,再經過光電隔離,然后再經過施密特觸發器整形后輸出。由于脈沖和方向信號需要進行差分,所以將信號接入差動線驅動器后再輸出。XPLS~UPLS為脈沖信號,XDIR~UDIR為方向信號。差動線驅動器由AM26LS31構成,該電路的功能是將輸入的單極性的方波信號轉化為一對極性相反的電機驅動信號,它的高阻抗輸出狀態在電源掉電時是有保障的。

(3)反饋脈沖處理電路設計。

伺服電機的編碼器信號直接接入到電機驅動器中,驅動器提供三對差分信號A+、A-、B+、B-、Z+、Z-作為反饋。這三對信號由于受到驅動器內部大電源的干擾,在電機旋轉時,所發出的信號會出現許多毛刺,直接接到FPGA中會引起誤判斷,所以三對信號經過差分電路轉化為單路信號A、B、Z。差分電路由AM26LS32構成,該芯片功能與AM26LS31相反,該電路的功能是將輸入的一對極性相反的編碼器反饋信號轉化為單極性的方波信號。A、B兩路為正交編碼脈沖,Z路每轉產生一個低電平脈沖,用于回零時的精確定位。

2.4 數字量輸入輸出接口模塊

考慮到系統的可擴展性和DSP的GPIO口的數量,此運動控制器在DSP與FPGA上分別設計8路,共16路數字量輸入輸出。運動控制器的所有數字量輸入輸出信號均采用光電隔離處理,并對每一路信號進行相應的數字濾波處理,以消除噪聲信號。數字量輸入通道可以根據用戶的要求自定義用途,用于零點、限位信號的輸入等;數字量輸出通道用于各軸方向、脈沖信號的輸出以及一些外部設備的啟停控制等。

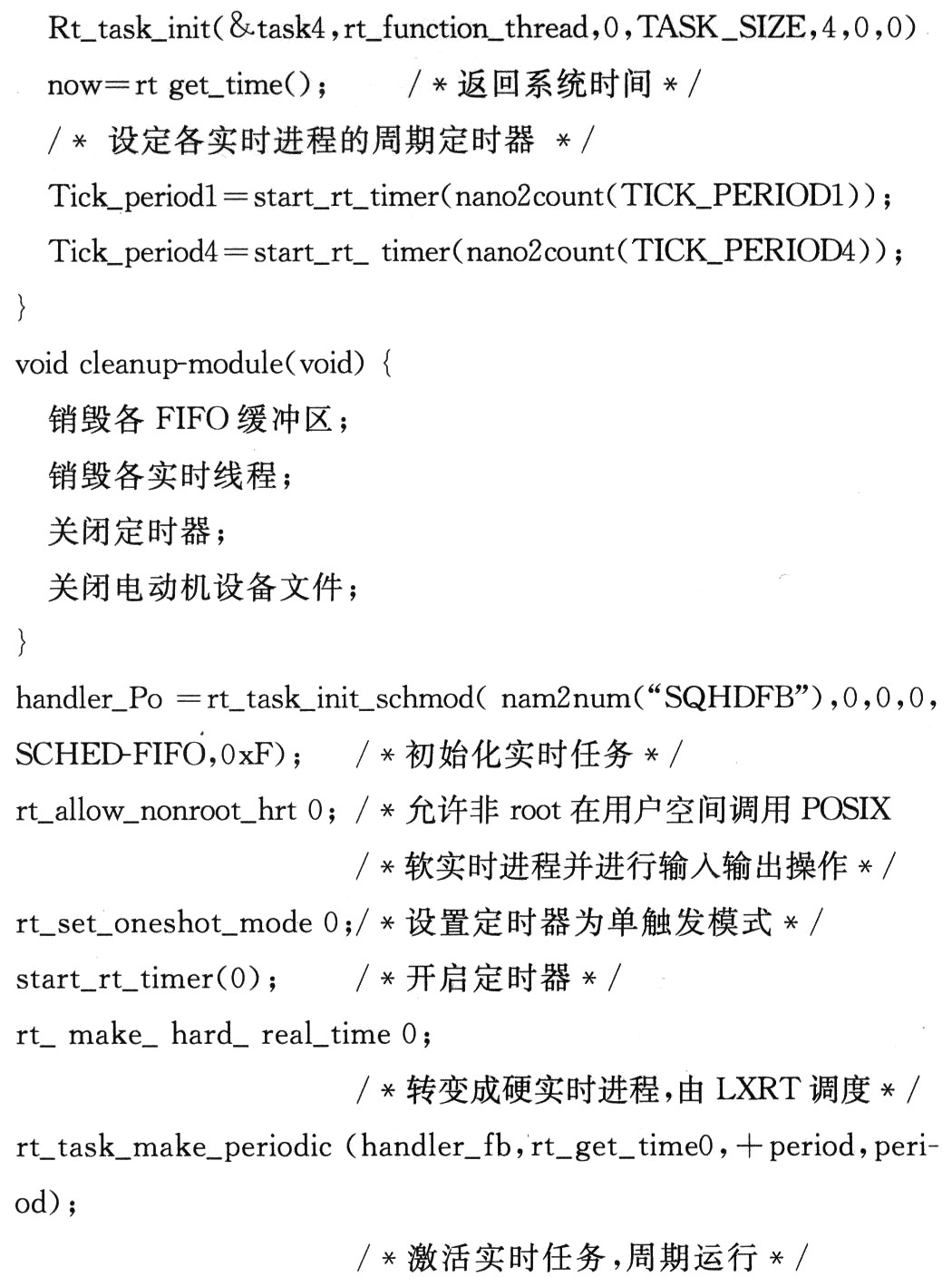

3 系統軟件設計

軟件設計采用模塊化設計方法,程序的總體結構采用以數據管理和位置速度控制為主,以I/O端口控制、邏輯控制、插補運算等為中斷任務或子函數任務的形式。位置速度控制主要負責對實時運動狀態的監控與調節;I/O端口控制主要負責掃描輸入端口、設置輸出端口等輔助性任務。

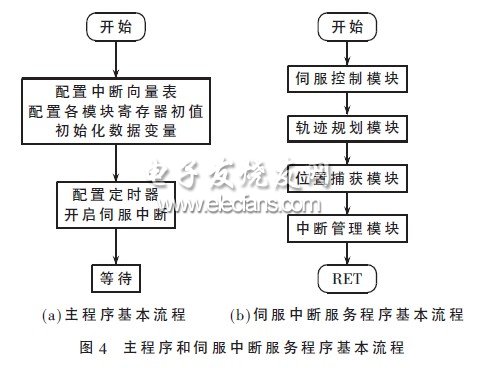

DSP控制程序主要由一個定時中斷構成,主程序啟動后,首先完成對TMS320F2812的初始化及系統的一些基本配置,并處于等待狀態。運動控制功能是在伺服中斷服務程序中實現的。主程序和伺服中斷服務程序基本流程如圖4所示。

?

FPGA主要完成運動控制器的精插補功能,采用數字積分法進行插補。把數字積分法分為3個狀態:

(1)狀態WAIT,等待插補信號;

(2)狀態L1,判斷總的脈沖數;

(3)狀態L2,積分累加器累加一次,如有溢出,相應的輸出脈沖為高電平,剩余累加次數減1。

數字積分法的有限狀態機如圖5所示。

?

觸發條件T1:沒有啟動信號,下一狀態為WAIT,無操作;

觸發條件T2:有啟動信號,下一狀態為L1,操作為初始化各寄存器,置忙信號;

觸發條件T3:剩余累加次數大于0,下一狀態為L2,操作為各軸輸出脈沖為低電平;

觸發條件T4:剩余累加次數為0,下一狀態為WAIT,操作為各軸輸出脈沖為低電平,清忙標志;

無觸發條件:下一狀態為L1。

具體實現方法為:時序電路產生的插補脈沖作為此模塊的累加脈沖,每累加1次,剩余累加次數減1。當剩余累加次數為0時,此次插補過程結束。

4 結語

該運動控制器的結構設計可以模塊化和易于擴展,這樣可以滿足用戶的各種需求。在軟件部分中,采用有限狀態機的插補方法,在插補速度處理環節做了優化,使脈沖輸出更加穩定。

電子發燒友App

電子發燒友App

評論