長期平均誤碼率,簡稱誤碼率(BitErrorRate,BER),是光通信網絡及設備的重要指標之一。目前光通信網絡及設備正朝著小型化、高頻率、高速率、大容量的方向發展,對作為測量儀器的誤碼測試儀速率及功能的要求也越來越高。雖然國內外儀器儀表廠,如安捷倫(Agilent)、泰克(Tektronix)等推出了各種高速誤碼測試儀,但是大多價格昂貴,并且系統復雜。所以,對于國內通信行業,開發一種價廉、方便、速率可達10 Gb/s的高速誤碼測試系統,具有實用價值。

1 系統概述

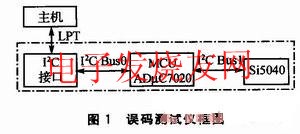

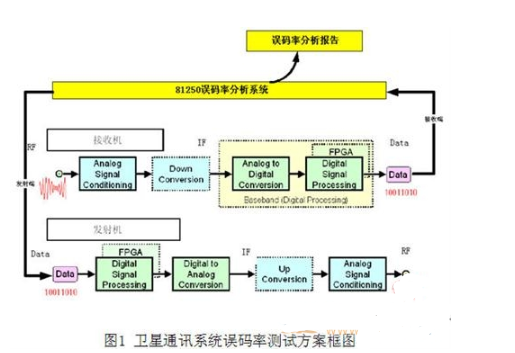

本誤碼測試系統由兩部分組成:誤碼測試部分和上位機人機界面部分。其中誤碼測試部分由高速誤碼儀、光衰減器、光功率計和光源等組成。高速誤碼儀以微控制器ADμC7020為核心,控制XFP收發控制器Si5040來實現。

ADμC7020是ADI公司的基于ARM7TDMI的體系結構的控制器,支持16/32位精簡指令集(RISC)。片內集成了12位的ADC(1MSPS)、4通道12位帶緩沖的DAC、電壓比較器、62 KB可在系統中編程(ISP)的片內閃速/電擦除存儲器Flash和8 KB RAM,串行接口包括UART、SPI、2個I2C、用于下載/調試的JTAG端口、4個定時器、14個通用I/0引腳、片內可編程邏輯陣列(PLA)。CPU時鐘高達45 MHz,可使用片內晶體振蕩器和片內PLL。

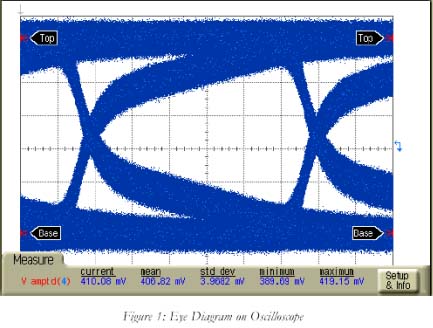

Si5040是Silicon Laboratories公司高速物理層(highspeed PHY)產品線的產品。采用其已通過市場驗證的DSPLL技術,同時在數據發送和接收路徑提供信號抖動消除功能的10 Gb/s XFP收發器。Si5040支持3種不同的模擬與數字信號質量監測功能,分別是模擬信號LOS監測、CID(連O或連1)監測以及專有的數字眼圖開度測量功能,還提供線路環回測試、XFI回路測試和接收/發送雙方向的PRBS碼流生成和檢查功能。

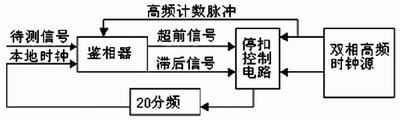

此設計中,ADμC7020作為控制器,對Si5040芯片進行配置和初始化,完成誤碼數的采集,并作為整個系統上位機和Si5040之間的橋梁,及時向上位機提供測量的誤碼及狀態值等數據;Si5040完成偽隨機碼型(PRBS)的產生、同步及對比檢測,計算出誤碼數(Error Count);上位機由LabWindows/CVI構造的測試平臺,通過上位機PC的并口(LPT)模擬I2C總線讀ADμC7020所構建的寄存器映射表,將測試系統各器件的狀態(包括Si5040)及誤碼數顯示出來,計算誤碼數和測試時間內的總發送碼數的比值得出誤碼率(BER),通過I2C總線讀寫ADμC7020的寄存器表完成對系統各部分(包括Si5040)的控制和查詢。

2 原理及組成

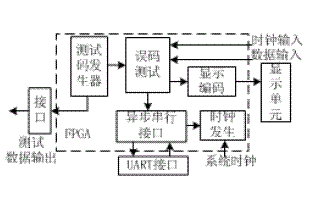

誤碼測試儀框圖如圖1所示。

2.1 測試原理

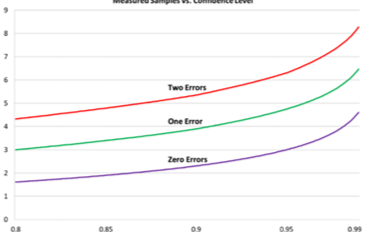

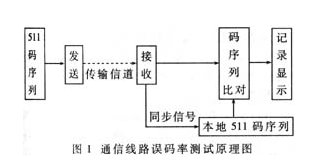

在數字光纖通信系統中,經常測試或驗證系統和器件的誤碼率指標,若要獲得精確的測試結果,必須進行無限長時間的試驗。根據統計置信度原理,只要驗證數字系統或器件的誤碼率指標是否優于某一規定標準,即可在測量精度和測試時間之間進行折中處理,而且仍能保證測試結果的可信度。產生誤碼的主要原因是傳輸系統的噪聲和脈沖抖動,誤碼性能用誤比特率BER來衡量。但在實際測量中,常以長時間測量中誤碼數目與傳送的總碼元數之比來表示BER,BER=錯誤比特數/傳輸總的比特數。

由于這是一個統計過程,因此當被測比特數接近于無窮大時,被測BER才能接近實際BER。但是在大多數情況下,只需測試小于預定義閾值的BER即可。完成測試所需的比特數取決于所需的置信度和BER閾值。置信度是指,系統的真實BER小于指定BER時的測試占全部測試的百分比。由于無法測量無窮位,也無法準確預測什么時候會出現誤碼,因此置信度永遠不會達到100%。另外,IEEE802.3規定最壞情況的誤碼率是10E-10。在這種條件下,出現的誤碼不會降低網絡的性能,因為所有的網絡軟硬件都按這個要求建立。因此,這個條件下出現的噪聲將不足以改變接收端的比特值,不會造成誤碼。一般情況下,選擇的誤碼率標準比IEEE標準高出100倍,并把10E-12誤碼率稱為零誤碼率。零誤碼率意味著每10萬億位中產生的誤碼小于1個。置信度的公式如下:

其中CL為置信度,Nbits為接收的總比特數。

在生產和測試中,只考慮零誤碼且置信度為標準的95%的情況,用比特數除以數據速率可確定測試所需時間。得出常用的方程式如下:

對于10 Gbps的系統,測試30 s基本可以達到10E-12的要求。

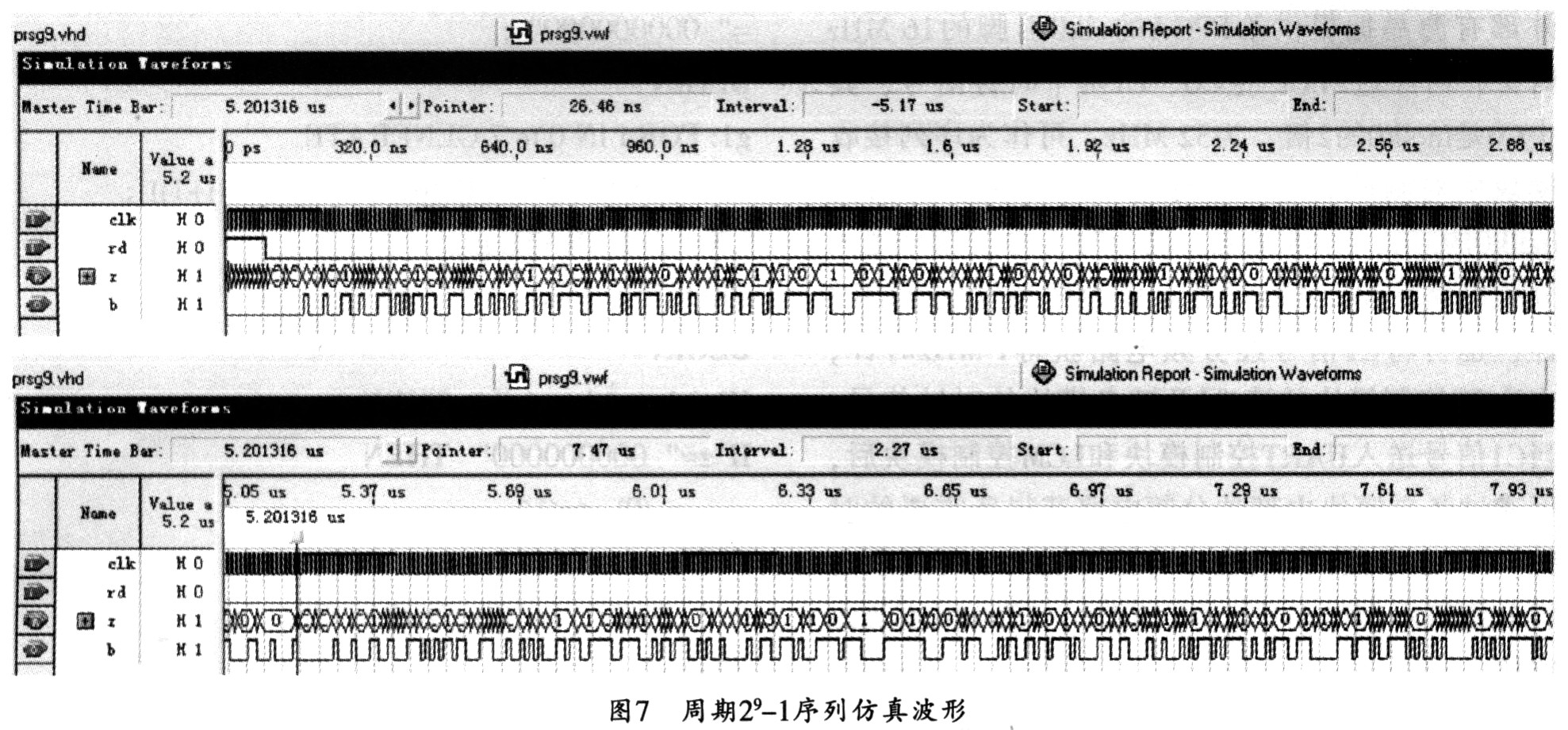

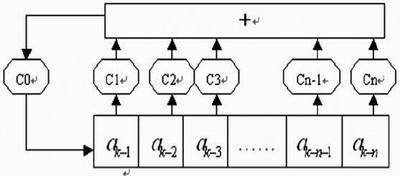

Si5040的發端模塊產生偽隨機碼序列數據流,作為通信系統的信源數據流,收端模塊接收通信系統輸出的比特流,并與本地產生的與發端形式相同的偽隨機碼比特流相比較,如比較結果不同即系統有誤碼。Si5040在收端和發端信道上都有可編程的模式生成器和檢查器。發端信道通過配置寄存器(tpSel Register 157),收端信道通過配置寄存器(RxtpSel Register 29),可以生成PRBS7、PRBS31或者64位用戶自定義碼型。模式檢查器還提供了不同步信號(Loss-of-Sync)檢查。在同步情況下,測試中發端的誤碼值結果存于Si5040中40位的寄存器組(tp-ChkErrCnt registerl76-180)和一個8位浮點數的寄存器(tpChkErr register 181)。收端的誤碼值結果存于40位寄存器組(RxtpChkErrCntRe-gister48-52)或8位浮點數據類型的寄存器(RxtpChkErr Register 53)。本設計僅使用Si5040的發端信號的模式生成器和檢查器功能。

2.2 硬件設計

本文硬件設計僅列出Si5040和ADμC7020兩部分的原理圖。

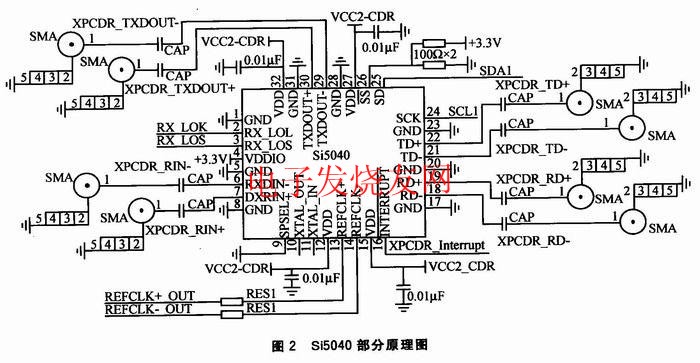

2.2.1 Si5040

Si5040的PINl3和PINl4是參考時鐘輸入引腳。在此設計應用中使用Silicon Laboratories公司的SI534四頻晶體振蕩器(XO),其工作頻率范圍10 MHz~1.4 GHz,RMS抖動低于O.3 ps,可提供高線性度的控制電壓及寬范圍的電壓增益選擇,并可以支持PECL、LVDS、CMOS和CML各種電平形式的輸出。

Si5040的通信接口支持I2C和類SPI模式。通過SPSEL(PIN9)來選擇使用接口的類型。當SPSEL置低電平時,使用I2C接口類型,PIN25(ser-ial data line,SD)and PIN24(serial clock input,SCK)作為I2C總線的SDA和SCL。當SPSEL置高電平時,使用類SPI接口類型。

Si5040在發端和收端都有可編程的碼型模式生成器和檢查器。發端信道使用TxtpSel寄存器,可配置成PRBS7、PRBS31或者64位用戶自定義碼型。

Interrupt、RX_LOL和Rx_LOS反映Si5040的工作狀態。由ADμC7020的I/O口來采樣其電平邏輯,由此反映Si5040的工作狀態。

TD+、TD-、TXDOUT+、TXDOUT-和RD+、RD-、RXDIN+、RXDIN-接入SMA頭,信號為差分CML信號。

Si5040原理圖如圖2所示。

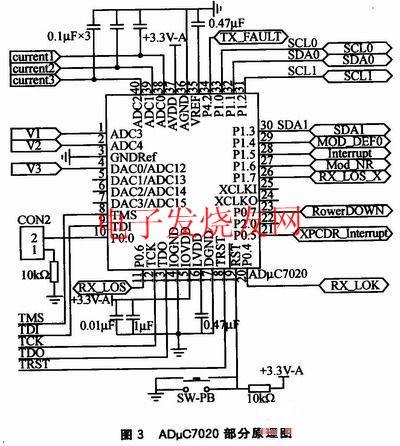

2.2.2 ADμC7020

使用JTAG仿真調試ADμC7020,其引腳為TMS、TDI、TCK、TD0、TRST。

使用ADμC7020的兩個I2C接口。P1.1和P1.2構成I2C總線O,ADμC7020作為I2C從機。上位機PC作為I2C主機。P1.3和P1.4構成I2總線1,ADμC7020作為I2C主機,Si5040作為I2C從機。

P0.6、P0.4和P0.5引腳作為輸入腳測試Si5040的狀態RX LOS、RX LOK和Interrupt。

P1.4、P1.5、P1.6、P1.7和P4.2引腳控制測試待測XFP模塊的各種狀態。

ADC0、ADC1和ADC2測量誤碼測試系統中有關電壓值+5 V、+3.3 V和+1.8 V的各電壓通道上的總電流值。

ADC3、ADC4和ADC12測量誤碼測試系統中XFP模塊的電壓值+5 V、+3.3 V和+1.8 V。

跳線接地時即P0.0接地,同時Flash 0x14地址的內容為0xFFFFFFFF時,在兩個條件同時滿足時,在ADμC7020復位時可自動進入Bootlo-ader程序(即在系統中編程ISP),這樣可以不使用JTAG仿真器,以方便誤碼測試儀的ADμC7020的Firmware在線升級換代。

ADμC7020部分原理圖如圖3所示。

3 FIRMWARE設計

①當ADμC7020作為I2C從機時,構建一個I2C訪問的寄存器映射表(Memory Map)。共有2個頁面,每個頁面256個寄存器。其中頁面0有待測XFP模塊和Si5040的狀態顯示、控制、上電初始化值、儀器接口初始化等寄存器。頁面1為Si5040的映射寄存器,其將Si5040內部全部的184個寄存器全部映射到本頁,測試人員可以通過該頁的寄存器對應訪問Si5040的相關寄存器,每個頁面的最后一個寄存器是頁面選擇寄存器。

②收到上位機命令,解釋上位機命令并完成測試或控制待測模塊和Si5040功能。

③設置Si5040循環控制定時器值為100 ms,即每100 ms檢測待測模塊的狀態和Si5040的寄存器值,并映射到構建的相關寄存器中。

④設置ADC采樣TIMER也為100 ms,即每100 ms通過ADC采樣測量相應的電壓值和電流值。并將值映射到構建的相關寄存器中,供上位機查詢。

⑤上電初始化Si5040相關測試誤碼寄存器。在上電復位時,ADμC7020按照其寄存器映射表的初始值配置Si5040。修改初始配置表可以改變Si5040的上電寄存器設置。在上電初始化完成后,通過I2C接口修改Tablel的Si5040映射寄存器值,也可以改變Si5040的相關寄存器的配置。

4 上位機及人機界面

4.1 人機界面

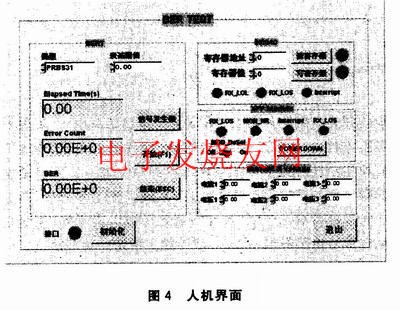

Lab Windows/CVI所設計的人機界面如圖4所示,左部為誤碼率測試,右部為寄存器狀態及控制。在測試前,通過串口讀光功率計和衰減器的值,根據生產和測試要求配置衰減器衰減量,在完成整個測試平臺的配置并選擇測試時的偽隨機碼列后,按下“開始”按鍵,可以開始測試。在Elapsed Time(s)、Error Count和BER三個顯示框中分別顯示測試時間、誤碼個數及誤碼率。“信號發生器”按鍵為使用Si5040配置TX信道的端口信號,不讀Si5040的誤碼個數,不計算RFR值。

4.2 底層驅動

控制上位機PC的并口,按I2C協議產生相應的I2C讀寫時序。上位機PC的并口DB25由3個寄存器組成:數據寄存器(Data Register)、狀態寄存器(Status Register)和控制寄存器(Control Register),在SPP(Standard Parallel Port)模式,即標準并口模式下,地址為:數據寄存器(0x378)、狀態寄存器(0x379)、控制寄存器(0x37a)。通過數據寄存器的數據輸出和狀態寄存器數據的讀入,控制SCL和SDA總線以及讀SCL和SDA的狀態,可以方便地產生I2C時序中的START、STOP、ACK、NACK等基本的時序,通過這些基本時序生成了完整的I2C讀寫的時序。

5 實驗

在碼型中可選擇PRBS7、PRBS31或64位用戶自定義碼型,針對XFP光模塊一般選擇PRBS31碼型,置信度為95%,短時間測量采用30 s,長時間測量采用3000 s。對比實驗采用Agilent 86100 Infinite DAC和Agilent70843B 12 Gb/s誤碼測試儀搭建的誤碼測試系統。結果顯示,在測量時間內兩系統測試的誤碼個數相近,而且誤碼率測試結果達到10E-12。

結語

本系統充分利用了ADμC7020強大功能及Si5040的誤碼檢測功能,結合虛擬儀器特點,構造了一種誤碼測試系統。對于大多數光收發模塊生產廠家,其對XFP模塊生產及測試線有一定的量及周期要求,本系統以其體積小、系統搭建簡便、靈活性強、成本低的特點,可以代替部分國內外高速誤碼測試儀。與進口誤碼測試儀的對比測量,充分證明了這點。另外,本測試系統可利用ADμC7020的強大Bootloader程序,完成Firmware升級,實現在系統編程,同時整套系統硬件稍加以改進就可以應用于XFP模塊的靈敏度測試。

電子發燒友App

電子發燒友App

評論