摘 要: 本論文提出一種基于TMS320C6701 DSP實現HDTV信源解碼器的方案。用C6701實現系統控制、解復用、AC-3音頻解碼,用STi7000視頻解碼。與現有的HDTV信源解碼方案相比,本方案將核心芯片由三片(系統控制+解復用、視頻解碼和音頻解碼)減少到兩片,有利于系統集成,代表了HDTV信源解碼器的發展方向之一。

引言

數字高清晰度電視(HDTV)是繼黑白電視和彩色電視之后的新一代電視,HDTV接收機或機頂盒具有廣闊市場和巨大經濟效益,已經成為國際高科技領域研究開發的熱點之一。

HDTV接收系統由信道解碼、信源解碼、顯示終端組成。目前,多數HDTV信源解碼方案均由三片或三片以上的核心芯片組成,分別用于系統控制+解復用、視頻解碼、音頻解碼。為了提高系統的集成度,信源解碼方案正向著兩片方案過渡,最終可能實現單片解碼方案。本文提出一種兩片解碼方案:用TI的TMS320C6701完成系統控制、解復用、音頻解碼;用STi7000完成視頻解碼。

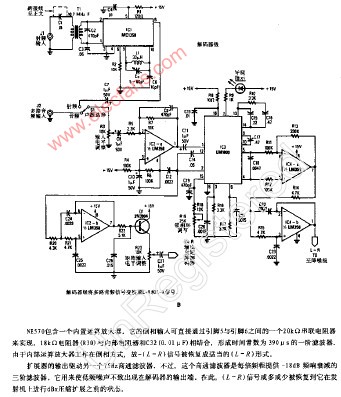

圖1 信源解碼器硬件框圖

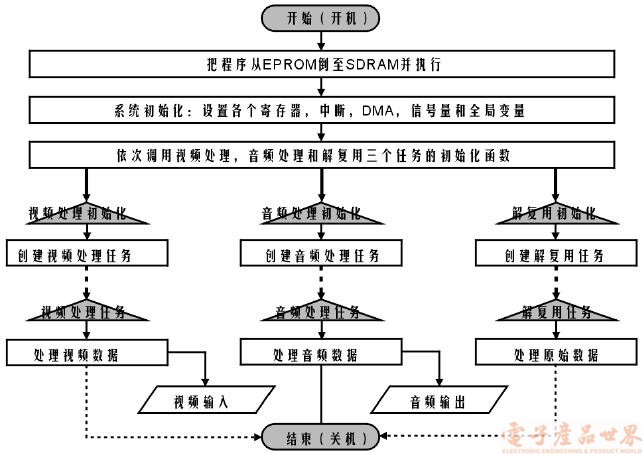

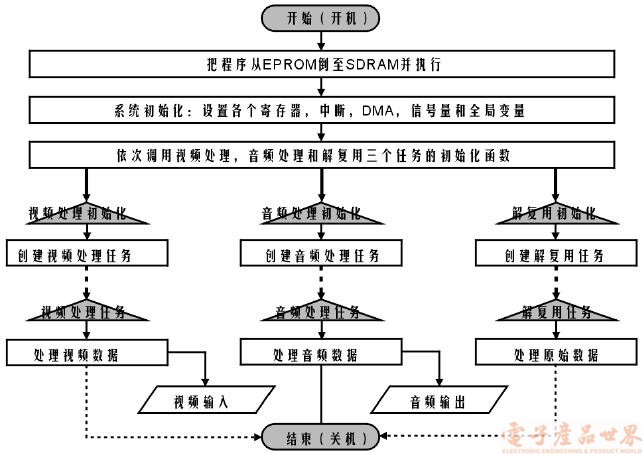

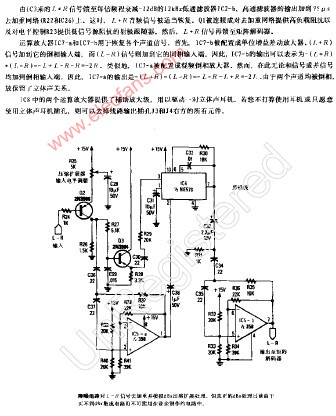

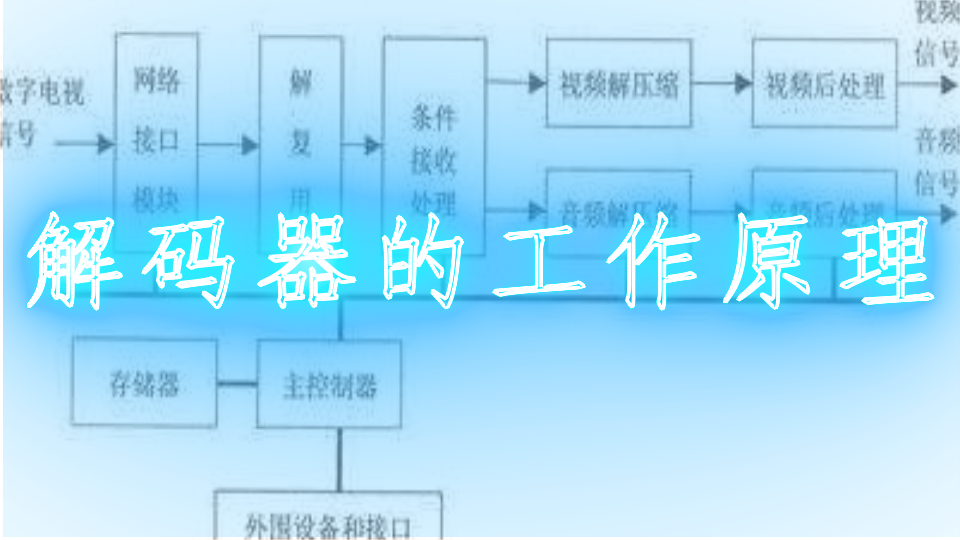

圖2 信源解碼器軟件結構框圖

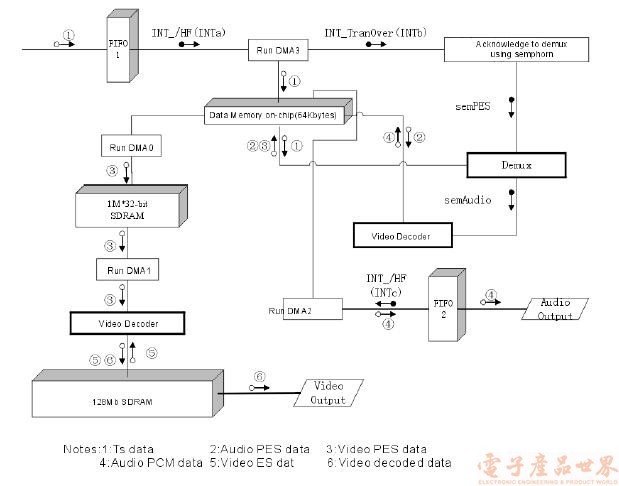

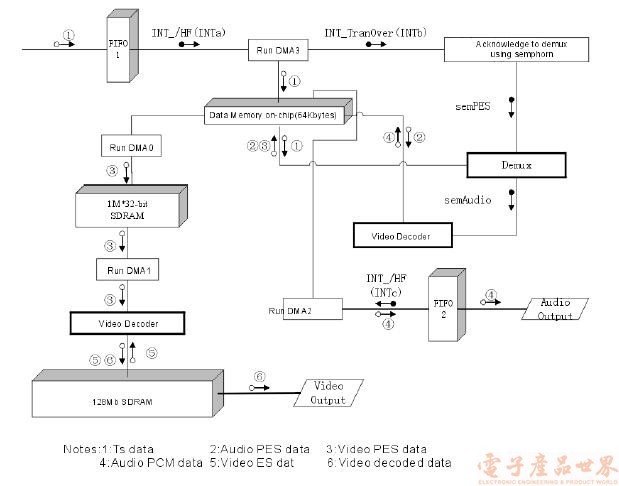

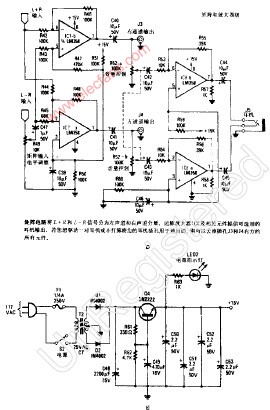

圖3 軟件解碼數據流圖

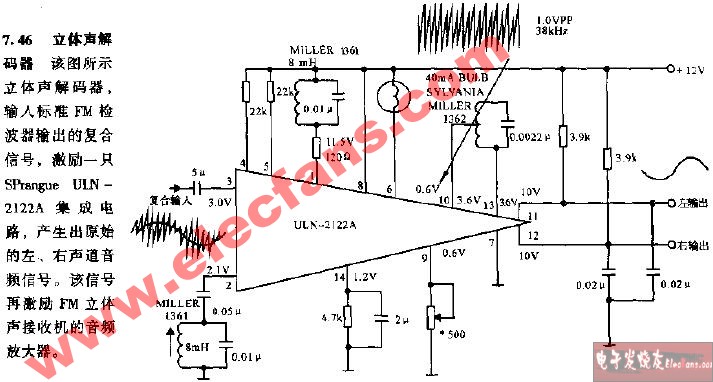

硬件設計

本信源解碼方案的硬件設計如圖1所示。

系統的核心為TMS320C6701 DSP,采用EPROM固化系統程序。C6701配接SDRAM用來存儲數據和工作程序。FIFO1用來輸入TS。視頻解碼器STi7000映射到C6701存儲空間。STi7000配有SDRAM用來存儲視頻PES、各種圖像(解碼、參考和顯示幀圖像)及OSD數據。視頻后處理部分由THS8134 DAC、CPLD及運放組成。系統本地時鐘和PWM產生器由FPGA實現,它與VCXO、RC低通濾波器一起在C6701解復用軟件配合下完成27MHz時鐘恢復。音頻解碼由C6701軟件完成。音頻輸出部分由FIFO2、一個 74LS157和三個D/A芯片組成。音頻輸出所用時鐘和控制信號也由FPGA實現。

系統控制、解復用和音頻解碼

C6701是TI的高性能浮點DSP,時鐘為167MHz,具有1336MIPS能力。C6701的Memory Map選為Map0。在其存儲器的 CE0 空間中放置了1M*32位的SDRAM。在CE1空間放置了1M*16位EPROM。本系統使用ROM boot process,因此C6701的BOOTMODE[4:0] 引腳置為“10010”。C6701的程序超過64K字節,因此從0地址開始執行的是一個Loader,它把EPROM中其他程序繼續傳送到SDRAM中。傳送完成后,CPU開始從Loader以下的地址開始執行程序。CE2空間用來放置異步器件,此時它的大小為4Mbytes。它被GAL內部的譯碼器等分為四個部分。前兩個部分放置STi7000;第三部分放置FIFO1;第四部分放置實現本地時鐘和PWM的FPGA。CE3空間僅放置FIFO2。

C6701 PLL模式被選為 *4 , 即輸入引腳CLKMODE[1:0] = 11b。41.75MHz由5V晶體振蕩器產生,經過LVT125做電平變換后輸入給C6701。C6701的SDCLK輸出加給零延遲時鐘緩沖器CY2308后分兩路分別提供給SDRAM。C6701所用的3.3V(VCC3)和1.9V(VCC1.9)由PT6921產生。本系統有一個 14腳插座, 它可與XDS510 emulator(硬件仿真器)連接起來實現仿真。C6701的HPI和串口1不被使用,相應引腳與跳線連接,以便系統功能擴展時使用。

本系統輸入為并行TS,輸入接口由TS數據(TSData[7:0]),DVALID,BCLK and ERROR組成。當TS數據輸入達到2KB時,FIFO的/HF信號有效,它作為一個中斷信號加給C6701 INT6腳。接到此中斷后,C6701運行有關中斷子程序,DMA將2KB TS數據取出傳輸到C6701片內的SRAM中。該FIFO映射到C6701 EMIF CE2空間。

27MHz系統時鐘恢復由FPGA(EPF10K20)中的計數器/PWM模塊、外部低通濾波器和VCXO在C6701相應軟件的控制下完成。VCXO輸出的時鐘信號輸入給FPGA中的一個42位計數器產生本地時鐘LMCR。當C6701按一定算法求得PCR與本地時鐘的差值后,將此差值輸出給FPGA的PWM模塊,該模塊將此差值轉換為PWM信號后輸出給低通濾波器,取出直流后控制VCXO輸出頻率。經一定時間的調整后,得到與發射方同步的27MHz。VCXO輸出的27MHz時鐘也提供給視頻解碼器使用。

視頻解碼

視頻解碼由ST公司的STi7000在C6701的相應軟件控制下實現。STi7000完成如下功能:a)接收C6701傳來的視頻PES并進行句法分析,取出ES存入SDRAM,取出DTS、PTS存入相應寄存器。b)找到ES中各層的開始碼并提取頭部信息,存入相應寄存器中,發中斷給C6701。C6701讀取這些頭部信息,并據此控制解碼流水線工作。c)STi7000的核心是硬件SLICE層以下解碼流水線。它從SDRAM中讀出ES,進行解壓縮(VLD-反掃描-IDCT-運動補償)得到重構圖像,并根據其類型(I、B或P幀)存入SDRAM相應區內。在流水線開始每一幀圖像解碼前,C6701要根據該幀類型等參數向STi7000發解碼命令。解碼流水線另一個重要功能是實現隱錯。d)視頻格式轉換:圖像輸出前,可進行各種格式變換(水平分辨率上下變換;垂直行數上下變換;隔行(I)和逐行(P)相互變換;3:2電影下拉模式和幅型比(4:3或16:9)變換(FULL、ZOOM、LETTERBOX和SIDEBAR)。e)實現OSD功能。

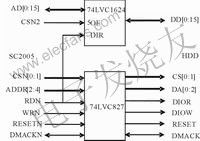

STi7000約有110個寄存器,分為配置、控制、存儲器存取、解碼指令、顯示、OSD、時鐘/鎖相環、D1接口、PES等9類。 C6701對STi7000各寄存器的存取通過STi7000的8位微控制器接口進行。該接口映射入C6701 EMIF CE2空間最低1MB內。其8位數據線接到LVT16245一邊;8位地址線接LVT16244輸出邊;片選(notA_cs)接GAL相應的輸出,讀寫(A_RnotW)接LVT16244輸出/B_AWE上。中斷請求信號(notA_IRQ)接C6701 INT4腳。C6701通過STi7000的8位并行數據接口向STi7000寫入視頻壓縮數據。該接口與上述8位微處理器接口共用8位數據線。壓縮數據請求信號接C6701 INT5腳。壓縮數據選通輸入notA_STRB則由GAL提供。

STi7000需要128Mbit的SDRAM存儲器,由兩片4*512K*32-Bit的100MHz SDRAM芯片組成。STi7000要求SDRAM具有如下特點:全頁Burst長度;連續Wrap;3周期CAS Latency。SDRAM和STi7000實現“glueless(無膠合)”連接。

本系統采用TI的THS8134實現視頻輸出D/A變換。本系統只實現HD輸出方式。STi7000的24Bit Y、Cb、Cr數字視頻信號和PIXCLK直接輸出給THS8134,產生模擬Y、Pb、Pr分量信號。STi7000的PIXCLK、HSYNC和VSYNC信號加給一個CPLD(EPM7128)。該CPLD控制THS8134按照相應的標準(1080I格式對應SMPTE274M;720P格式對應SMPTE296M;480P格式對應SMPTE293M;480I格式對應SMPTE170M)分別在Y、Pb、Pr分量上疊加三電平(1080I和720P)或兩電平(480P)復合同步信號,然后經運算放大器放大后輸出。這四種格式由C6701 TOUT0和TOUT1輸出的Displaymode0和1選擇。

當音頻開始輸出時,C6701先將4KB數據寫入FIFO2中。FIFO2映射入C6701 EMIF CE3空間。FIFO2的滿標志/FF信號有效,它觸發FPGA內相應模塊開始工作,將音頻主時鐘12.2880MHz時鐘分頻產生LRCLK(左右時鐘信號,頻率48KHz)和SCLK(串行時鐘,頻率為3.072MHz)。SCLK信號作為FIFO2的讀信號,而LRCLK則作為74LS157的輸入選擇信號。當LRCLK為高電平時,左(左環、中央聲道)數據輸出給三個DAC芯片;當LRCLK為低電平時,右(右環、LFE)數據輸出給三個DAC芯片。MCLK、LRCLK和SCLK同時輸入給三個DAC芯片。由三個DAC輸出的5.1聲道經放大后分別輸出。當FIFO2中已輸出2KB數據時,其/HF無效,此信號接至C6701 INT7輸入腳,觸發該中斷。C6701執行相應的中斷子程序,再向FIFO2輸出2KB數據,如此循環,保證音頻信號持續輸出。

軟件設計

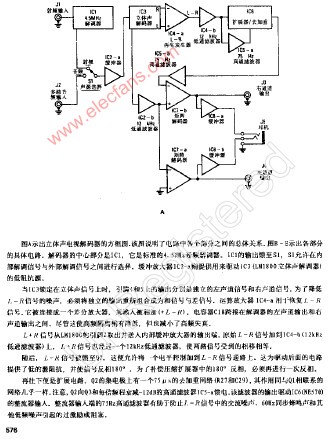

系統的軟件結構如圖2所示。

在C6701內部有64Kbytes的數據SRAM和64Kbytes的Cache/Program SRAM。程序SRAM經初始化用作Cache。64K字節的片內數據RAM被組織成兩個塊。它們的地址分別為8000 0000h到8000 7FFFh和8000 8000h到8000 FFFFh。當CPU的Side A和Side B或者DMA控制器同時使用不同塊時,不會引起沖突。因此,同時訪問的數據位于不同塊時,不需考慮它們的地址。整個片內數據RAM分為五個部分:TS_Buffer(4K字節)用來緩沖輸入的TS;V_PES_Buffer(16K字節)用來存放視頻PES; A_PES_Buffer(8K字節) 用來存放音頻PES/ES; A_Buffer(32K字節) 用來存放解壓縮后的音頻數據;剩余的部分用于緩存中間計。

算數據。每一部分Buffer又分成兩個塊,以乒乓方式使用。即一塊由CPU使用時,另一塊可以同時進行存貯或由DMA使用。

軟件整個系統解碼數據流圖如圖3所示。首先FIFO1接收到的TS數據到其存儲量的一半(2KB),發出中斷(INTa)激活DMA3。DMA3把FIFO1里一半的數據倒到C6701的片內存儲器TS_Buffer中,并在傳輸完成時發出中斷(INTb),INTb的中斷服務程序發出信號semPES激活解復用任務。解復用任務從片內存儲器中取出TS數據進行相應處理,然后把分離出的音視頻PES數據送回片內存儲器,當A_PES_Buffer填充一半時,通過信號量semAudio激活音頻處理任務。音頻處理任務從A_PES_Buffer中取出音頻PES數據,解碼后存到A_Buffer。當A_Buffer中的數據積累到一定數量時,激活DMA2。DMA2把解碼后的4KB音頻數據輸出給FIFO2,FIFO2的/FF信號(滿標志)啟動音

頻數據由FIFO2的讀出。音頻輸出FIFO2半空時會發出中斷INTc,激活DMA2。DMA2把A_Buffer中的數據再傳送2KB到FIFO2去,如此繼續下去。視頻PES數據由DMA0從V_PES_Buffer不斷地倒到片外SDRAM中,當接到STi7000請求時,激活DMA1,把SDRAM中緩存的的視頻PES數據輸出給STi7000,進行解碼,然后,經視頻后處理后輸出給顯示器。

解復用的功能包括:PSI分析,時鐘恢復以及對傳輸包拆包并傳給相應的buffer(緩存器)。

視頻解碼的功能是對視頻PES進行解壓縮,恢復出視頻流。在系統中,Video Driver的中斷的優先級被設為最高。視頻解碼系統主要是通過中斷來觸發其它過程的進行,中斷是視頻解碼主線,操縱著整個視頻解碼的過程。

音頻解碼的功能是對音頻PES進行AC-3解壓縮,恢復出音頻流。音頻解碼從音頻PES包解碼開始,在6701片內的數據存儲區中開辟A_PES_Buffer(由兩塊各4KB對稱的存儲區組成),解復用得到的音頻PES數據以乒乓方式存儲到這兩個區域。經過拆包PES數據得到的ES數據直接覆蓋PES數據所處區域。然后開始音頻解碼的核心計算,將解碼輸出的PCM數據格式化后存儲到片內數據存儲區中開辟的兩塊(各16K)PCM緩沖區中,利用DMA2將其中的數據輸出給片外的FIFO。

結語

本論文提出了一種基于通用DSP C6701的HDTV信源解碼器兩片解決方案。隨著技術的進步,將來可能會提出HDTV信源解碼器單片解決方案。即在單個功能強大的芯片的基礎上,很多工作可以由軟件控制實現。本論文提出的HDTV信源解碼器解決方案對于下一代HDTV信源解碼器的研制具有重要的參考價值。

引言

數字高清晰度電視(HDTV)是繼黑白電視和彩色電視之后的新一代電視,HDTV接收機或機頂盒具有廣闊市場和巨大經濟效益,已經成為國際高科技領域研究開發的熱點之一。

HDTV接收系統由信道解碼、信源解碼、顯示終端組成。目前,多數HDTV信源解碼方案均由三片或三片以上的核心芯片組成,分別用于系統控制+解復用、視頻解碼、音頻解碼。為了提高系統的集成度,信源解碼方案正向著兩片方案過渡,最終可能實現單片解碼方案。本文提出一種兩片解碼方案:用TI的TMS320C6701完成系統控制、解復用、音頻解碼;用STi7000完成視頻解碼。

圖1 信源解碼器硬件框圖

圖2 信源解碼器軟件結構框圖

圖3 軟件解碼數據流圖

硬件設計

本信源解碼方案的硬件設計如圖1所示。

系統的核心為TMS320C6701 DSP,采用EPROM固化系統程序。C6701配接SDRAM用來存儲數據和工作程序。FIFO1用來輸入TS。視頻解碼器STi7000映射到C6701存儲空間。STi7000配有SDRAM用來存儲視頻PES、各種圖像(解碼、參考和顯示幀圖像)及OSD數據。視頻后處理部分由THS8134 DAC、CPLD及運放組成。系統本地時鐘和PWM產生器由FPGA實現,它與VCXO、RC低通濾波器一起在C6701解復用軟件配合下完成27MHz時鐘恢復。音頻解碼由C6701軟件完成。音頻輸出部分由FIFO2、一個 74LS157和三個D/A芯片組成。音頻輸出所用時鐘和控制信號也由FPGA實現。

系統控制、解復用和音頻解碼

C6701是TI的高性能浮點DSP,時鐘為167MHz,具有1336MIPS能力。C6701的Memory Map選為Map0。在其存儲器的 CE0 空間中放置了1M*32位的SDRAM。在CE1空間放置了1M*16位EPROM。本系統使用ROM boot process,因此C6701的BOOTMODE[4:0] 引腳置為“10010”。C6701的程序超過64K字節,因此從0地址開始執行的是一個Loader,它把EPROM中其他程序繼續傳送到SDRAM中。傳送完成后,CPU開始從Loader以下的地址開始執行程序。CE2空間用來放置異步器件,此時它的大小為4Mbytes。它被GAL內部的譯碼器等分為四個部分。前兩個部分放置STi7000;第三部分放置FIFO1;第四部分放置實現本地時鐘和PWM的FPGA。CE3空間僅放置FIFO2。

C6701 PLL模式被選為 *4 , 即輸入引腳CLKMODE[1:0] = 11b。41.75MHz由5V晶體振蕩器產生,經過LVT125做電平變換后輸入給C6701。C6701的SDCLK輸出加給零延遲時鐘緩沖器CY2308后分兩路分別提供給SDRAM。C6701所用的3.3V(VCC3)和1.9V(VCC1.9)由PT6921產生。本系統有一個 14腳插座, 它可與XDS510 emulator(硬件仿真器)連接起來實現仿真。C6701的HPI和串口1不被使用,相應引腳與跳線連接,以便系統功能擴展時使用。

本系統輸入為并行TS,輸入接口由TS數據(TSData[7:0]),DVALID,BCLK and ERROR組成。當TS數據輸入達到2KB時,FIFO的/HF信號有效,它作為一個中斷信號加給C6701 INT6腳。接到此中斷后,C6701運行有關中斷子程序,DMA將2KB TS數據取出傳輸到C6701片內的SRAM中。該FIFO映射到C6701 EMIF CE2空間。

27MHz系統時鐘恢復由FPGA(EPF10K20)中的計數器/PWM模塊、外部低通濾波器和VCXO在C6701相應軟件的控制下完成。VCXO輸出的時鐘信號輸入給FPGA中的一個42位計數器產生本地時鐘LMCR。當C6701按一定算法求得PCR與本地時鐘的差值后,將此差值輸出給FPGA的PWM模塊,該模塊將此差值轉換為PWM信號后輸出給低通濾波器,取出直流后控制VCXO輸出頻率。經一定時間的調整后,得到與發射方同步的27MHz。VCXO輸出的27MHz時鐘也提供給視頻解碼器使用。

視頻解碼

視頻解碼由ST公司的STi7000在C6701的相應軟件控制下實現。STi7000完成如下功能:a)接收C6701傳來的視頻PES并進行句法分析,取出ES存入SDRAM,取出DTS、PTS存入相應寄存器。b)找到ES中各層的開始碼并提取頭部信息,存入相應寄存器中,發中斷給C6701。C6701讀取這些頭部信息,并據此控制解碼流水線工作。c)STi7000的核心是硬件SLICE層以下解碼流水線。它從SDRAM中讀出ES,進行解壓縮(VLD-反掃描-IDCT-運動補償)得到重構圖像,并根據其類型(I、B或P幀)存入SDRAM相應區內。在流水線開始每一幀圖像解碼前,C6701要根據該幀類型等參數向STi7000發解碼命令。解碼流水線另一個重要功能是實現隱錯。d)視頻格式轉換:圖像輸出前,可進行各種格式變換(水平分辨率上下變換;垂直行數上下變換;隔行(I)和逐行(P)相互變換;3:2電影下拉模式和幅型比(4:3或16:9)變換(FULL、ZOOM、LETTERBOX和SIDEBAR)。e)實現OSD功能。

STi7000約有110個寄存器,分為配置、控制、存儲器存取、解碼指令、顯示、OSD、時鐘/鎖相環、D1接口、PES等9類。 C6701對STi7000各寄存器的存取通過STi7000的8位微控制器接口進行。該接口映射入C6701 EMIF CE2空間最低1MB內。其8位數據線接到LVT16245一邊;8位地址線接LVT16244輸出邊;片選(notA_cs)接GAL相應的輸出,讀寫(A_RnotW)接LVT16244輸出/B_AWE上。中斷請求信號(notA_IRQ)接C6701 INT4腳。C6701通過STi7000的8位并行數據接口向STi7000寫入視頻壓縮數據。該接口與上述8位微處理器接口共用8位數據線。壓縮數據請求信號接C6701 INT5腳。壓縮數據選通輸入notA_STRB則由GAL提供。

STi7000需要128Mbit的SDRAM存儲器,由兩片4*512K*32-Bit的100MHz SDRAM芯片組成。STi7000要求SDRAM具有如下特點:全頁Burst長度;連續Wrap;3周期CAS Latency。SDRAM和STi7000實現“glueless(無膠合)”連接。

本系統采用TI的THS8134實現視頻輸出D/A變換。本系統只實現HD輸出方式。STi7000的24Bit Y、Cb、Cr數字視頻信號和PIXCLK直接輸出給THS8134,產生模擬Y、Pb、Pr分量信號。STi7000的PIXCLK、HSYNC和VSYNC信號加給一個CPLD(EPM7128)。該CPLD控制THS8134按照相應的標準(1080I格式對應SMPTE274M;720P格式對應SMPTE296M;480P格式對應SMPTE293M;480I格式對應SMPTE170M)分別在Y、Pb、Pr分量上疊加三電平(1080I和720P)或兩電平(480P)復合同步信號,然后經運算放大器放大后輸出。這四種格式由C6701 TOUT0和TOUT1輸出的Displaymode0和1選擇。

當音頻開始輸出時,C6701先將4KB數據寫入FIFO2中。FIFO2映射入C6701 EMIF CE3空間。FIFO2的滿標志/FF信號有效,它觸發FPGA內相應模塊開始工作,將音頻主時鐘12.2880MHz時鐘分頻產生LRCLK(左右時鐘信號,頻率48KHz)和SCLK(串行時鐘,頻率為3.072MHz)。SCLK信號作為FIFO2的讀信號,而LRCLK則作為74LS157的輸入選擇信號。當LRCLK為高電平時,左(左環、中央聲道)數據輸出給三個DAC芯片;當LRCLK為低電平時,右(右環、LFE)數據輸出給三個DAC芯片。MCLK、LRCLK和SCLK同時輸入給三個DAC芯片。由三個DAC輸出的5.1聲道經放大后分別輸出。當FIFO2中已輸出2KB數據時,其/HF無效,此信號接至C6701 INT7輸入腳,觸發該中斷。C6701執行相應的中斷子程序,再向FIFO2輸出2KB數據,如此循環,保證音頻信號持續輸出。

軟件設計

系統的軟件結構如圖2所示。

在C6701內部有64Kbytes的數據SRAM和64Kbytes的Cache/Program SRAM。程序SRAM經初始化用作Cache。64K字節的片內數據RAM被組織成兩個塊。它們的地址分別為8000 0000h到8000 7FFFh和8000 8000h到8000 FFFFh。當CPU的Side A和Side B或者DMA控制器同時使用不同塊時,不會引起沖突。因此,同時訪問的數據位于不同塊時,不需考慮它們的地址。整個片內數據RAM分為五個部分:TS_Buffer(4K字節)用來緩沖輸入的TS;V_PES_Buffer(16K字節)用來存放視頻PES; A_PES_Buffer(8K字節) 用來存放音頻PES/ES; A_Buffer(32K字節) 用來存放解壓縮后的音頻數據;剩余的部分用于緩存中間計。

算數據。每一部分Buffer又分成兩個塊,以乒乓方式使用。即一塊由CPU使用時,另一塊可以同時進行存貯或由DMA使用。

軟件整個系統解碼數據流圖如圖3所示。首先FIFO1接收到的TS數據到其存儲量的一半(2KB),發出中斷(INTa)激活DMA3。DMA3把FIFO1里一半的數據倒到C6701的片內存儲器TS_Buffer中,并在傳輸完成時發出中斷(INTb),INTb的中斷服務程序發出信號semPES激活解復用任務。解復用任務從片內存儲器中取出TS數據進行相應處理,然后把分離出的音視頻PES數據送回片內存儲器,當A_PES_Buffer填充一半時,通過信號量semAudio激活音頻處理任務。音頻處理任務從A_PES_Buffer中取出音頻PES數據,解碼后存到A_Buffer。當A_Buffer中的數據積累到一定數量時,激活DMA2。DMA2把解碼后的4KB音頻數據輸出給FIFO2,FIFO2的/FF信號(滿標志)啟動音

頻數據由FIFO2的讀出。音頻輸出FIFO2半空時會發出中斷INTc,激活DMA2。DMA2把A_Buffer中的數據再傳送2KB到FIFO2去,如此繼續下去。視頻PES數據由DMA0從V_PES_Buffer不斷地倒到片外SDRAM中,當接到STi7000請求時,激活DMA1,把SDRAM中緩存的的視頻PES數據輸出給STi7000,進行解碼,然后,經視頻后處理后輸出給顯示器。

解復用的功能包括:PSI分析,時鐘恢復以及對傳輸包拆包并傳給相應的buffer(緩存器)。

視頻解碼的功能是對視頻PES進行解壓縮,恢復出視頻流。在系統中,Video Driver的中斷的優先級被設為最高。視頻解碼系統主要是通過中斷來觸發其它過程的進行,中斷是視頻解碼主線,操縱著整個視頻解碼的過程。

音頻解碼的功能是對音頻PES進行AC-3解壓縮,恢復出音頻流。音頻解碼從音頻PES包解碼開始,在6701片內的數據存儲區中開辟A_PES_Buffer(由兩塊各4KB對稱的存儲區組成),解復用得到的音頻PES數據以乒乓方式存儲到這兩個區域。經過拆包PES數據得到的ES數據直接覆蓋PES數據所處區域。然后開始音頻解碼的核心計算,將解碼輸出的PCM數據格式化后存儲到片內數據存儲區中開辟的兩塊(各16K)PCM緩沖區中,利用DMA2將其中的數據輸出給片外的FIFO。

結語

本論文提出了一種基于通用DSP C6701的HDTV信源解碼器兩片解決方案。隨著技術的進步,將來可能會提出HDTV信源解碼器單片解決方案。即在單個功能強大的芯片的基礎上,很多工作可以由軟件控制實現。本論文提出的HDTV信源解碼器解決方案對于下一代HDTV信源解碼器的研制具有重要的參考價值。

電子發燒友App

電子發燒友App

評論