隨著嵌入式計算機應用的發展,嵌入式CPU的主頻不斷提高,這就造成了慢速系統存儲器不能匹配高速CPU處理能力的情況。為了解決這個問題,許多高性能的嵌入式處理器內部集成了高速緩存cache。其中,三星公司的S3C44B0X內部就集成了8 KB空間統一的指令和數據Cache。

Cache即高速緩沖存儲器,是位于CPU與主存之間一種容量較小,但速度很高的存儲器。由于CPU在進行運算時,所需的指令和數據都是從主存中提取的,而CPU運算速度要比主存讀寫速度快得多,這樣極其影響整個系統的性能。采用Cache技術,即在Cache中存放CPU常用的指令和數據,然后將這些數據和指令以一定的算法和策略從主存中調入,使CPU可以不必等待主存數據而保持高速操作。這樣就滿足了嵌入式系統實時、高效的要求。但Cache的使用也帶來了一致性的問題,在應用中應特別注意。

1 Cache一致性問題的發現

本項目的目標板為:處理器采用ARM芯片S3C44B0X,存儲器采用2片Flash和1片SDRAM,在調試的時候輸入采用鍵盤,輸出采用顯示器,用RS232串口實現通信。

在項目的開發過程中,經軟件仿真調試成功的程序,燒入目標板后,程序卻發生異常中止。通過讀存儲器的內容發現,程序不能正常運行在目標板上,是因為存儲器中寫入的數據與程序編譯生成的數據不一致,總是出現一些錯誤字節。

經過一段時間的調試發現,只要在程序中禁止Cache的使用,存儲器中寫入的數據將不再發生錯誤,程序可以正常運行,但速度明顯減慢。經過分析,認為問題是由于Cache數據與主存數據的不一致性造成的。

Cache數據與主存數據不一致是指:在采用Cache的系統中,同樣一個數據可能既存在于Cache中,也存在于主存中,兩者數據相同則具有一致性,數據不相同就叫做不一致性。如果不能保證數據的一致性,那么,后續程序的運行就要出現問題。

2 分析Cache的一致性問題

要解釋Cache的一致性問題,首先要了解Cache的工作模式。Cache的工作模式有兩種:寫直達模式(writethrough)和寫回模式(writeback)。寫直達模式是,每當CPU把數據寫到Cache中時,Cache控制器會立即把數據寫入主存對應位置。所以,主存隨時跟蹤Cache的最新版本,從而也就不會有主存將新數據丟失這樣的問題。此方法的優點是簡單,缺點是每次Cache內容有更新,就要對主存進行寫入操作,這樣會造成總線活動頻繁。S3C44B0X中的Cache就是采用的寫直達模式(writethrough)。在寫直達模式下,數據輸出時,系統會把數據同時寫入高速緩沖存儲器Cache和主存中,這樣就保證了輸出時高速緩沖存儲器的一致性。但該模式下,卻無法保證輸入時的高速緩沖存儲器的一致性。

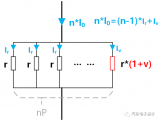

下面再看一下Cache的組織方式。按照主存和Cache之間的映像關系,Cache有三種組織方式。全相聯方式、直接映像方式和組相聯方式。其中,直接映像方式的原理如圖1所示。

按照Cache的行數m,把主存分為n/m個區域,每個區中有m個存儲塊。各區中的0~(m-1)塊一一對應地固定映射到Cache中L0~Lm-1行。這樣,標簽只要給定區地址(區號),就能唯一確定Cache行與存儲器的對應關系。當CPU發出存儲器訪問時,以存儲器地址作為行索引,尋址到一高速緩沖行,檢測該行的標簽。若標簽與存儲器的相應地址匹配,則Cache命中。該高速緩存行當前即為欲訪問存儲塊的唯一映像。從上面的分析可以看出,在寫直達模式下,由于每次Cache內容有更新,就要對主存進行寫入操作,造成總線活動頻繁。在Cache命中的過程中,如果總線遇到干擾,就會出現數據不一致的現象。

3 Cache一致性問題的解決方法

該問題可以從軟件及硬件兩方面著手解決。

3.1 軟件解決的方法

S3C44B0X的Cache提供完整的Cache使能和禁止操作模式。能夠通過設置SYSCFG寄存器中CM域中的值為01或11來使能Cache(其中,01為使能4 KB Cache, 11為使能8 KB Cache),而通過清除SYSCFG寄存器中[2:1]域為0來禁止Cache功能。用禁止Cache的方法來消除數據不一致性問題,具體代碼如下:

#define rSYSCFG(*(volatile unsigned *)0x1c00000)

#define WRBUFOPT (0x8) //write_buf_on

#define SYSCFG_0KB (0x0|WRBUFOPT)

#define SY

?

SCFG_4KB (0x2|WRBUFOPT)

#define SYSCFG_8KB (0x6|WRBUFOPT)?

#define cacheCFGSYSCFG_0KB

rSYSCFG= CACHECFG; //禁止Cache

另外,S3C44B0X還提供了2個不能Cache訪問的區域(noncacheable area)。每個區域要求兩個Cache控制域,用來表明每一個不能Cache訪問區域的起始和結束地址。在不能Cache訪問的區域,當Cache沒有命中,一個讀的時候,Cache不能更新。在已知影響到數據不一致的地址情況下,可以在使能Cache的條件下,用設定不能Cache訪問區域的方法,防止產生數據不一致現象。有時,如果數據區域被安排在不能Cache區域,程序執行速度更高,因為多數變量是不能重用的。對于不能重用的變量,刷新16 B的Cache存儲器是浪費的。本系統中設定不能Cache訪問的區域為0x2000000~0xc000000,就可以解決數據不一致問題。代碼如下:

#define rSYSCFG(*(volatile unsigned *)0x1

c00000)

#define WRBUFOPT (0x8) //write_buf_on

#define SYSCFG_0KB (0x0|WRBUFOPT)

#defineSYSCFG_4KB (0x2|WRBUFOPT)

#define SYSCFG_8KB (0x6|WRBUFOPT)?

#define CACHECFG SYSCFG_8KB

#define rNCACHBE0 (*(volatile unsigned *)0x1c00004)

#define rNCACHBE1 (*(volatile unsigned *)0x1c00008)

#define Non_Cache_Start(0x2000000)

//不能Cache訪問的區域開始地址

#define Non_Cache_End(0xc000000)

//不能Cache訪問的區域結束地址

rSYSCFG= CACHECFG;?

// 8 KB cache,寫緩沖使能,data abort使能?

rNCACHBE0= ((Non_Cache_End>>12)<<16)|(Non_Cache_Start>>12);//在上面的數據區域不使用高速緩存Cache

采用上述兩種方法,排除了數據不一致性的問題。但一個高性能的系統是需要Cache的,禁止Cache的使用會大大降低系統的性能。所以,在嵌入式系統的設計中,還應從硬件方面考慮,從根本上防止數據不一致的產生。

3.2 硬件的解決方法

由于現在的嵌入式處理器,主頻越來越高,地址、數據線越來越多,所以在硬件的設計和焊接過程中應特別注意高頻干擾的問題。因為高頻干擾可以引起信號的不完整性,這些不完整的信號會引起總線傳輸過程中出現一些壞字節,所以高速PCB設計變得尤為重要。高速PCB設計中,對高速信號網絡的特征與走線

控制的設計技術,已成為高速數字設備成功與否的關鍵。在設計中應注意下列問題:

① 在成本允許的條件下, PCB盡量采用多層板布線。

② 高頻電路布線的引線最好采用全直線,需要轉折時,可以用45°折線或圓弧轉折。在高頻電路中

,滿足這一要求可以減少高頻信號對外的發射和相互間的耦合。

③ 高頻電路器件引腳的引線層間的交替越少越好,過孔越少越好。據測,一個過孔可帶來約0.5 pF

的分布電容,減少過孔數量能顯著提高速度。

④ 高頻電路布線要注意信號線近距離平行走線所引入的“交叉干擾”,若無法避免平行分布,可在

平行信號線的反面布置大面積“地”來減少干擾。同一層內的平行走線幾乎無法避免,但是在相鄰的兩個

層,走線的方向務必取為相互垂直。

⑤ 每個集成電路塊的附近應設置一個高頻退耦電容。

⑦ 對特別重要的信號線或局部單元實施地線包圍的措施,各類信號走線不能形成環路,地線也不能

形成電流環路。

在注意了上面的設計規則之后,制作出的PCB基本上可以滿足高速信號的要求。

最后,就是在焊接時要注意焊點一定要圓滑。因為焊點的尖峰會產生很強的高頻干擾。

有了上述各條規則,就保證了在信號傳輸過程中,總線上不會出現不必要的干擾,防止了數據不一致的發生。

結語

嵌入式處理器已經被廣泛應用。本文提到的對S3C44B0X中cache數據不一致性的處理方法同樣適用于其他型號的高頻嵌入式處理器。掌握一些設計、調試的基本經驗,可以大大提高工作效率,減小系統開發過程中不必要的麻煩。

電子發燒友App

電子發燒友App

評論