1 mig接口說明

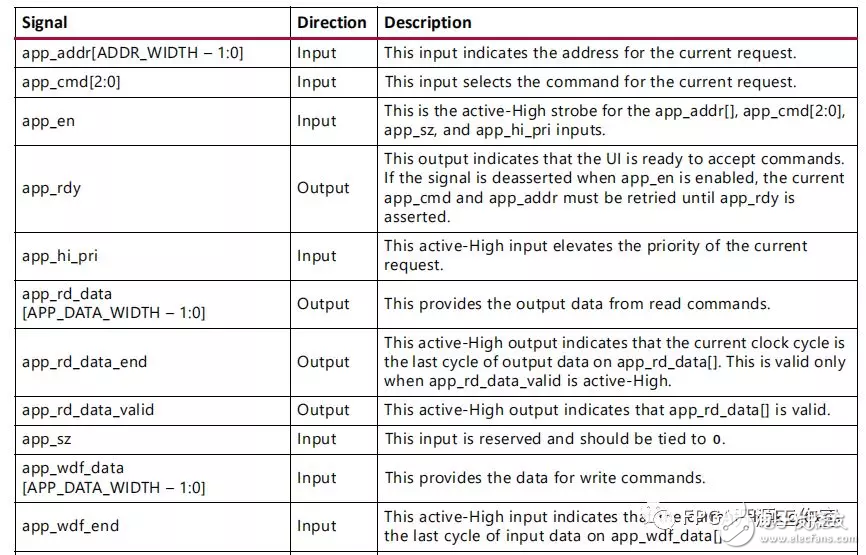

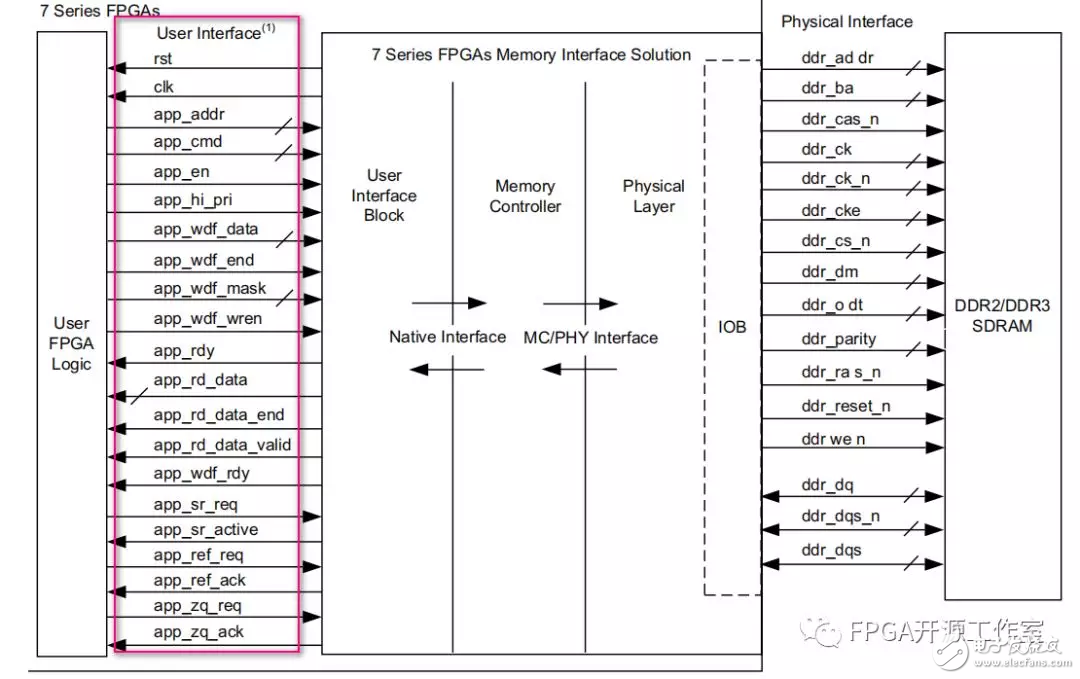

對于mig與DDR3/DDR2 SDRAM的讀寫時(shí)序我們不需要了解太多,交給mig就可以了。我們需要做的是控制好User Interface,寫出正確的User logic。想要寫好Userlogic,我們就必須清楚每一個(gè)用戶控制接口的含義:

a. app_addr[ADDR_WIDTH – 1:0]:此輸入指示當(dāng)前提交給UI的請求的地址。 UI聚合外部SDRAM的所有地址字段,并為您提供平面地址空間(Rank,bank,row,colum)。

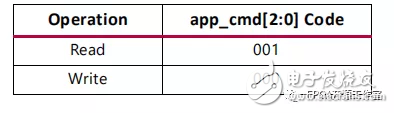

b. app_cmd[2:0]:此輸入指定當(dāng)前提交給UI的請求的命令。

c. app_en:此輸入在請求中變化。您必須將所需的值應(yīng)用于app_addr []和app_cmd [2:0],然后斷言app_en以將請求提交給UI。這會通過斷言app_rdy來啟動UI確認(rèn)的握手。

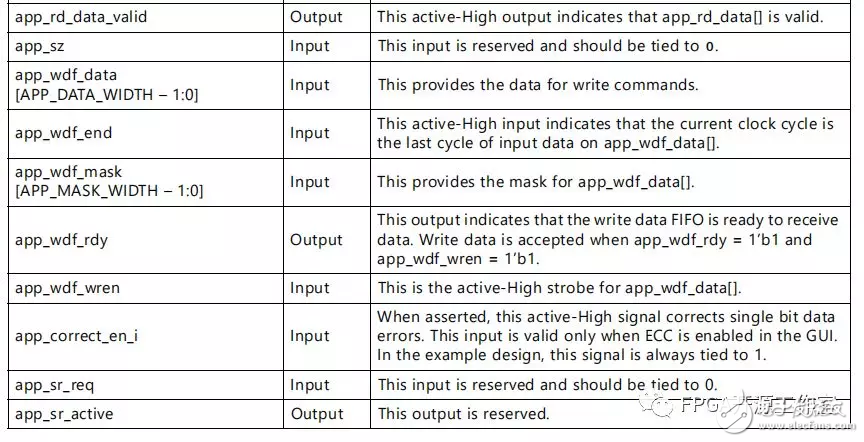

d. app_wdf_data[APP_DATA_WIDTH – 1:0]:該總線提供當(dāng)前正在寫入外部存儲器的數(shù)據(jù)。

e. app_wdf_end:此輸入指示當(dāng)前周期中app_wdf_data []總線上的數(shù)據(jù)是當(dāng)前請求的最后一個(gè)數(shù)據(jù)。

f. app_wdf_wren:此輸入表示app_wdf_data []總線上的數(shù)據(jù)有效。

g. app_wdf_rdy:此輸出表示寫數(shù)據(jù)FIFO已準(zhǔn)備好接收數(shù)據(jù)。當(dāng)app_wdf_rdy和app_wdf_wren都被聲明時(shí),接受寫入數(shù)據(jù)。

h. app_wdf_mask[APP_MASK_WIDTH – 1:0]:該總線指示app_wdf_data []的哪些字節(jié)寫入外部存儲器以及哪些字節(jié)保持其當(dāng)前狀態(tài)。通過將值1設(shè)置為app_wdf_mask中的相應(yīng)位來屏蔽字節(jié)。例如,如果應(yīng)用程序數(shù)據(jù)寬度為256,則掩碼寬度取值為32. app_wdf_data的最低有效字節(jié)[7:0]使用app_wdf_mask的Bit [0]屏蔽,app_wdf_data的最高有效字節(jié)[255:248]使用app_wdf_mask的Bit [31]屏蔽。因此,如果必須屏蔽最后一個(gè)DWORD,即app_wdf_data的字節(jié)0,1,2和3,則app_wdf_mask應(yīng)設(shè)置為32‘h0000_000F。

i. app_rdy:此輸出指示您是否接受當(dāng)前提交給UI的請求。如果在確認(rèn)app_en后UI未聲明此信號,則必須重試當(dāng)前請求。如果出現(xiàn)以下情況,則不會聲明app_rdy輸出:

1》PHY /內(nèi)存初始化尚未完成;

2》所有bank都被占用(可以看作命令緩沖區(qū)已滿);

3》請求讀取并且讀取緩沖區(qū)已滿;

4》請求寫入,沒有可用的寫緩沖區(qū)指針;

5》正在插入定期讀取。

j. app_rd_data[APP_DATA_WIDTH – 1:0]:此輸出包含從外部存儲器讀取的數(shù)據(jù)。

k. app_rd_data_end:此輸出表示當(dāng)前周期中app_rd_data []總線上的數(shù)據(jù)是當(dāng)前請求的最后一個(gè)數(shù)據(jù)。

l. app_rd_data_valid:此輸出表明app_rd_data []總線上的數(shù)據(jù)有效。

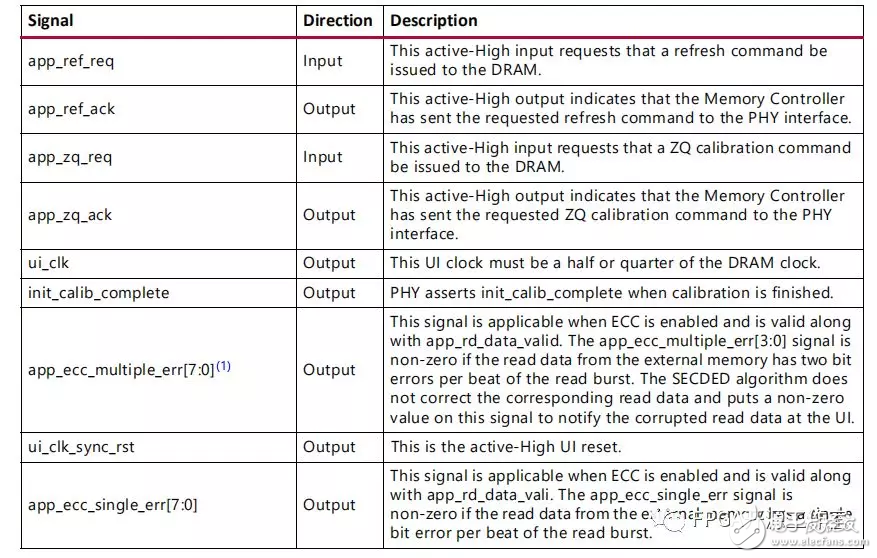

m. ui_clk_sync_rst:reset信號來自于UI,與ui_clk同步。

n. ui_clk:這是UI的輸出時(shí)鐘。它必須是輸出到外部SDRAM的時(shí)鐘頻率的一半或四分之一,這取決于在GUI中選擇的2:1或4:1模式。

o. init_calib_complete:校準(zhǔn)完成后,PHY將init_calib_complete置‘1’。在將命令發(fā)送到內(nèi)存控制器之前,應(yīng)用程序無需等待init_calib_complete。

p. app_ref_req:置位時(shí),此高電平有效輸入請求內(nèi)存控制器向DRAM發(fā)送刷新命令。它必須在一個(gè)周期內(nèi)進(jìn)行脈沖以發(fā)出請求,直到app_ref_ack信號被置位以確認(rèn)請求并指示它已被發(fā)送,然后置為無效。

q. app_ref_ack:置位時(shí),此高電平有效輸入確認(rèn)刷新請求,并指示該命令已從存儲器控制器發(fā)送到PHY。

r. app_zq_req:置位時(shí),此高電平有效輸入請求存儲器控制器向DRAM發(fā)送ZQ校準(zhǔn)命令。它必須在一個(gè)周期內(nèi)進(jìn)行脈沖以發(fā)出請求,直到app_zq_ack信號被置位以確認(rèn)請求并指示它已被發(fā)送,然后取消置位。

s. app_zq_ack:置位時(shí),此高電平有效輸入確認(rèn)ZQ校準(zhǔn)請求,并指示該命令已從存儲器控制器發(fā)送到PHY。

了解了每個(gè)信號的作用我們來講解mig 用戶邏輯的讀寫時(shí)序。

2 命令與地址

如上圖所示①,②,③情況,只有在③時(shí)刻app_en和app_rdy同時(shí)為高電平app_cmd(命令)和(app_addr)地址才有效,所以當(dāng)需要app_cmd,app_addr有效時(shí)app_en必須保持到app_rdy為高電平才有效。

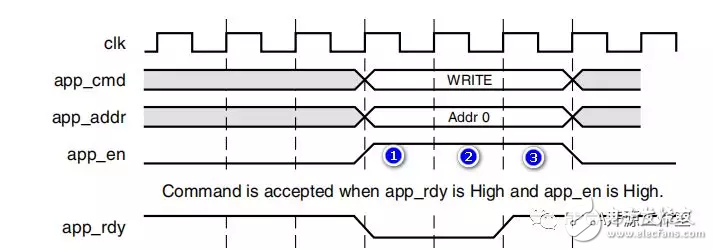

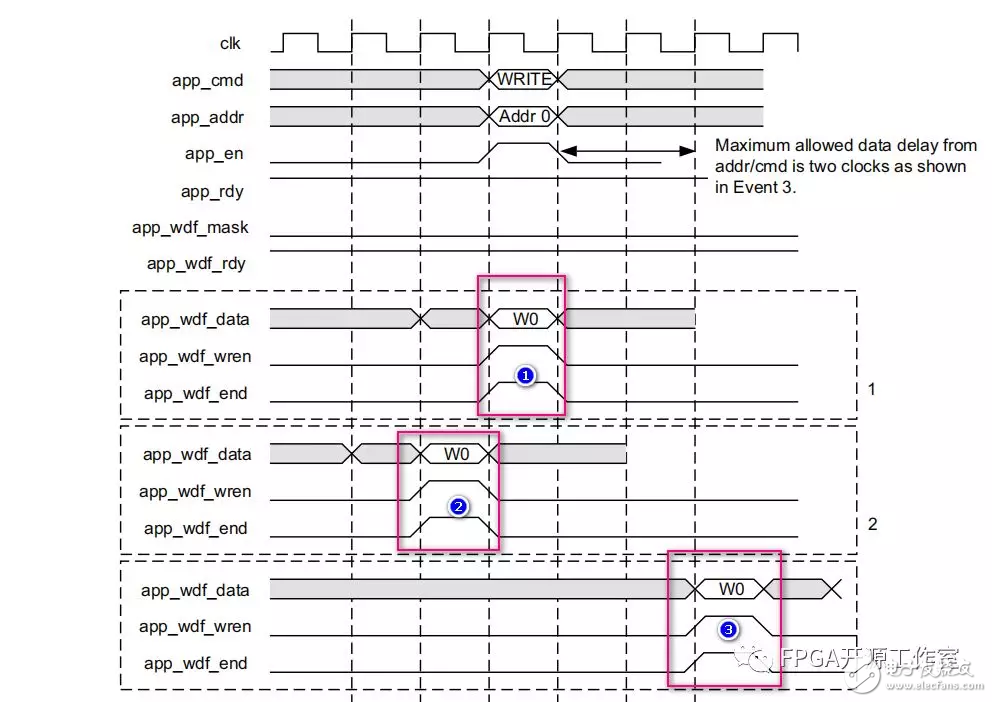

3寫時(shí)序

如上圖所示①,②,③種情況,寫命令和寫數(shù)據(jù)直接存在三種邏輯關(guān)系。

1,①表示寫命令(app_cmd),寫當(dāng)前地址(app_addr)和寫數(shù)據(jù)(app_wdf_data)以及寫控制信號(app_en,app_rdy,app_wdf_rdy,app_wdf_wren,app_wdf_end)同時(shí)有效。

2,②表示寫數(shù)據(jù)(app_wdf_data)和寫控制信號(app_wdf_wren,app_wdf_end)先于寫命令(app_cmd)和寫當(dāng)前地址(app_addr)以及其他寫控制信號(app_en,app_rdy,app_wdf_rdy)一個(gè)用戶時(shí)鐘(ui_clk)。

3,③表示寫數(shù)據(jù)(app_wdf_data)和寫控制信號(app_wdf_wren,app_wdf_end)遲于寫命令(app_cmd)和寫當(dāng)前地址(app_addr)以及其他寫控制信號(app_en,app_rdy,app_wdf_rdy)。最多兩個(gè)用戶時(shí)鐘(ui_clk)。

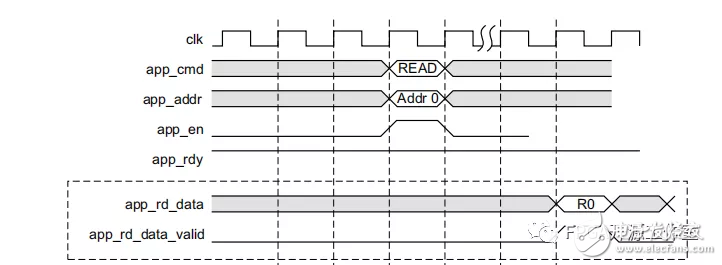

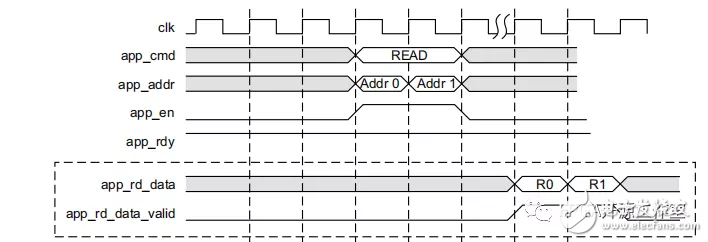

4讀時(shí)序

如上圖所示,當(dāng)讀命令(app_cmd)和當(dāng)前讀地址(app_addr)以及讀控制信號(app_en,app_rdy)同時(shí)有效時(shí),等待讀數(shù)據(jù)有效信號(app_rd_data_valid)有效時(shí)讀數(shù)據(jù)(app_rd_data)有效。

電子發(fā)燒友App

電子發(fā)燒友App

評論