隨著計算機網(wǎng)絡技術和電子信息技術的迅猛發(fā)展,Internet的普及,接入Internet的非PC設備越來越多,各類電子設備像Web個人數(shù)字助理、Web可視電話、TV機頂盒接入Internet的需求也越來越大,嵌入式TCP/IP的Internet網(wǎng)絡化將成為網(wǎng)絡發(fā)展的趨勢。

嵌入式系統(tǒng)中大量存在的是8/16位低速處理器,在進行Internet接入時,嵌入式TCP/IP對于計算機存儲器、運算速度要求比較高,占用大量系統(tǒng)資源,因而常嵌入TCP/IP協(xié)議簇的子集或用UDP代替TCP實現(xiàn)。

本文提出一種基于嵌入式TCP/IP軟件體系結構的優(yōu)化設計和實現(xiàn)方案,從實現(xiàn)相應的功能又節(jié)省系統(tǒng)資源角度出發(fā),對嵌入TCP/IP優(yōu)化設計,實現(xiàn)嵌入式的Internet接入。

嵌入式TCP/IP接入方法

嵌入式電子設備接入Internet有多種解決方案:在低速微處理器運行剪裁的TCP/IP協(xié)議棧;使用一些ASIC實現(xiàn)TCP/IP的芯片如ADI的InternetModem;也可以使用嵌入式操作系統(tǒng)自帶的完整的TCP/IP協(xié)議棧。在某些對網(wǎng)絡速度要求不高的領域,可以精簡的TCP/IP實現(xiàn);在對性能要求高的場合,則可以選擇后兩種方案。嵌入式設備接入Internet網(wǎng)絡常用的方案比較如表1所示。

但以上接入方法一般專門為某種微處理器設計,不具有通用性,而且效率較低或功能不夠全面[3]。本文提出的經(jīng)過優(yōu)化設計的嵌入式TCP/IP適合移植到各種嵌入式處理器中,如單片機、ARM或ARM+FPGA多核嵌入式處理器中,具有較小的代碼量、RAM使用量和較高的效率,同時支持套接字形式的多個TCP連接和多個網(wǎng)絡設備連接,支持通過網(wǎng)關發(fā)送數(shù)據(jù)包和數(shù)據(jù)包轉發(fā),支持TCP包的整序、重發(fā)和窗口控制流量控制等等。

嵌入式TCP/IP的軟件體系結構與優(yōu)化設計

嵌入式TCP/IP軟件體系結構

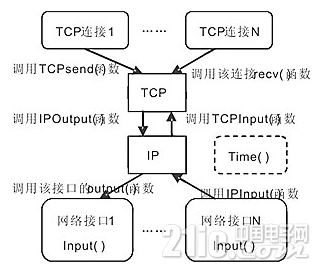

與PCTCP/IP協(xié)議相似,嵌入式TCP/IP采用協(xié)議分層的結構:應用層、TCP層、IP層和網(wǎng)絡設備接口層[4]。圖1描述了嵌入式TCP/IP輸入和輸出數(shù)據(jù)包流程以及調(diào)用的函數(shù)。

圖1基于嵌入式TCP/IP接口結構

其中,Timer()函數(shù)調(diào)用TCPTimer()處理TCP數(shù)據(jù)包重發(fā),以及調(diào)用每個接口的Input()函數(shù)接收到達的數(shù)據(jù)包。Timer()函數(shù)必須在短時間(一般《20ms)內(nèi)被調(diào)用一次,否則接收數(shù)據(jù)包和TCP定時等功能將停止。

輸出時,TCP層先查看unsend隊列,發(fā)現(xiàn)非空,將數(shù)據(jù)包插入隊列;發(fā)現(xiàn)為空,則查看對方窗口是否夠大能夠接收這個數(shù)據(jù)包,然后填寫TCP頭部信息。IP層選擇網(wǎng)絡設備接口,目的IP和該接口的子網(wǎng)掩碼相與是否等于子網(wǎng)掩碼。然后調(diào)用這個接口的Output函數(shù)來發(fā)送。

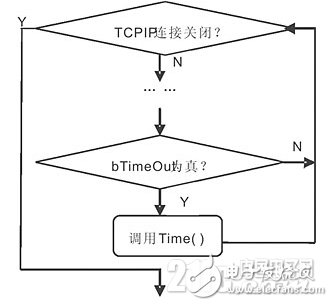

圖2基于嵌入式TCP/IP主程序結構

輸入時,Timer()函數(shù)調(diào)用每個接口的Input函數(shù)。IP層判斷IP版本、IP校驗和、判斷是否應該轉發(fā)數(shù)據(jù)包,然后根據(jù)IP頭部的protocol字段將包傳給相應的高層處理。TCP層,需要判斷TCP校驗和,然后在現(xiàn)有的套接字中查找,判斷是否有套接字可以接收這個數(shù)據(jù)包,判斷TCP序號是否為希望的,然后更新這個連接的狀態(tài)(包括釋放被應答的數(shù)據(jù)包和TCP狀態(tài)機的轉化等),調(diào)用該套接字的回調(diào)函數(shù)recv。

圖2程序主流程是一個大循環(huán),在循環(huán)中處理發(fā)送數(shù)據(jù)包等應用層協(xié)議同時查詢變量bTimeOut,在定時中斷中將bTimerOut設置為真,應用層在程序流程中反復查詢bTimerOut是否為真,真則調(diào)用Timer(),然后置bTimerOut為假。

嵌入式TCP/IP設計優(yōu)化

因為網(wǎng)絡中數(shù)據(jù)非常多,如果把所有的數(shù)據(jù)都讀到內(nèi)存中再判斷是否應該丟棄幀顯然效率不高。所以邊讀取數(shù)據(jù)邊判斷而沒有一開始就把整個幀全部讀到內(nèi)存中,同時在程序里定義幀中各個部分的相對地址,可以方便的對幀的各個字節(jié)尋址。這樣的設計是基于提高訪問速度考慮的。

為了減小RAM使用量,當數(shù)據(jù)包需要重新發(fā)送時,如果能夠重新產(chǎn)生數(shù)據(jù)包所需的數(shù)據(jù),可以不存儲需要被應答的TCP包。圖3給出了嵌入式CPU中TCP/IP的內(nèi)存劃分,以及內(nèi)存中幀的各個字節(jié)的定義和相對位置,其中PacketRAM為存放幀的首地址。

發(fā)送TCP/IP過程中主要的運算量集中在三個部分:應用程序?qū)?shù)據(jù)拷貝到RAM、計算TCP校驗和、將RAM中的數(shù)據(jù)包拷貝到網(wǎng)絡設備的發(fā)送緩沖區(qū)。對每一個字節(jié)數(shù)據(jù),兩次拷貝大致共使用12×2=24個指令周期;計算TCP校驗和使用為16個指令周期。為提高速度可采用快速CPU或提高晶振頻率。例如采用12M晶振時,網(wǎng)絡傳輸速度為25K字節(jié)/s;而在高頻PCB電路板使用233M晶振時,網(wǎng)絡傳輸速度能達到為384K字節(jié)/s。

另外,TCP/IP一般采用C語言或者混合匯編,而使用可重入函數(shù)和一般指針(genericpointer)使得程序代碼增大,運行速度變慢。所以使用函數(shù)指針時,應手動重建調(diào)用樹(Calltree),或?qū)⒑瘮?shù)指針調(diào)用的函數(shù)設置為可重入函數(shù),同時使用“指定存儲類型”的指針(memory-specificpointer),防止數(shù)據(jù)包的不必要的拷貝以及優(yōu)化計算校驗和和內(nèi)存拷貝函數(shù)。另外,Reentrant類型的函數(shù)比一般函數(shù)速度要慢很多,但是某些時候為了程序結構的需要必須使用Reentrant,這就需要在速度和結構之間作一個選擇。

嵌入式TCP/IP的實現(xiàn)

TCP/IP的嵌入式實現(xiàn)一般通過以軟件方式嵌入到ROM中,然后通過輕網(wǎng)絡通訊技術與專用嵌入式網(wǎng)關連接,在嵌入式處理器中運行TCP/IP協(xié)議,提供TCP/IP到用戶的輕型網(wǎng)絡的連接和路由功能。

內(nèi)存管理方法和無多余數(shù)據(jù)包拷貝的實現(xiàn)

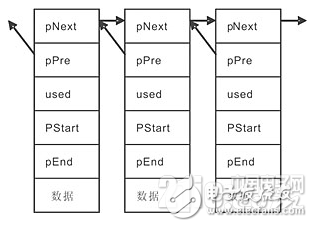

嵌入式TCP/IP的內(nèi)存管理可以用鏈表方法,即根據(jù)數(shù)據(jù)包大小分配相應大小的內(nèi)存塊。如圖4所示,鏈表將內(nèi)存塊鏈接起來,used字段表示該內(nèi)存塊是否正在使用,pSstart和pEend則表示數(shù)據(jù)部分有效數(shù)據(jù)的開始地址和結束地址。搜索內(nèi)存鏈表找到一個沒有分配的比所需空間大的內(nèi)存塊,截取所需的大小。該內(nèi)存塊被截取以后可能還有較多剩余,這時將剩余部分從原內(nèi)存塊中分離出來,成為一個新的內(nèi)存塊,并插入鏈表。釋放時,將used值置為假,如果pNext或者pPre指向的鏈表單元也是空閑的,則將其和自己合并,以防止內(nèi)存分片。在協(xié)議層之間傳送數(shù)據(jù)包只需傳送內(nèi)存塊的起始地址。這種內(nèi)存管理方法,空間浪費小但是運算量相對較大。

圖4基于嵌入式TCP/IP內(nèi)存管理

整序、重發(fā)和窗口控制的實現(xiàn)

對于嵌入式TCP/IP系統(tǒng),可以使用隊列緩存的方式來實現(xiàn)整序、重發(fā)和窗口控制。隊列的一個元素指向一個數(shù)據(jù)包,隊列的最大長度沒有限制。

對于整序,使用ooSeq隊列,如果發(fā)現(xiàn)接收的TCP包序號并不是期望的,但序號在接收窗口內(nèi),此時不能立刻接收這個包也不應丟棄,可先將這個包放入ooSeq隊列。當期望TCP包被接收后,再查看ooSeq隊列現(xiàn)在是否有TCP包成為了期望的數(shù)據(jù)包,如果有則將其取出并處理。

對于重發(fā),使用unacked隊列,每一個需要被應答的TCP數(shù)據(jù)包發(fā)送以后都要放入unacked隊列,等到被應答以后才從隊列中刪除。TCP重發(fā)定時只針對unacked隊列第一個TCP包,如果定時超出,重新發(fā)送,重發(fā)次數(shù)超出規(guī)定值,則報錯。

對于窗口控制,使用unsend隊列,如果發(fā)現(xiàn)對方的窗口過小無法接收這個數(shù)據(jù)包,則只發(fā)送部分數(shù)據(jù),將多余部分放入unsend隊列,等待對方發(fā)來TCP包通知新的窗口大小時,再次判斷是否可以發(fā)送。如果在unsend隊列不為空的情況下,需要發(fā)送的數(shù)據(jù)包都應插入unsend隊列。

嵌入式TCP/IP的性能分析

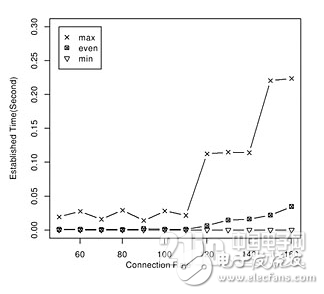

圖5給出了將優(yōu)化設計后的TCP/IP移植到ARM9處理器、CS8900A網(wǎng)絡控制器中,時鐘頻率為133MHz下,與Internet連接的情況。

圖5連接圖

系統(tǒng)支持最大發(fā)起連接數(shù)約為380,最大并發(fā)連接率約為170cps。隨著呼叫數(shù)的增加,平均分組到達也隨之增加,導致網(wǎng)絡傳輸數(shù)據(jù)的增加,從而最大建立時間變長。但最小的建立連接時間基本保持不變,說明系統(tǒng)具有良好的性能。

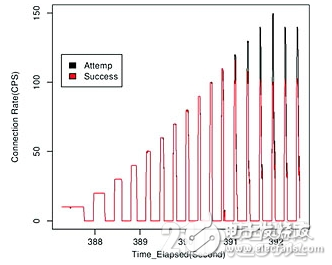

圖6給出了隨建立時間變化的接通率。圖中存在一個臨界點,成功的連接率隨著TCP連接嘗試數(shù)目增加而減少,直至為0,而響應時間也急劇上升,這是由嵌入式處理器的處理能力有限造成的。

圖6隨建立時間變化的連接圖

結語

本文從實現(xiàn)相應的功能又節(jié)省系統(tǒng)資源角度出發(fā),對嵌入式TCP/IP協(xié)議簇進行優(yōu)化設計,可以在各種嵌入式處理器上實現(xiàn)Internet接入。

經(jīng)過優(yōu)化設計的嵌入式TCP/IP支持套接字形式的多個TCP連接、支持多個網(wǎng)絡設備、支持通過網(wǎng)關發(fā)送數(shù)據(jù)包和數(shù)據(jù)包轉發(fā)功能,以及支持TCP包的整序、重發(fā)和窗口控制流量控制。實踐證明,這種設計方式靈活,能按用戶需求實現(xiàn)復雜的功能。

電子發(fā)燒友App

電子發(fā)燒友App

評論