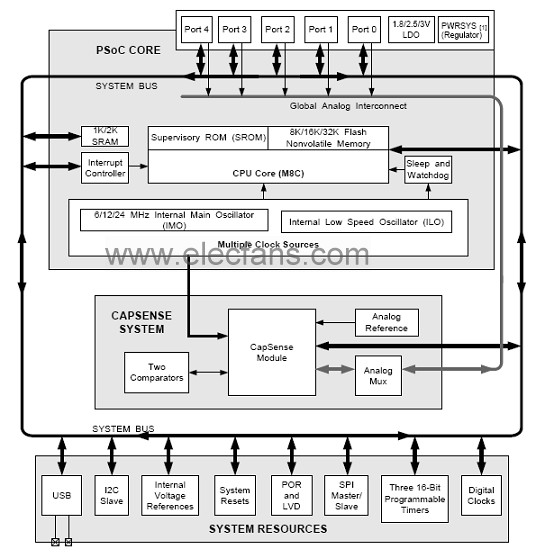

賽普拉斯的PSoC微控制器易于使用、靈活并具有一系列經(jīng)濟高效的可重新編程的模擬和數(shù)字資源。通過這些特性可以實現(xiàn)各種創(chuàng)意設(shè)計,例如使用板上主機處理器對PSoC進行串行編程。此方法用于現(xiàn)場安裝或更新固件,甚至對PSoC完全重新編程,以實現(xiàn)其他功能。

HSSP代碼示例由賽普拉斯創(chuàng)建,旨在幫助系統(tǒng)設(shè)計人員開始創(chuàng)建自己的串行編程軟件。設(shè)計人員必須最大限度地減少對該代碼的修改,以保證其與特定的主機編程器兼容。該代碼示例僅涵蓋CY8C20xx6A系列的PSoC器件,具有高度抽象性。有關(guān)串行編程的更多信息,請參閱ISSP編程規(guī)范。本文概括介紹了實現(xiàn)方法。協(xié)議詳細(xì)信息和各個矢量的含義是專有信息,本文故意省略了這些內(nèi)容。

概述

PSoC器件可通過兩種不同的模式進行編程:復(fù)位模式和重啟模式。復(fù)位模式是首選編程模式,僅在系統(tǒng)采用外部供電時使用。在這種情況下,目標(biāo)PSoC上的XRES引腳將于流程結(jié)束時切換,使其跳出編程模式,并恢復(fù)正常操作。在重啟模式下,主機微處理器將切換PSoC電源的開關(guān)。

在兩種編程模式下,主機均需要三個I/O引腳。在復(fù)位模式下分別為串行數(shù)據(jù)(SDATA)、串行時鐘(SCLK)和外部復(fù)位(XRES)引腳,在電源循環(huán)模式下則為SDATA、SCLK和PSoC電源(PWR)引腳。這些引腳通過軟件控制。

主機處理器上的SDATA引腳必須為雙向引腳。主機必須能夠更改該引腳的屬性,以便用其向PSoC發(fā)出信號、將其釋放到High Z狀態(tài),以及從該引腳讀取信號。

屬性選擇

設(shè)計人員必須設(shè)置以下兩個屬性:標(biāo)簽和說明。要進行此設(shè)置,可以對ISSP_DIRECTIVES.H文件中的某些#define進行注釋或取消注釋。這些#define標(biāo)有“User Attention Required”(用戶需要注意)標(biāo)簽,非常明顯,很容易找到。您還可以進行頁面搜索,查找單個標(biāo)簽。每個屬性的說明及其標(biāo)簽將列于屬性下方:

屬性:編程模式

標(biāo)簽:PROGRAMMING MODE(編程模式)

說明:如果采用的是重啟模式,則應(yīng)對該#define進行注釋。如果采用的是復(fù)位模式,則應(yīng)取消注釋該#define語句。

屬性:目標(biāo)PSoC器件

標(biāo)簽:TARGET?PSOC(目標(biāo)PSOC)

說明:在此部分中選擇目標(biāo)CY8C20xx6A PSoC。在任何給定情況下,均只能啟用一個器件,所有其他的器件均應(yīng)注釋掉。低層驅(qū)動程序修改。

設(shè)計人員根據(jù)主機特定代碼,以操作在對目標(biāo)PSoC進行編程時所涉及的引腳。這些API可以在ISSP_DRIVER_ROUTINES.C找到,并標(biāo)有“Processor Specific”(特定處理器)和“User Attention Required”(用戶需要注意)。

■端口位掩碼:對于使用的特定主機處理器,必須調(diào)整四個端口位掩碼。請注意,雖然要設(shè)置四個位,但根據(jù)所用的編程方法,只需在編程過程中用到以下三個位——復(fù)位模式下為SDATA、SCLK和XRES;電源循環(huán)模式下為SDATA、SCLK和PWR。

■Delay(n)函數(shù):調(diào)整此函數(shù),使while循環(huán)的每次迭代均保持至少1μs。循環(huán)時間通常沒有上限。但是,循環(huán)時間越長,對目標(biāo)的編程時間就越長。例如,如果主機微處理器也是PSoC,每次迭代約為1μs,開銷為3μs。因此,該函數(shù)將產(chǎn)生n+3μs的延遲,其中n是傳遞給該函數(shù)的參數(shù)。要調(diào)整主機處理器的延遲時間,請修改ISSP_DELAYS.H中的#define。

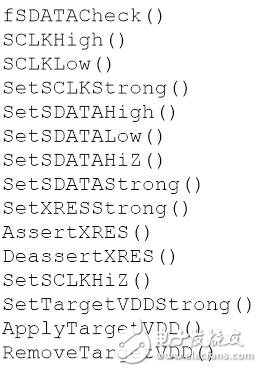

■端口位操作函數(shù):這些函數(shù)將控制主機引腳,以產(chǎn)生PSoC編程所需的信號。它們可以驅(qū)動引腳輸出高低電平,也可以將引腳釋放至High Z狀態(tài)。以下列出了這些函數(shù)。大部分函數(shù)的用途不言自明,但在代碼中均有記錄。附錄中也提供了說明。

向RAM緩沖區(qū)中加載數(shù)據(jù)

HSSP代碼將按順序從128字節(jié)緩沖區(qū)取出數(shù)據(jù),以進行PSoC閃存區(qū)塊編程。此過程從最低區(qū)塊地址開始。對第一個區(qū)塊進行編程后,同一個緩沖區(qū)將用于對后續(xù)閃存區(qū)塊進行編程。

設(shè)計人員必須根據(jù)數(shù)據(jù)來源(USB、RS-232、SD卡等)編寫代碼,以填充該緩沖區(qū)。對于所用的特定主機處理器,應(yīng)編寫以下兩個函數(shù):LoadProgramData()和fLoadSecurityData()。這些函數(shù)可以在ISSP_DRIVER_ROUTINES.C中找到,并標(biāo)有“Processor Specific”(特定處理器)和“User Attention Required”(用戶需要注意)。這些函數(shù)在原始狀態(tài)下,會調(diào)用兩個輔助函數(shù),向緩沖區(qū)加載偽測試數(shù)據(jù),以進行調(diào)試。在最終版本中,請刪除或注釋掉這些調(diào)用語句。

修改閃存區(qū)塊順序或數(shù)量

在某些情況下,必須對閃存中的特定區(qū)域進行編程。例如專用于存儲特征、校準(zhǔn)或固件現(xiàn)場升級的區(qū)域。這些特性通常通過EEPROM用戶模塊實現(xiàn)。但是,在某些情形下,如果代碼空間受限,則可以在PSoC中直接編寫這些特性,以節(jié)省代碼空間。

您可以更改目標(biāo)區(qū)塊的起始地址,以及區(qū)塊的編程順序。上述操作不會產(chǎn)生任何問題,因為每個編程順序均包含區(qū)塊地址。但是,請記住以下幾點:

■如果修改了編程循環(huán),則必須對驗證循環(huán)應(yīng)用相同的變更,否則驗證將會失敗。

■代碼在運行過程中會累加校驗和,并根據(jù)截至當(dāng)時的整個閃存檢查校驗和。如果您僅對閃存的某個區(qū)域進行編程,則應(yīng)相應(yīng)地設(shè)置變量iChecksumData。

利用內(nèi)置測試點進行驗證

要成功實現(xiàn)主機源編程,最關(guān)鍵因素之一是獲取正確的擦除和寫入脈沖寬度。為幫助您完成此過程,在程序的重要位置實現(xiàn)了幾個測試點(TP)調(diào)用。要啟用此調(diào)試模式,在ISSP_DRIVER_SOUTINES.H中取消對USE_TP #ifdef的注釋。有幾個函數(shù)與調(diào)試模式相關(guān),它們與本文之前提及的引腳操作函數(shù)相似。系統(tǒng)設(shè)計人員必須提供主機特定代碼,以驅(qū)動引腳輸出高電平、低電平,或切換引腳。

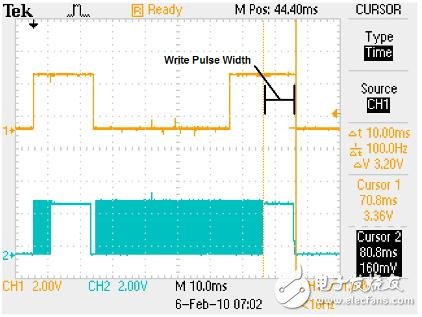

正確的調(diào)試過程需要監(jiān)控TP和SDATA線,且必須測量擦除和編程脈沖。實現(xiàn)此目的的最佳方式是使用雙蹤示波器,并在TP通道的上升沿進行觸發(fā),使其進入單序列模式。

擦除脈沖寬度從數(shù)據(jù)突發(fā)的末端開始測量,到TP下降沿結(jié)束,如圖1所示。請注意,TP上升沿與數(shù)據(jù)突發(fā)末端不在一條線上。但是由于TP引腳被驅(qū)高的時刻與主機開始發(fā)出數(shù)據(jù)的時刻之間存在延遲開銷,因此,TP上升沿預(yù)計會排成一條線。

圖1.測量擦除脈沖寬度

編程脈沖寬度亦是從數(shù)據(jù)突發(fā)的末端開始測量,到TP下降結(jié)束。圖2顯示編程脈沖寬度測量。與擦除脈沖寬度一樣,TP信號的上升沿與數(shù)據(jù)突發(fā)的末端也不在一條線上。

圖2.測量寫入脈沖寬度

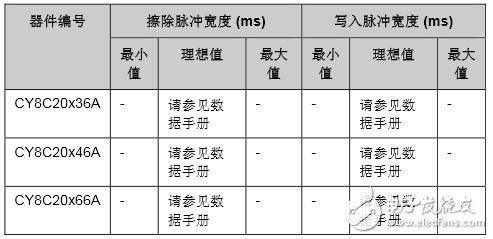

表1匯總了各種PSoC器件的理想擦除和寫入脈沖寬度。測量值必須在理想值-3%到+15%的范圍內(nèi)。無法滿足該要求將導(dǎo)致錯誤編程,并產(chǎn)生不利影響,例如比指定規(guī)范更短的閃存數(shù)據(jù)保留時間,以及比預(yù)期更少的閃存擦除和寫入循環(huán)。

表1.CY8C20xx6A?PSoC的擦除和寫入脈沖寬度

限制

main.c開頭部分的注釋包含有用的重要信息,系統(tǒng)設(shè)計人員應(yīng)仔細(xì)考量。這些注釋對HSSP代碼的某些限制進行了說明;不過,以下是簡短摘要。

■串行編程只能在5℃和50℃的溫度范圍內(nèi)進行。

■HSSP程序不支持1.8V以下的電壓。

■編程過程僅在一個電壓范圍內(nèi)完成。如果器件初始電壓為5.0V,則整個過程必須在5.0V范圍內(nèi)完成。

■SCLK的頻率存在上限。器件數(shù)據(jù)手冊的“交流電編程規(guī)范”部分指定了該頻率,以符號FSCLK標(biāo)出

電子發(fā)燒友App

電子發(fā)燒友App

評論