隨著通信與計算機整合時代的到來,數(shù)字化、寬帶化和智能化已成為未來通信發(fā)展的方向,人類社會對電信業(yè)務從質量到業(yè)務種類都提出越來越高的要求,而接入網(wǎng)作為電信網(wǎng)的重要組成部分,連接本地交換機與用戶,是整個電信網(wǎng)的毛細血管和瓶頸,實現(xiàn)數(shù)字化、寬帶化和業(yè)務綜合化的關鍵。 嵌入式系統(tǒng)是以應用為中心的硬件設計和面向應用的軟件產(chǎn)品開發(fā)為基礎的專用計算機系統(tǒng),廣泛應用于制造工業(yè)、過程控制、通信、儀器、儀表、汽車、船舶、航空、航天、軍事裝備、消費產(chǎn)品等領域。

在嵌入式系統(tǒng)中,板上通信接口是指用于將各種集成電路與其他外圍設備交互連接的通信通路或總線。下面將逐一說明常用的板上通信接口。

1. I2C總線

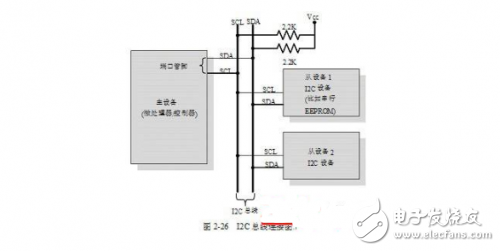

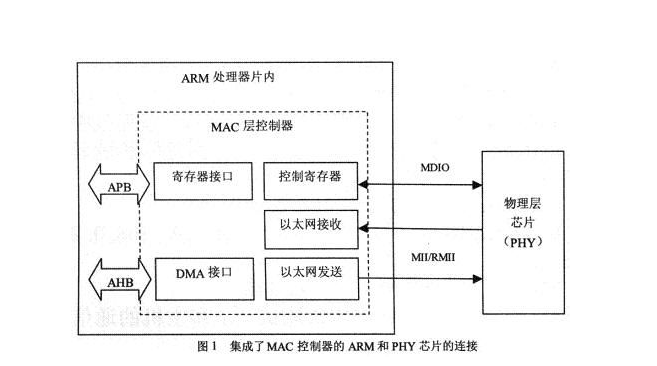

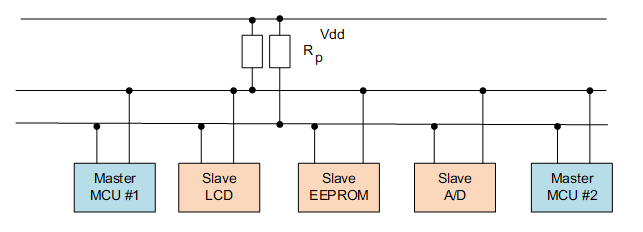

I2C總線是一種同步、雙向、半雙工的兩線式串行接口總線。這里,半雙工的含義是指在任意給定的時刻,只有一個方向上是可以通信的。I2C總線最早由Philips半導體公司于20世紀80年代研發(fā)面市。I2C最初的設計目標是為微處理器/微控制器系統(tǒng)與電視機外圍芯片之間的連接提供簡單的方法。I2C總線由兩條總線組成:串行時鐘線SCL和串行數(shù)據(jù)線SDA。SCL線負責產(chǎn)生同步時鐘脈沖,SDA線負責在設備間傳輸串行數(shù)據(jù)。I2C總線是共享的總線系統(tǒng),因此可以將多個I2C設備連接到該系統(tǒng)上。連接到I2C總線上的設備既可以用作主設備,也可以用作從設備。主設備負責控制通信,通過對數(shù)據(jù)傳輸進行初始化/終止化,來發(fā)送數(shù)據(jù)并產(chǎn)生所需的同步時鐘脈沖。從設備則是等待來自主設備的命令,并響應命令接收。主設備和從設備都可以作為發(fā)送設備或接收設備。無論主設備是作為發(fā)送設備還是接收設備,同步時鐘信號都只能由主設備產(chǎn)生。在相同的總線上,I2C支持多個主設備的同時存在。圖2-26顯示了I2C總線上主設備和從設備的連接關系。

基于輸入緩沖區(qū)和漏極開路晶體管(或者是集電極開路晶體管),可以構建I2C總線接口。當總線處于空閑狀態(tài)的時候,漏極開路晶體管(或者是集電極開路晶體管)處于懸空狀態(tài),輸出導線(SDA和SCL)為高阻態(tài)。為了使總線正常工作,應該使用上拉電阻,將兩條總線都上拉到供電電壓(TTL系列器件為+5V,CMOS系列器件為+3.3V)。上拉電阻通常取值為2.2K。使用上拉電阻,總線上輸出導線處于空閑狀態(tài)的時候,對應于高電平。

通過將設備地址線硬件連接到所需的邏輯電平上,可以分配I2C設備的地址。在嵌入式設備中,當設計嵌入式硬件的時候,需要分配各種I2C設備的地址并完成硬件連接。系統(tǒng)與I2C從設備通信的工作順序如下:

(1) 主設備將總線上的時鐘線(SCL)拉高到高電平。

(2) 當SCL線處于高電平邏輯(這是數(shù)據(jù)傳輸?shù)膯訔l件)的時候,主設備將數(shù)據(jù)線(SDA)拉低到低電平。

(3) 主設備通過SDA線,將從設備地址(具有7位或10位寬度)發(fā)送到通信目的地址。從設備會在SCL線上產(chǎn)生時鐘脈沖,用于同步位接收。需要說明的是,系統(tǒng)總是首先傳輸數(shù)據(jù)的MSB(最高位)。在時鐘信號處于高電平期間,總線中的數(shù)據(jù)是有效的。

(4) 根據(jù)需求,主設備發(fā)送讀位或寫位(位值等于1意味著讀操作,位值等于0意味著寫操作)。

(5) 主設備等待從設備發(fā)出確認位。在發(fā)送讀/寫操作命令的同時,從設備的地址也會發(fā)送到總線上。對于連接到總線上的從設備,會將接收到的地址與分配的地址進行比較。

(6) 如果從設備接收到來自主設備的指令并且地址正確,那么從設備通過SDA線發(fā)送確認位(值為1)。

(7) 主設備接收到確認位之后,如果操作指令是向設備寫入數(shù)據(jù),就通過SDA線向從設備發(fā)送8位數(shù)據(jù)。如果操作指令是從設備讀出數(shù)據(jù),從設備將通過SDA線將數(shù)據(jù)發(fā)送給主設備。

(8) 對于寫入操作,在字節(jié)傳輸結束之后,主設備等待從設備發(fā)送確認位;對于讀出操作,在字節(jié)傳輸結束之后,主設備向從設備發(fā)送確認位。

(9) 當時鐘線SCL處于邏輯高電平(表示停止)的時候,通過將SDA線拉高到高電平,主設備可以終止數(shù)據(jù)傳輸。

I2C總線支持三種不同的數(shù)據(jù)速率:標準模式(數(shù)據(jù)速率為100kb/秒,即100kbps)、快速模式(數(shù)據(jù)速率為400kb/秒,即400kbps)、高速模式(數(shù)據(jù)速率為3.4Mb/秒,即3.4Mbps)。第一代I2C設備設計所支持的數(shù)據(jù)速率只有100kbps,新一代I2C設備則能夠以高達3.4Mbps的數(shù)據(jù)速率工作。

2. SPI總線

SPI總線是同步、雙向、全雙工的4線式串行接口總線,最早由Motorola公司提出。SPI是由“單個主設備+多個從設備”構成的系統(tǒng)。需要說明的是:在系統(tǒng)中,只要任意時刻只有一個主設備是處于激活狀態(tài)的,就可以存在多個SPI主設備。為了實現(xiàn)通信,SPI共有4條信號線,分別是:

(1)主設備出、從設備入(Master Out Slave In,MOSI):由主設備向從設備傳輸數(shù)據(jù)的信號線,也稱為從設備輸入(Slave Input/Slave Data In,SI/SDI)。

(2)主設備入、從設備出(Master In Slave Out,MISO):由從設備向主設備傳輸數(shù)據(jù)的信號線,也稱為從設備輸出(Slave Output/Slave Data Out,SO/SDO)。

(3)串行時鐘(Serial Clock,SCLK):傳輸時鐘信號的信號線。

(4)從設備選擇(Slave Select,SS):用于選擇從設備的信號線,低電平有效。

圖2-27顯示了SPI總線上主設備和從設備的連接關系圖。

主設備負責產(chǎn)生時鐘信號,并通過將相應從設備的從設備選擇信號拉低為低電平,選通所需的從設備。在沒有選通的時候,所有從設備的數(shù)據(jù)輸出線MISO都懸空處于高阻態(tài)。

SPI總線上的串行數(shù)據(jù)傳輸是用戶可配置的。SPI設備包含特定的寄存器組,可以保存所需的配置。串行外圍設備的控制寄存器用于保存各種配置參數(shù),比如器件的主/從選擇、通信波特率的選擇、時鐘信號控制等。狀態(tài)寄存器則用于保存各種通信條件的狀態(tài),實現(xiàn)所需的數(shù)據(jù)傳輸和數(shù)據(jù)接收。

SPI的工作是基于移位寄存器的;為了實現(xiàn)數(shù)據(jù)傳輸或數(shù)據(jù)接收,主設備和從設備包含了專用移位寄存器。移位寄存器的長度取決于具體設備,通常是8的整數(shù)倍。數(shù)據(jù)在從主設備傳輸?shù)綇脑O備的過程中,主設備移位寄存器中的數(shù)據(jù)從MOSI管腳移出,然后通過從設備的MOSI管腳,輸入到從設備的移位寄存器中。與此同時,由從設備移位寄存器移位出來的數(shù)據(jù),通過MISO管腳,輸入到主設備的移位寄存器中。也就是說,主設備和從設備的移位寄存器構成了一個循環(huán)緩沖區(qū)。對于特定類型的器件,可以通過配置寄存器(比如,對于Motorola公司生產(chǎn)的68HC12型控制器,需要配置SPI控制寄存器的LSBF位),決定最先發(fā)送的數(shù)據(jù)位是最高位還是最低位。

與I2C總線相比,SPI總線更適于數(shù)據(jù)流傳輸。SPI的不足之處在于,SPI不支持數(shù)據(jù)確認機制。

3. UART

基于UART的數(shù)據(jù)傳輸是異步形式的串行數(shù)據(jù)傳輸。基于UART的串行數(shù)據(jù)傳輸不需要使用時鐘信號來同步傳輸?shù)陌l(fā)送端和接收端,而是依賴于發(fā)送設備和接收設備之間預定義的配置。對于發(fā)送設備和接收設備來說,兩者的串行通信配置(波特率、單位字的位數(shù)、奇偶校驗、起始位數(shù)與結束位、流量控制)應該設置為完全相同。通過在數(shù)據(jù)流中插入特定的比特序列,可以指示通信的開始與結束。當發(fā)送一個字節(jié)數(shù)據(jù)的時候,需要在比特流的開頭加上起始位,并在比特流的末尾加上結束位。數(shù)據(jù)字節(jié)的最低位緊接在起始位之后。

起始位用于告知接收設備:數(shù)據(jù)字節(jié)將要到達接收端。然后,接收設備按照設定的波特率,選中其數(shù)據(jù)接收線。如果波特率是x比特/秒,那么每個比特可用的時隙是1/x秒。接收設備會精確地在比特可用時隙一半的位置,定時選中數(shù)據(jù)接收線。如果通信使用了奇偶校驗功能,那么UART發(fā)送設備會在發(fā)送數(shù)據(jù)流中增加奇偶校驗位(取值為1,表示傳輸比特流中含有奇數(shù)個1;取值為0,則表示傳輸比特流中含有偶數(shù)個1)。UART接收設備計算接收到的數(shù)據(jù)位的奇偶校驗結果,并與接收到的奇偶校驗位進行比較。UART接收設備丟棄掉接收比特流中的起始位、結束位、奇偶校驗位,并將接收到的串行比特數(shù)據(jù)轉換成字(比如,考慮8比特對應于1個字節(jié)的情況,接收到8比特,最先接收到的數(shù)據(jù)位是LSB,最后接收到的數(shù)據(jù)位是MSB)。

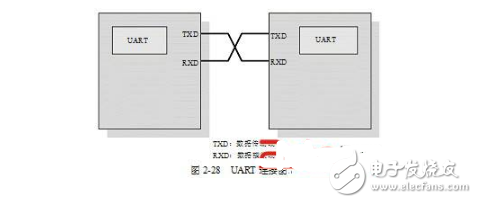

為了實現(xiàn)正確的通信,發(fā)送設備的數(shù)據(jù)傳輸線應該連接到接收設備的數(shù)據(jù)接收線上。圖2-28顯示了UART的連接圖。

除了串行數(shù)據(jù)傳輸功能以外,UART還可以為控制串行數(shù)據(jù)流提供硬件握手信號支持。很多半導體廠商都提供了相應的UART芯片。NaTIonal半導體公司生產(chǎn)的8250 UART是具有標準設置的UART,用于IBM PC的早期設計中。

如今,大多數(shù)微處理器/控制器都集成有UART功能,并為串行數(shù)據(jù)傳輸與接收提供內(nèi)置式的指令支持。

4. 1-Wire接口

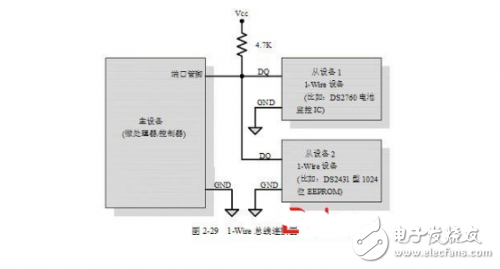

1-Wire接口是由Maxim Dallas半導體公司(首頁為)開發(fā)的異步半雙工通信協(xié)議,也稱為Dallas 1-Wire?協(xié)議。其中,按照主-從通信模型,只使用單條信號線DQ實現(xiàn)通信。1-Wire總線的一個重要特征在于,該總線允許在信號線上傳輸能量。I2C從設備在信號線上使用內(nèi)部電容器(其典型取值為800 pF)來驅動設備。1-Wire接口支持在總線上連接單個主設備以及一個或多個從設備。圖2-29顯示了1-Wire總線上主設備和從設備的連接關系圖。

每臺1-Wire設備都具有全球唯一可識別的64位識別碼信息,存儲在設備內(nèi)部。對于多臺從設備連接到1-Wire總線上的情況,通過解讀唯一的識別碼,可以尋址總線上存在的各***立設備。識別碼由以下三個部分組成:8位的類別碼、48位的序列號以及前56比特數(shù)據(jù)的8位CRC校驗結果。與1-Wire從設備通信的具體流程如下:

(1) 主設備將復位脈沖發(fā)送到1-Wire總線上。

(2) 總線上的從設備通過確認脈沖予以回應。

(3) 主設備發(fā)送ROM命令(網(wǎng)絡尋址命令,參數(shù)是設備的64位地址),從而尋址到需要發(fā)起通信的從設備。

(4) 主設備發(fā)送讀/寫命令,對從設備的內(nèi)部存儲器或寄存器進行讀/寫操作。

(5) 主設備將數(shù)據(jù)由從設備讀出,或者是將數(shù)據(jù)寫入從設備。

1-Wire總線上的所有通信都是由主設備發(fā)起的。其中,通信的最小間隔是時長為60微秒的時隙。復位脈沖占用8個時隙。在通信的開始階段,主設備將1-Wire總線拉低到低電平,并持續(xù)8個時隙(即480 μs),從而發(fā)出復位脈沖。如果總線上存在從設備,而且已經(jīng)準備好進行通信,那么從設備將通過確認脈沖來回應主設備;也就是說,從設備將1-Wire總線拉低到低電平,并持續(xù)1個時隙(即60 μs)。為了在1-Wire總線上寫入位值1,需要總線主設備將總線拉低,其持續(xù)時間為1~15 μs,然后在該時隙的其余時間段釋放總線。為了在總線上寫入位值0,主設備需要將總線拉低,其持續(xù)時間至少為1個時隙(60 μs),最多為2個時隙(120 μs)。為了由從設備讀出位值,主設備需要將總線拉低,并持續(xù)1~15 μs。為了響應主設備的讀數(shù)據(jù)請求,如果從設備想要發(fā)送位值1,那么從設備只需要在該時隙的其余時間段釋放總線;如果從設備想要發(fā)送位值0,那么從設備需要在該時隙的其余時間段將總線拉低。

電子發(fā)燒友App

電子發(fā)燒友App

評論