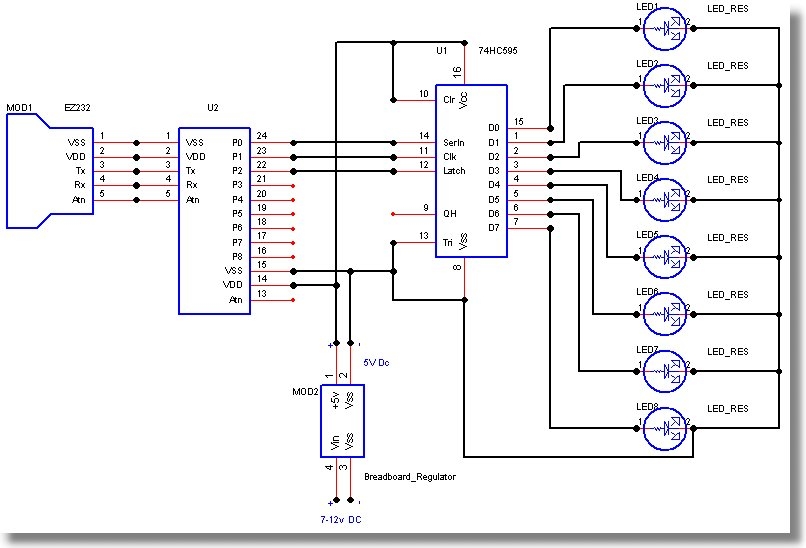

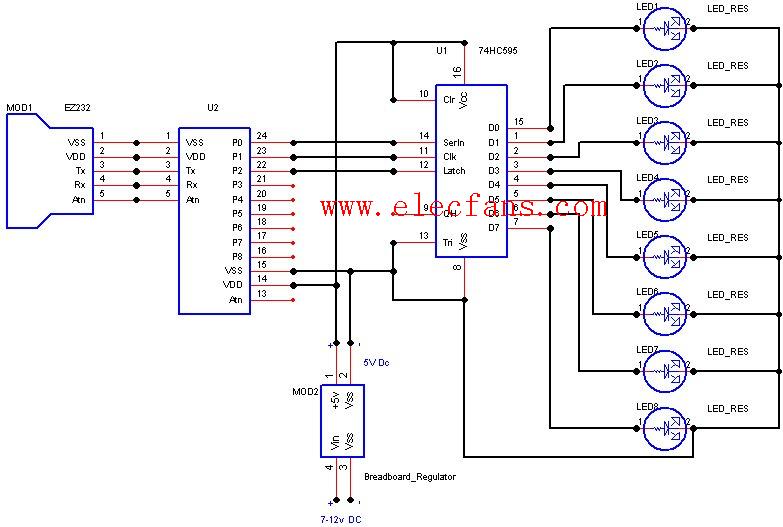

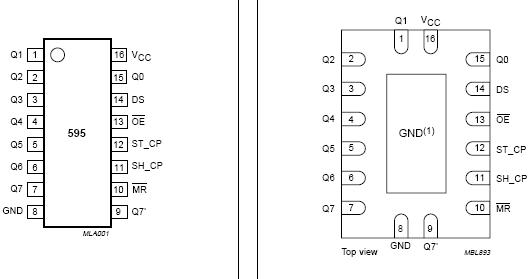

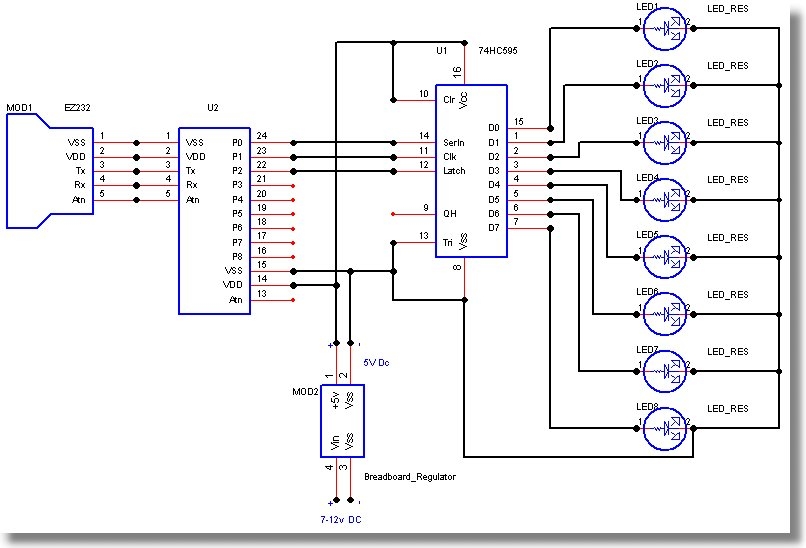

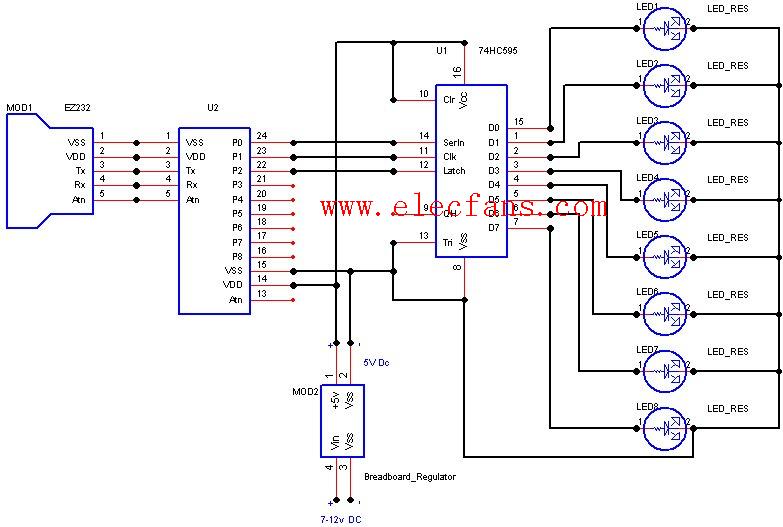

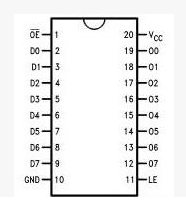

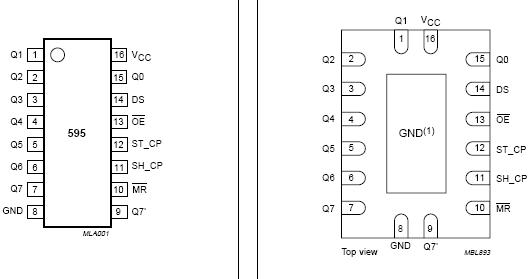

一、74HC595使用方法74HC595的數(shù)據(jù)端Q0--Q7:八位并行輸出端,可以直接控制數(shù)碼管的8個(gè)段。Q7:級(jí)聯(lián)輸出端。將它接下一個(gè)595的DS端。DS:串行數(shù)據(jù)輸入端,級(jí)聯(lián)的話接上一級(jí)的Q7

2021-12-07 06:46:57

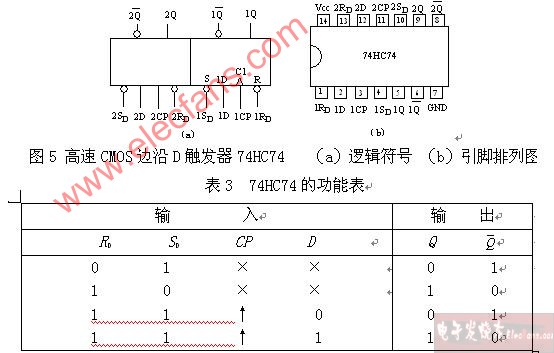

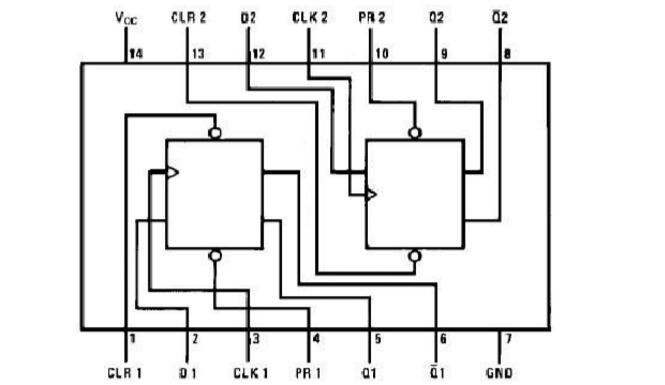

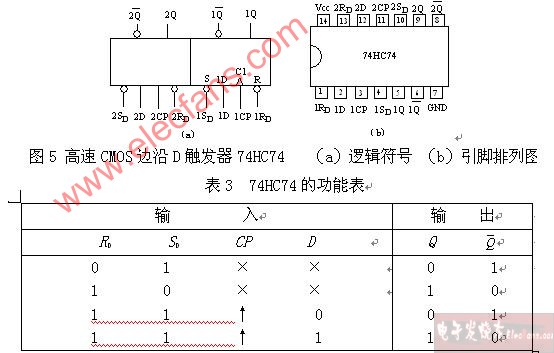

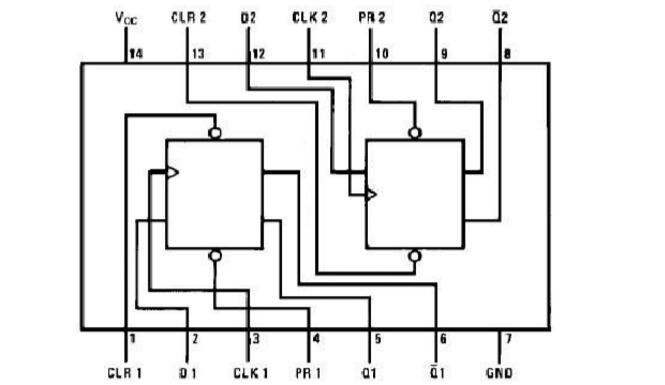

74HC74為單輸入端的雙D觸發(fā)器。一個(gè)片子里封裝著兩個(gè)相同的D觸發(fā)器,每個(gè)觸發(fā)器只有一個(gè)D端,它們都帶有直

2009-04-01 08:47:01 34879

34879

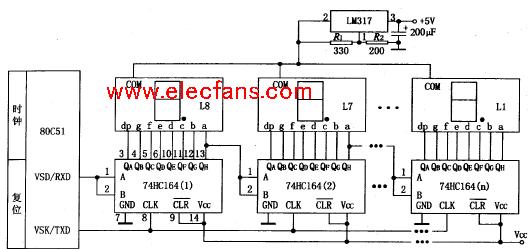

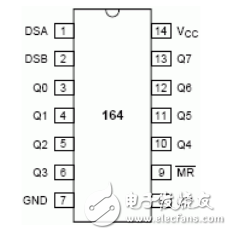

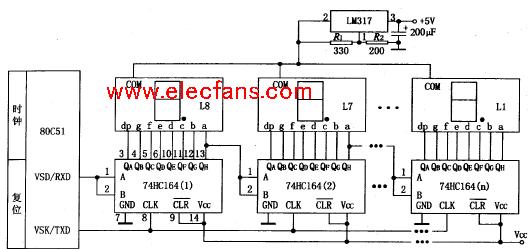

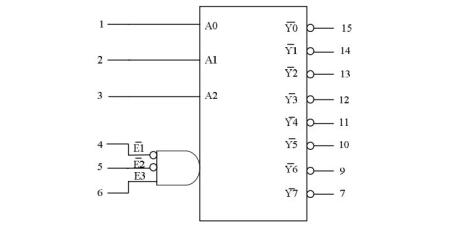

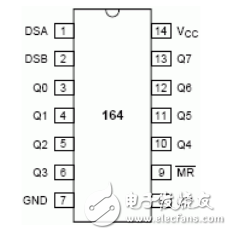

74hc164應(yīng)用電路

通過(guò)74HC164

2008-09-22 11:08:07 5448

5448

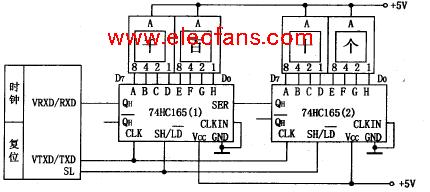

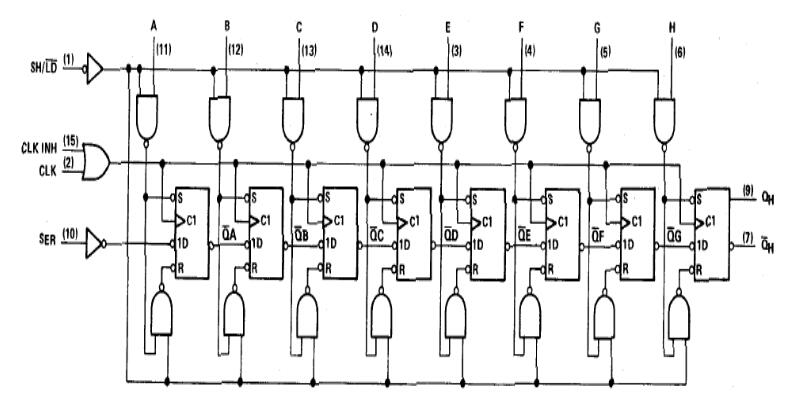

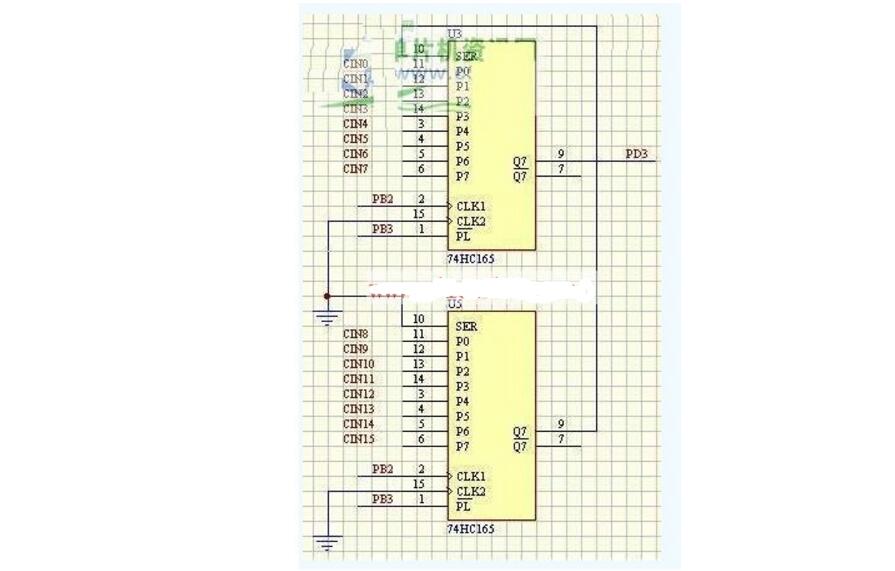

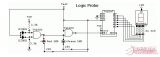

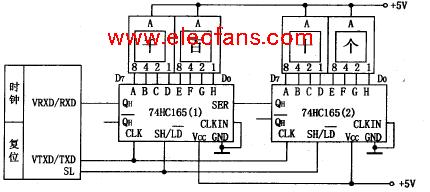

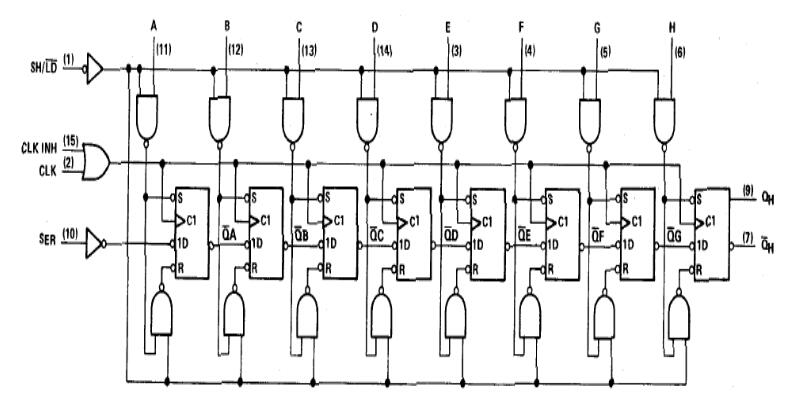

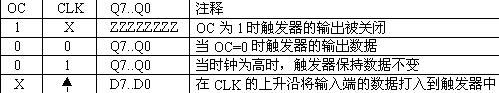

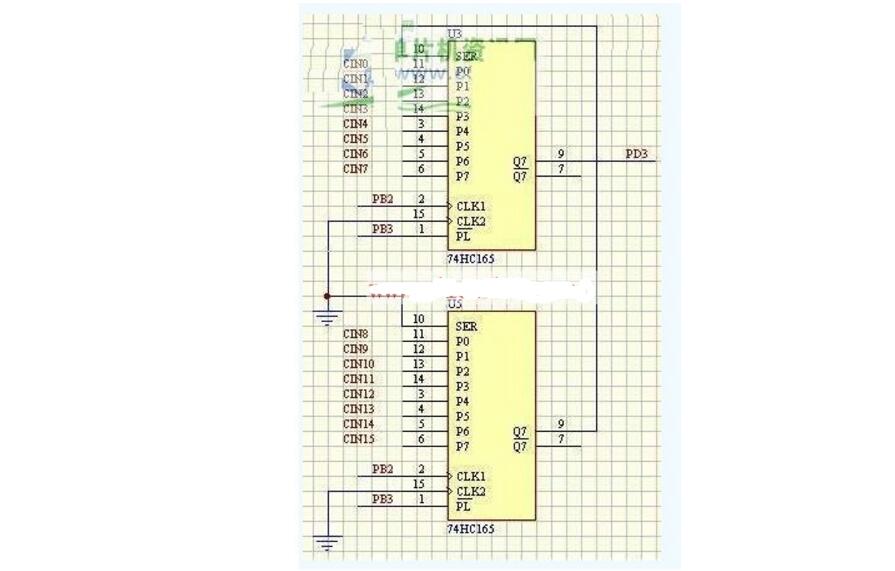

74hc165典型應(yīng)用電路

2008-09-22 11:02:24 7376

7376

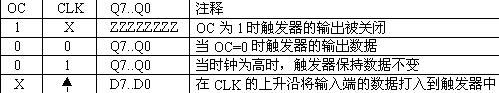

74hc595應(yīng)用電路

2008-01-12 00:04:08 3300

3300

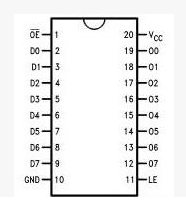

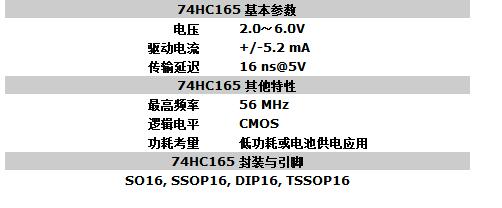

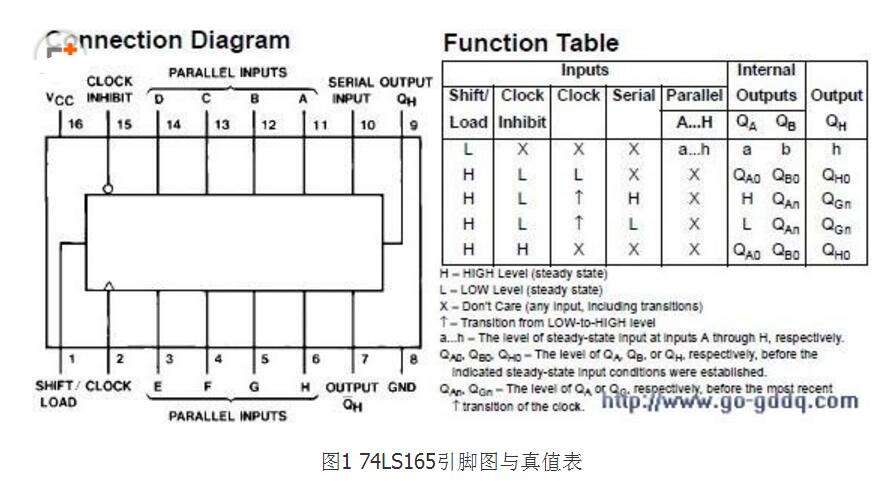

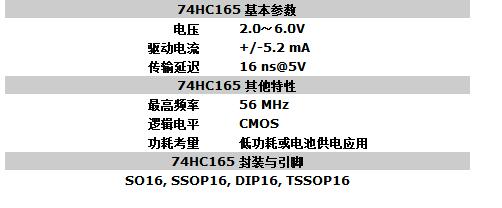

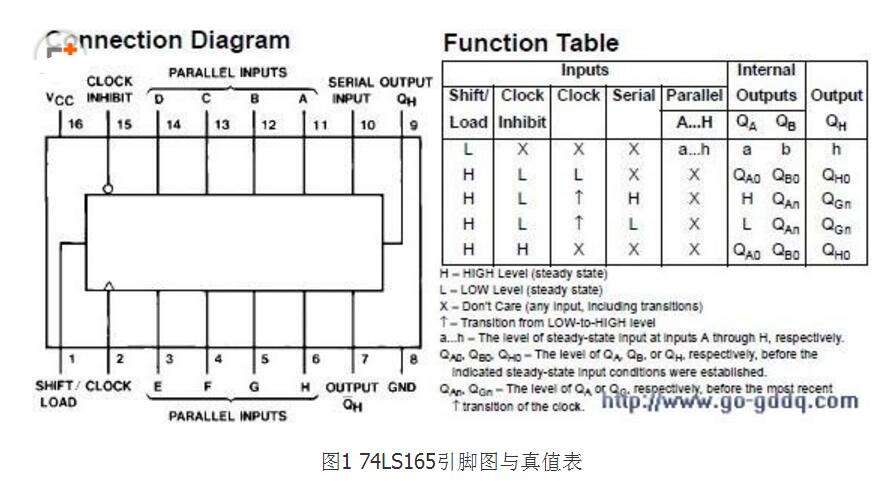

本文介紹了74hc165特性、74HC165邏輯圖、74hc165基本參數(shù)及真值表,其次介紹了74HC165時(shí)序圖、分析了74hc165工作原理與引腳圖及功能,最后接介紹了74HC165推薦工作條件與應(yīng)用電路。

2018-02-02 11:16:04 177680

177680

The 74HC/HCT74 is a high-speed Si-gate CMOS deviceand is pin compatible with low power Schottky TTL

2008-07-14 16:47:22 155

155 74HC574應(yīng)用電路原理圖

寄存器是一種重要的數(shù)字電路部件, 常用來(lái)暫時(shí)存放數(shù)據(jù)、指令等。一個(gè)觸發(fā)器可以存儲(chǔ)一位二進(jìn)

2009-04-01 14:59:55 18512

18512

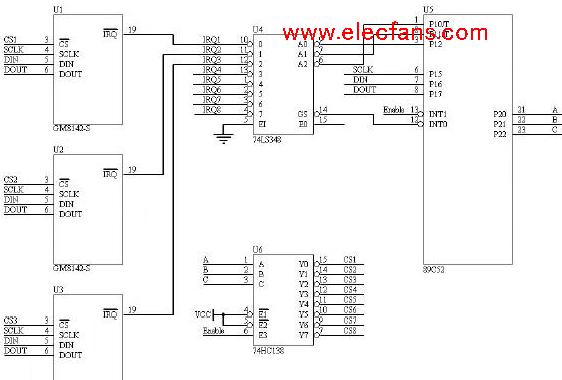

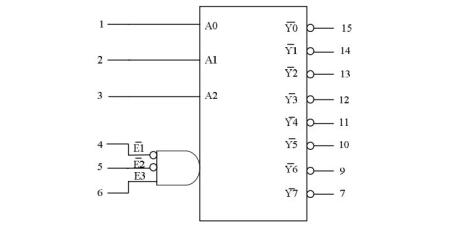

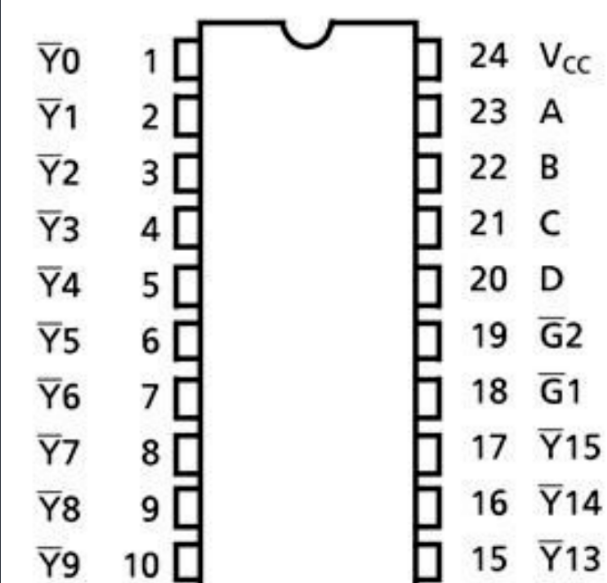

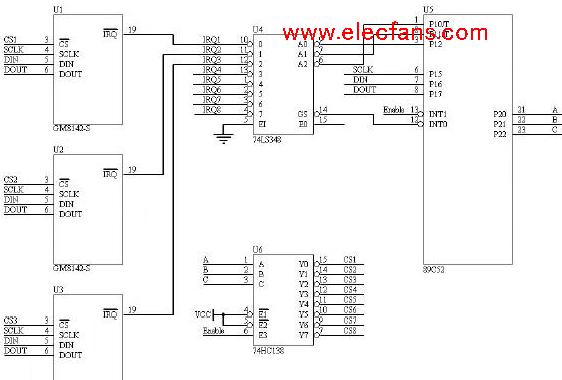

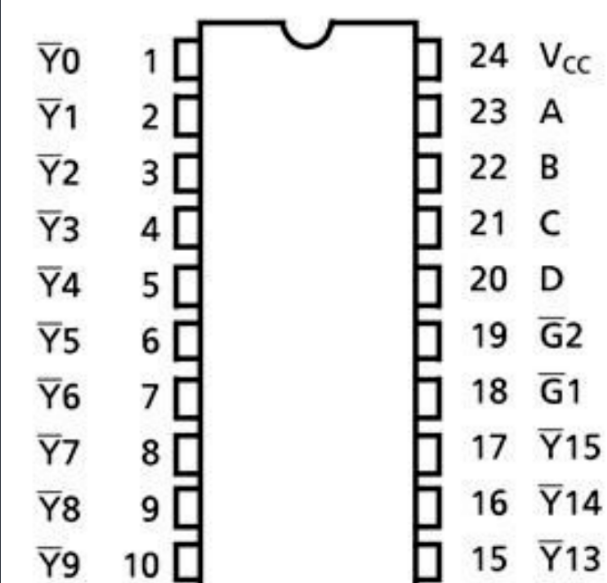

74HC138譯碼器應(yīng)用電路

2008-09-22 11:21:22 5940

5940

本文介紹了74HC138邏輯圖、74HC138功能、介紹了74HC138引腳圖及引腳功能,其次介紹了74HC138真值表、特性與電氣參數(shù),最后介紹了74HC138的封裝形式與應(yīng)用電路。

2018-02-02 16:01:39 277255

277255

本文主要介紹74hc595的主要功能(74hc595引腳圖及功能_工作原理及電壓_典型應(yīng)用電路)。應(yīng)用電路:74HC595驅(qū)動(dòng)LED的電路設(shè)計(jì)、基于74HC595流水燈設(shè)計(jì)。

2017-12-08 15:37:06 269966

269966

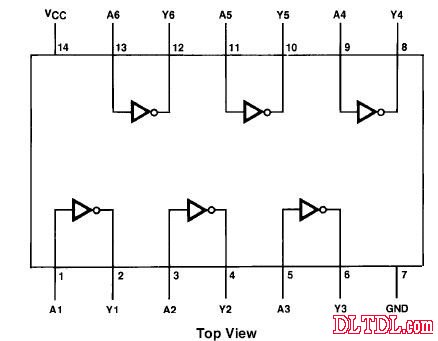

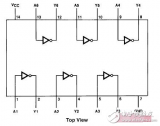

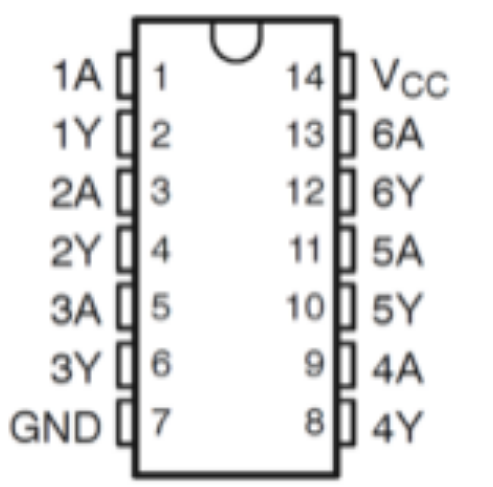

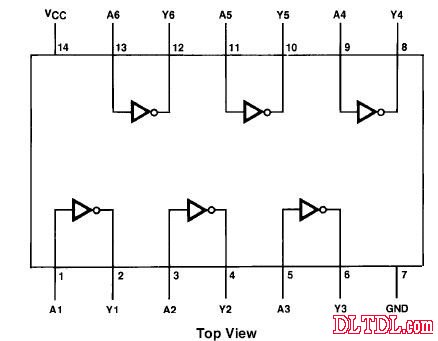

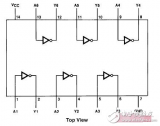

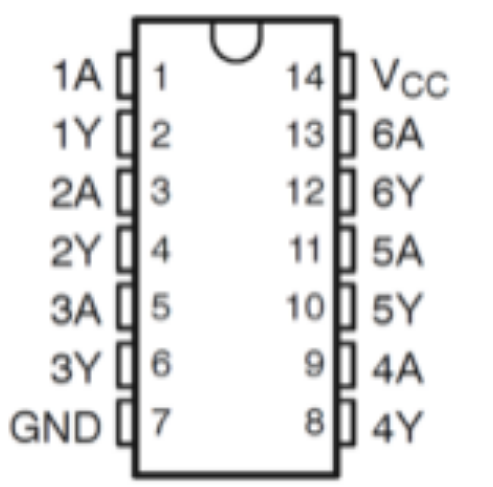

最全74HC04六反相器中文資料|引腳圖及功能表|應(yīng)用電路圖,該74HC04/74HCT04是高速CMOS器件,低功耗肖特基的TTL(LSTTL)電路 。功能作用:六反相器圖1 引腳-其他基礎(chǔ)電路圖

2022-05-26 08:59:05 11133

11133

74HC595程序應(yīng)用(附原理圖)

2012-08-10 09:11:11 136

136 本文首先介紹了74ls595和74hc595區(qū)別,其次闡述了74ls595的工作原理、引腳圖及功能、邏輯功能、電路圖,最后介紹了74ls595引腳圖及功能、應(yīng)用電路圖,具體的跟隨小編一起來(lái)了解一下。

2018-05-29 14:49:38 40596

40596

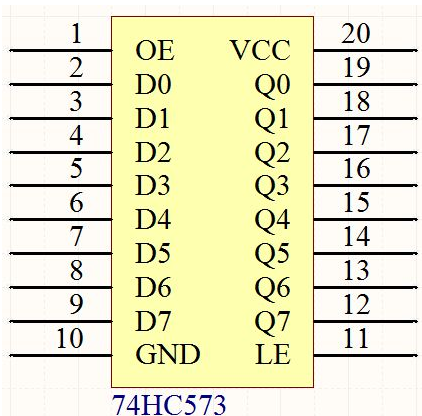

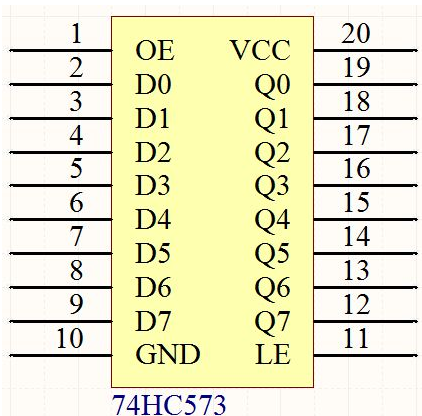

在實(shí)際應(yīng)用電路中74hc573和74hc595都可用,都可實(shí)現(xiàn)行掃描,看你電路怎么連接,程序如何編寫。

2018-07-27 14:27:07 24780

24780

74hc595電路圖

2008-04-07 15:21:54 5339

5339

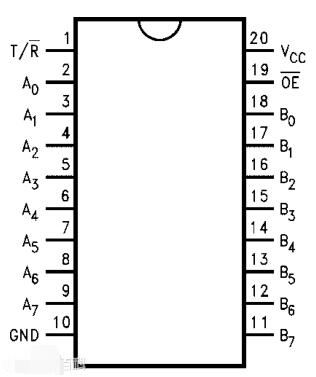

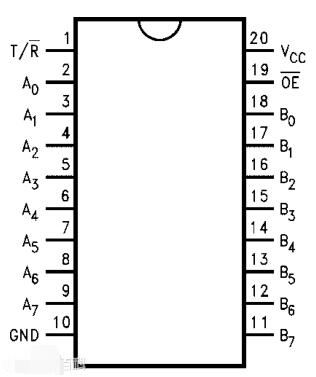

本文介紹了74hc245主要特性、引腳及功能介紹,74hc245建議操作條件,介紹了74hc245交流電氣特性,74hc245直流電氣規(guī)格以及74hc245封裝形式,最后介紹了74hc245真值表以及內(nèi)部電路圖,介紹工作原理方法及應(yīng)用電路。

2018-01-27 09:54:51 52611

52611

74ls14應(yīng)用電路圖:下圖為步進(jìn)電機(jī)驅(qū)動(dòng)器系統(tǒng)電路原理圖,有用到74LS14.

2008-06-08 09:08:12 5690

5690 本文檔的主要內(nèi)容詳細(xì)介紹的是高速CMOS器件74HC244的原理圖和封裝資料免費(fèi)下載。

2020-04-07 08:00:00 17

17 74HC165是一款高速CMOS器件,74HC165遵循JEDEC標(biāo)準(zhǔn)no.7A。74HC165引腳兼容低功耗肖特基TTL(LSTTL)系列。本文介紹了74HC165的級(jí)聯(lián)電路圖,介紹了74hc165使用方法與級(jí)聯(lián)程序。

2018-02-02 13:55:00 47384

47384

本文主要介紹了74hc164中文資料匯總(74hc164引腳圖及功能_特性參數(shù)及典型應(yīng)用電路)。74hc164是高速硅門CMOS電路,管腳與低功耗肖特基TTL(LSTTL)系列兼容。74hc

2018-04-04 14:24:08 101050

101050

74HC154是一款高速CMOS器件,74HC154引腳兼容低功耗肖特基TTL(LSTTL)系列。74HC154譯碼器可接受4位高有效二進(jìn)制地址輸入,并提供16個(gè)互斥的低有效輸出。

2018-07-19 09:50:37 20892

20892

74hc14與74hc14d的區(qū)別 74HC14與74HC14D都是集成電路型號(hào),這兩種型號(hào)的區(qū)別主要在于包裝形式和外延尺寸。 一、74HC14的介紹 74HC14是一款由NXP公司生產(chǎn)的CMOS

2023-08-18 11:14:34 886

886 本文主要介紹了74ls175是什么(74ls175引腳圖及功能_內(nèi)部結(jié)構(gòu)原理圖及應(yīng)用電路)。74ls175是常用的六D觸發(fā)器集成電路,里面含有6組d觸發(fā)器,可以用來(lái)構(gòu)成寄存器,搶答器等功能部件。下面具體看看74ls175的功能結(jié)構(gòu)。

2018-02-01 11:07:11 186783

186783

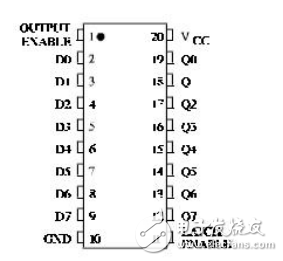

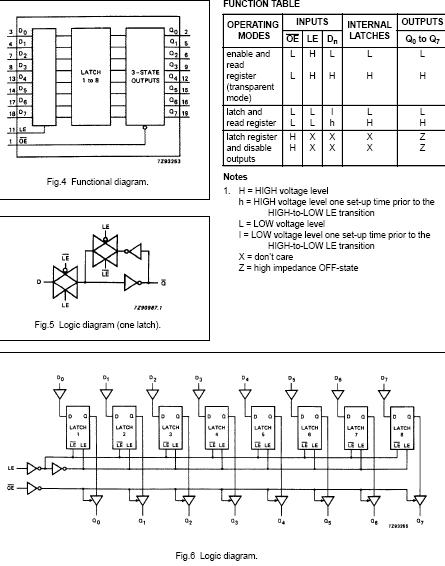

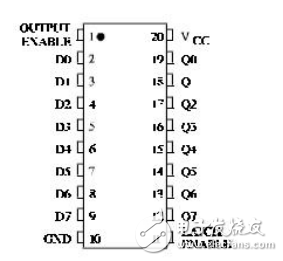

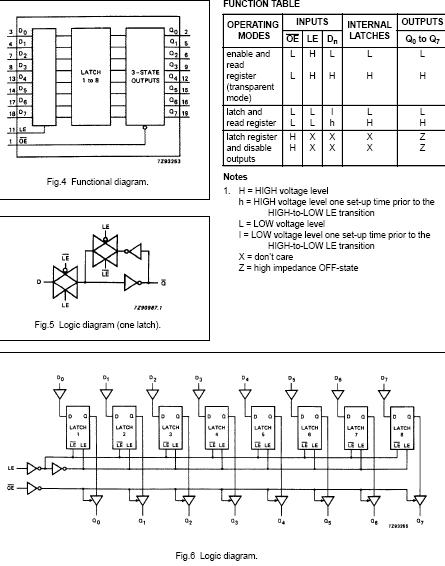

本文介紹了74hc573使用方法(74hc573引腳圖及功能_工作原理_封裝尺寸及應(yīng)用電路),74HC573的八個(gè)鎖存器都是透明的D型鎖存器,當(dāng)使能(G)為高時(shí),Q輸出將隨數(shù)據(jù)(D)輸入而變,適用于緩沖寄存器,I/O通道,雙向總線驅(qū)動(dòng)器和工作寄存器。

2017-12-08 17:10:03 301455

301455

MM54HC365/MM74HC365 Hex TRI-STATEÉ BufferMM54HC366/MM74HC366 Inverting Hex TRI-STATE

2008-08-06 09:53:45 37

37 TC74HC240,TC74HC244/TC74HC241 pdf datasheet

2008-10-24 10:11:33 33

33 HD74HC160/HD74HC161/HD74HC162/HD74HC163 數(shù)據(jù)表

2023-05-09 20:12:01 0

0 本文主要介紹了74ls04和74hc04有什么區(qū)別_74ls04/74hc04簡(jiǎn)介。74LS04是TTL電路的六反相器,工作電源電壓5V,74HC04是CMOS電路的六反相器,工作電源電壓

2018-04-08 11:34:31 24720

24720

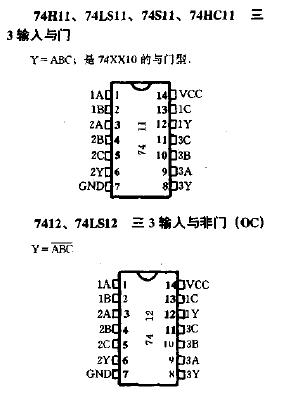

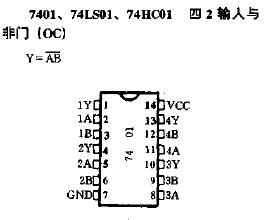

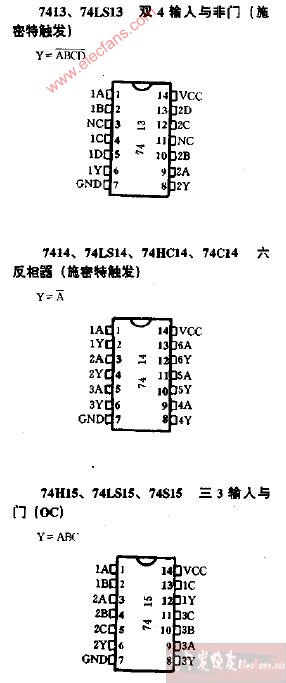

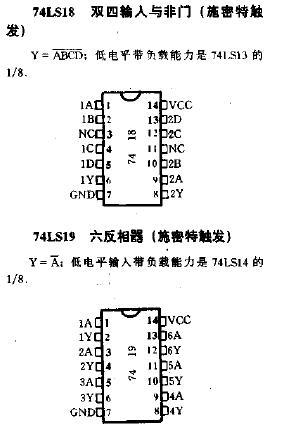

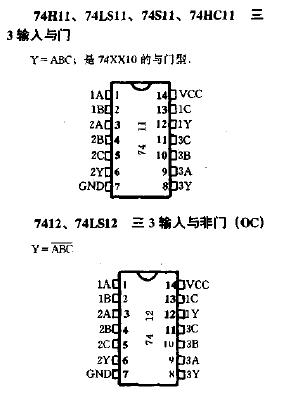

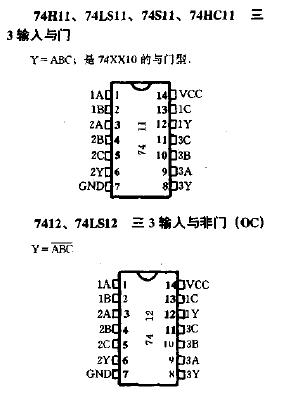

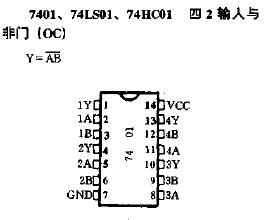

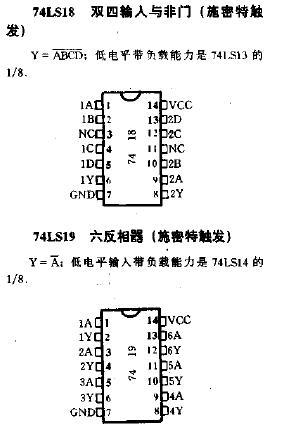

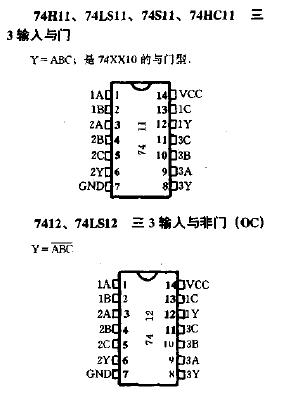

常用74系列,74LS,74HC系列邏輯門電路

2009-08-06 08:42:36 482

482 74HC573D是8位三態(tài)鎖存器,一般在實(shí)際應(yīng)用電路中用于地址或數(shù)據(jù)的鎖存。

2018-07-28 10:19:39 45695

45695

HD74HC160/HD74HC161/HD74HC162/HD74HC163 數(shù)據(jù)表

2023-06-28 19:01:56 0

0 HD74HC442 HD74HC443 HD74HC444 數(shù)據(jù)表

2023-06-27 19:14:25 0

0 HD74HC442 HD74HC443 HD74HC444 數(shù)據(jù)表

2023-05-08 19:34:43 0

0 74hc14與74hc04的區(qū)別? 在數(shù)字邏輯電路設(shè)計(jì)中,集成電路起著至關(guān)重要的作用。這些電路通常由許多晶體管和其他元器件組成,使得它們的設(shè)計(jì)和制造變得更加高效和簡(jiǎn)單。74HC14和74HC

2023-08-18 11:14:46 870

870 MM54HC74A/MM74HC74ADual D Flip-Flop with Preset and ClearGeneral DescriptionThe MM54HC74A/MM74HC74

2008-08-06 09:22:58 37

37 74HC165是一款高速CMOS器件。本文開(kāi)始介紹了74HC165參數(shù)與74hc165引腳及功能,其次介紹了74hc165內(nèi)部結(jié)構(gòu)圖與使用方法,最后介紹了74hc165時(shí)序圖與真值表。

2018-02-02 11:42:09 49360

49360

下面是關(guān)于74ls00的應(yīng)用電路圖

2017-10-26 11:56:10 23000

23000

74HC74A英文手冊(cè)

2016-11-02 16:32:59 10

10 74HC244是一款高速CMOS器件,74HC244引腳兼容低功耗肖特基TTL(LSTTL)系列。本文介紹了74hc244的特點(diǎn)、引腳功能、特性參數(shù)及封裝尺寸圖。

2017-12-21 10:52:37 21631

21631

74HC14是一款高速CMOS器件,74HC14引腳兼容低功耗肖特基TTL(LSTTL)系列。74HC14遵循JEDEC標(biāo)準(zhǔn)No.7A。74HC14實(shí)現(xiàn)了6路施密特觸發(fā)反相器,可將緩慢變化的輸入信號(hào)轉(zhuǎn)換成清晰、無(wú)抖動(dòng)的輸出信號(hào)。

2018-08-02 15:52:36 131425

131425

74LS165是并行輸入,串行輸出移位寄存器。本文主要介紹了三款74ls165應(yīng)用電路圖。

2018-05-08 08:55:49 15826

15826

基本電路的原理圖連接(DS18B20、蜂鳴器、雙色點(diǎn)陣、5軸步進(jìn)電動(dòng)機(jī)、CPU、74HC165鎖存器等實(shí)用電路圖)。

2016-04-14 15:56:51 14

14 74HC11/7411/74S11引腳功能管腳定義圖

2009-04-10 15:07:10 14756

14756

74LS01 74HC01 7401引腳功能管腳定義圖

2009-04-10 14:48:23 7832

7832

MM74HC 與 74LS、74S 和 74ALS 邏輯的比較

2022-11-14 21:08:32 2

2 74C15/74HC15/7415引腳功能管腳定義圖

2009-04-10 15:13:10 4594

4594

74LS19/74HC19/7419引腳功能管腳定義圖

2009-04-10 15:18:17 6701

6701

74HC74D文資料,很好的學(xué)習(xí)資料,快來(lái)下載吧

2016-01-18 18:09:11 29

29 d觸發(fā)器芯片有:

74HC74 74LS90? 雙D觸發(fā)器74LS74?

74LS364八D觸發(fā)器(三態(tài))

2008-01-22 12:42:33 43218

43218

74LS03/74HC03/7403引腳功能管腳定義圖

2009-04-10 14:51:27 7073

7073

74LS12/74HC12/7412引腳功能管腳定義圖

2009-04-10 15:08:26 6963

6963

本文主要探討了關(guān)于74hc573的使用方法以及74hc573能否仿真的問(wèn)題。

2018-07-26 15:48:21 15218

15218

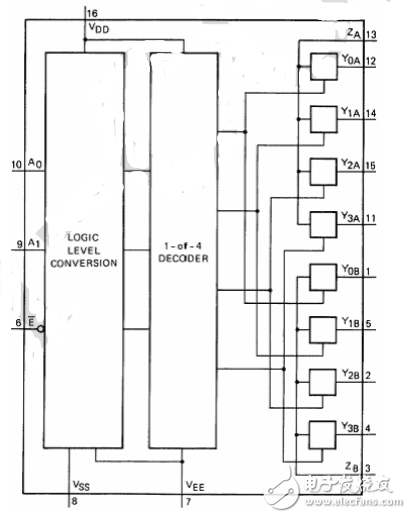

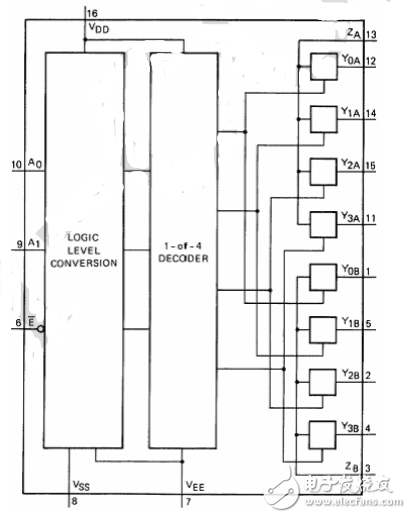

本文主要介紹了74hc4052中文資料匯總(74hc4052引腳圖及功能_工作原理及應(yīng)用電路),74HC4052是一塊帶有公共使能輸入控制位的2路四選一模擬開(kāi)關(guān)電路。每一個(gè)多路選擇開(kāi)關(guān)都有四個(gè)獨(dú)立

2018-04-04 15:53:14 141196

141196

HCT14要短。而74HCT14則是CMOS TTL兼容系列,具有輸入電平接近0V和5V(VCC)的特點(diǎn),且其輸出阻抗非常小。因此,對(duì)于高頻計(jì)數(shù)器和時(shí)序電路的設(shè)計(jì),74HC14更為

2023-08-18 11:14:39 536

536 SN74HC14PWLE中文資料

詳細(xì)解說(shuō)了斯密特觸發(fā)器的使用

2016-12-20 22:47:08 14

14 74hc373引腳圖

74hc373真值表和74HC373邏輯功能圖

2008-04-07 23:52:18 23700

23700

本文首先介紹了74ls74引腳圖及功能,其次介紹了邊沿D觸發(fā)器結(jié)構(gòu)與真值表,最后介紹了74ls74的三款應(yīng)用電路。

2018-04-28 12:42:40 554052

554052

74hc595引腳圖

引腳說(shuō)明

2008-01-11 23:59:31 34795

34795

74HC14與74AC14的區(qū)別 74HC14和74AC14是兩種常見(jiàn)的集成電路,在電子設(shè)計(jì)和制造中廣泛使用。這兩種器件都是由六個(gè)反相器構(gòu)成的,可用于多種應(yīng)用,包括振蕩器、閃爍器、計(jì)時(shí)器等等。盡管

2023-08-18 11:14:36 422

422 HD74HC4052 HD74HC4053 數(shù)據(jù)表

2023-06-27 19:15:34 0

0 HD74HC540 HD74HC541 數(shù)據(jù)表

2023-06-27 19:14:39 0

0 HD74HC668 HD74HC669 數(shù)據(jù)表

2023-06-27 19:13:30 1

1 HD74HC157/HD74HC158 數(shù)據(jù)表

2023-05-09 20:11:42 0

0

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論