Altera MAX+plus II 介紹

一、軟件功能簡介

MAX+plusⅡ(Multiple Array and Programming Logic User System)開發工具

是美國Altera 公司推出的一種EDA 工具,具有靈活高效,使用便捷,易學易用

的特點。Altera 公司在推出各種CPLD 和FPGA 的同時也在不斷地升級相應的開

發工具軟件,已從早期的第一代A+plus、第二代MAX+plus 發展到目前的第三

代MAX+plus II 和第四代Quartus。使用MAX+plus Ⅱ軟件,設計者無需精通器

件內部的復雜結構,只需熟悉所用的設計輸入工具,如硬件描述語言、原理圖等

進行輸入,MAX+plusⅡ自動將設計轉換成目標文件下載到器件中去。

MAX+plusⅡ開發系統具有以下特點。

(1)多平臺系統 MAX+plusⅡ的設計輸入、處理與校驗功能一起提供了全集

成化的可編程開發工具,可以加快動態調試,縮短開發周期。

(2)開放的界面 MAX+plusⅡ可與其它工業標準的設計輸入、綜合和校驗工

具鏈接。具有EDIF,VHDL,Verilog HDL 以及其他的網表接口,便于與許多公

司的EDA 工具接口,包括Cadence,Mentor,Synopsys,Synplicity,Viewlogic

等公司提供的EDA 工具的接口。

(3)模塊組合式工具軟件MAX+plusⅡ具有一個完整的可編程邏輯設計環境,

包括設計輸入、設計處理、設計校驗仿真和下載編程四個模塊,設計者可以按設

計流程選擇工作模塊。

(4)與結構無關 MAX+plusⅡ支持Altera 的Classic、MAX5000、MAX7000、

FLEX8000、FLEXlOK 等可編程器件系列,提供工業界中唯一真正與結構無關的

可編程邏輯設計環境。

(5)硬件描述語言 MAX+plusⅡ支持各種HDL 硬件設計輸入語言,包括VHDL、

VerilogHDL 和Altera 的硬件描述語言AHDL。

二、軟件的安裝使用說明

MAX+plus II 教學版軟件是免費的,你需要到Altera 公司的網頁去申請一

個License.dat 授權文件(軟件安裝部分有詳細說明),也可使用隨機光盤的

License.dat 授權文件(此文件就在光盤中的Altera MAX+plusII 10.0 文件下)。其

商業版需要到Altera 公司的中國代理購買,它帶有一個軟件狗,需置于計算機的

并行口上。教學版軟件同樣支持功能仿真和時序分析,并且同樣支持VHDL 語

言設計。該軟件可運行在Windows9X/2000/NT 及WindowsXP 操作系統下。

MAX+plusII 10.0 版本推薦PC 機的配置如為:333MHz 奔騰以上CPU、64M 以

上有效內存、600M 以上的硬盤。

1、 軟件的安裝

注意:本安裝過程以10.0 版本為例介紹,其它版本安裝過程類似。

⑴ 將光盤插入PC 機光驅,假定您的光驅號為G:,

⑵ 運行G:\MAX+plusII 10.0\setup.exe 文件,按提示進行安裝;

⑶ 安裝過程中閱讀完授權窗口信息后,選擇YES 接受協議,再選擇適當的安裝

方式,教學版軟件請選擇: full installation 模式安裝,若改變安裝目錄及路徑請按

Browse 按鈕修改,一般選擇默認安裝即可。軟件安裝完畢后,readme 文件將自

動出現,它包含一些重要信息,請仔細閱讀,該軟件要通過License 文件設置以

后方可使用(見下一節介紹)。

2、軟件的第一次使用與設置

MAX+plusII 10.0 軟件安裝完畢后,第一次運行軟件必須進行license.dat 文件的

設置,否則其大部分功能用戶不能正常使用。下面我們將license.dat 文件的安裝

方法簡單介紹如下。

1)、將光盤里隨機附送的license.dat 文件拷貝至安裝后的MAX+plus2 軟件包根

目錄下。注意:license.dat 文件來自于Altera 網上授權或代理商提供。也可使用

隨機光盤提供的License.dat 授權文件(此文件就在光盤中的Altera MAX+plusII

10.0 文件夾下)。

2)、點擊windows 程序組下的altera\ MAX+plusII 10.0 ,啟動本軟件。注意:第一次啟動軟件會有幾個對話窗口,提示沒有安裝License 文件或軟件狗,并附

有其公司網址及如何申請license 授權文件等詳細說明。

3)、軟件啟動以后選擇主菜單欄的Option \License Setup 選項,彈出如下對話框,

點擊 “Browse”;

4)、通過瀏覽,在如下對話框中指出您保存的License.dat 文件的所在硬盤位置

(路徑),點擊OK 確認即可。這樣您的MAX+plusII 軟件就可以正常使用了。

license.Dat 文件生效后,對話框底部的System lnfo 中就有你的硬盤ID 信息了,

如下圖所示。至此您已成功地完成了整個軟件的安裝。

說明:一般免費注冊申請的License.dat 文件只能用六個月的時間,如果到期的

話,您可以用同樣的方法再次申請,如果您使用的通用License.dat 文件(此文件

就在光盤中的Altera MAX+plusII 10.0 文件下),就不存在上述問題了,如果您在

安裝和使用本軟件中遇到問題,請及時與我們聯系。

三、可編程邏輯器件設計流程簡介

可編程邏輯器件CPLD/FPGA 的設計是指利用開發軟件和編程工具對器件

進行開發的過程。

可編程邏輯器件的設計流程包括設計準備、設計輸入、設計處理(項目編譯)、

仿真和定時分析、器件編程下載(設計實現)四個步驟。

三、MAX+plus II 可編程設計流程

1) 設計準備在對可編程邏輯器件的芯片進行設計之前,首先要進行方案論證、

系統設計和器件選擇等設計準備工作。設計者首先要根據任務要求,如系統所完

成的功能及復雜程度,對工作速度和器件本身的資源、成本及連線的可布通性等

方面進行權衡,選擇合適的設計方案。

在前面已經介紹過,數字系統的設計方法通常采用從頂向下的設計方法,也是基

于芯片的系統設計的主要方法,它首先從系統設計入手,在頂層進行功能劃分和

結構設計,采用硬件描述語言對高層次的系統進行描述,并在系統級采用仿真手

段,驗證設計的正確性,然后再逐級設計在低層的結構。

由于高層次的設計與器件及工藝無關,而且在芯片設計前就可以用軟件仿真手段

驗證系統方案的可行性,因此自頂向下的設計方法,有利于在早期發現結構設計

中的錯誤,避免不必要的重復設計,提高設計的一次成功率。自頂向下的設計采

用功能分割的方法從頂向下逐次進行劃分,這種層次化設計的另一個優點是支持

模塊化,從而可以提高設計效率。

2)設計輸入

設計者將所設計的系統或電路以開發軟件要求的某種形式表現出來,并送入

計算機的過程稱為設計輸入。設計輸入通常有以下幾種方式。

1).原理圖輸入方式

2).硬件描述語言輸入方式

3).波形輸入方式

4).層次化設計輸入方式

4、項目編譯(設計處理)

這是器件設計中的核心環節。在設計處理過程中,編譯軟件將對設計輸入文

件進行邏輯化簡、綜合和優化,并適當地用一片或多片器件自動進行適配,最后

產生編程用的編程文件。

1).語法檢查和設計規則檢查

設計輸入完成之后,在編譯過程首先進行語法檢驗,如檢查原理圖有無漏連

信號線,信號有無雙重來源,文本輸入文件中的關鍵字有無輸入錯誤等各種語法

錯誤,并及時列出錯誤信息 報告供設計者修改;然后進行設計規則檢驗,檢查

總的設計有無超出器件資源或規定的限制 并將編譯報告列出,指明違反規則情

況以供設計者糾正。

2).邏輯優化和綜合

化簡所有的邏輯方程或用戶自建的宏,使設計所占用的資源最少。綜合的目

的是將多個模塊設計文件合并為一個網表文件,并使層次設計平面化(即展平)。

3).適配和分割

確定優化以后的邏輯能否與器件中的宏單元和I/0 單元適配,然后將設計

分割為多個便于適配的邏輯小塊形式映射到器件相應的宏單元中。如果整個設計

不能裝入一片器件時,可以將整個設計自動分(分割)成多塊并裝入同一系列的多

片器件中去。

劃分(分割)工作可以全部自動實現,也可以部分由用戶控制,還可以全部由

用戶控制進行。劃分時應使所需器件數目盡可能少,同時應使用于器件之間通信

的引線端子數目最少。

4).布局和布線

布局和布線工作是在設計檢驗通過以后由軟件自動完成的,它能以最優的方

式對邏輯元件布局,并準確地實現元件間的互連。布線以后軟件會自動生成布線

報告,提供有關設計中各部分資源的使用情況等信息。

5).生成編程數據文件

項目編譯的最后一步是產生可供器件編程使用的數據文件。對CPLD 來說,是產

生熔絲圖文件,即JEDEC 文件(電子器件工程聯合制定的標準格式,簡稱JED 文

件);對于FPGA 來說,是生成位數據文件(BitstreamGeneration)。

4、仿真和定時分析(項目校驗):

設計項目的校驗包括設計項目的仿真(功能仿真)、定時分析兩個部分。一

個設計項目在編譯完成后只能為項目創建一個編程文件,但并不能保證是否真正

達到了用戶的設計要求,如邏輯功能和內部時序要求等。所以在器件編程之前應

進行全面模擬檢測和仿真調試,以確保其設計項目在各種可能的情況下正確響應

和正常工作,這就是項目校驗(仿真調試)的必要性。

MAX+plusⅡ提供的設計校驗過程包括仿真和定時分析,項目編譯后,為確保設

計無誤,再用專門軟件進行仿真。如果發現了錯誤,則對設計輸入進行部分修改

直至無誤。

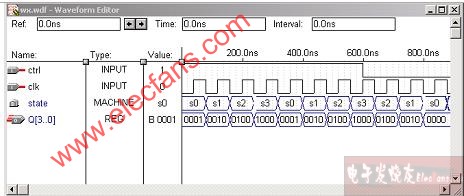

1)仿真(Simulation) MAX+plusII Simulator(仿真器)具有很強的靈活性,可以控制

對單個器件或多個器件設計的仿真。該模擬程序使用編譯過程中生成的二進制模

擬網表文件,對一個設計實現功能仿真和時序仿真。

設計者可以直接用矢量輸入語言來定義輸入激勵,也可以用MAX+plus ⅡWave

Editor 直接繪制波形。仿真結果在WaveEditor 或TextEditor 窗口顯示,也可作為

波形或文本文件打印出來。

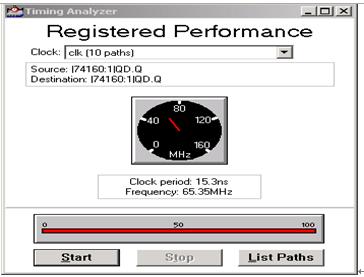

2)定時分析(TimingAnalysis) MAX+plus TimiⅡ ngAnalyzer(定時分析程序)能按

矩陣方式計算設計中點到點的延時,確定在器件引線端上要求的上升和保持時

間,估計最大時鐘頻率。MAX+plusⅡ設計輸入工具與定時分析程序綜合在一起,

允許在設計文件中簡單地指定起始和終點標記,或者用FloorplanEditor(平面圖編

輯器)來確定最短和最長的傳播延時。

五、器件編程下載

在以上步驟都正確實施并完全通過以后,我們就可以將我們設計的項目(最

終的數據編程文件)下載到器件中去,然后加入實際的激勵信號進行測試,在我

們的目標系統中進行產品級使用了。如果還未最終達到我們的設計目的,則需返

回以上步驟查找設計問題直至無誤。至此,我們已經完整的完成了可編程邏輯器

件的產品級設計流程,相信用戶通過對以上步驟的了解,對可編程邏輯器件的設

計有了一定的概念和了解。(有關器件下載編程配置的詳細使用說明見

MAX+plusII 軟件設計與應用舉例章節。)

六、可編程邏輯常用設計輸入法介紹

MAX+plus II 的設計輸入方法有多種,主要包括文本設計輸入、原理圖輸入、

波形設計輸入、層次設計輸入和平面圖設計輸入等多種方式,另外,還可以利用

第三方EDA工具生成的網表文件輸入,該軟件可接受的網表有EDIF格式、VHDL

格式及Verilog 格式。設計者可根據實際情況靈活地使用最適合自己的設計方法。

下面我們將用幾種最常見的輸入法加以介紹。

1、原理圖設計輸入法

這是一種最直接的輸入方式,它使用軟件系統提供的元器件庫及各種符號和

連線畫出原理圖,形成原理圖輸入文件。這種方式大多用在對系統及各部分電路

很熟悉的情況,或在系統對時間特性要求較高的場合。當系統功能較復雜時,原

理圖輸入方式效率低,它的主要優點是容易實現仿真,便于信號的觀察和電路的

調整。

1)、軟件的啟動:進入Altera 軟件包,打開MAX+plus II 10.0 軟件,如下圖所示。

2)、啟動File \ New 菜單,彈出設計輸入方式選擇窗口,如下圖所示:

3)、選擇Graphic Editor File,單擊OK 按鈕,打開原理圖編輯器,進入原理圖設

計輸入電路編輯狀態,如下圖所示:

4)、放置一個器件在原理圖上

a.在原理圖編輯器的空白處雙擊鼠標左鍵或單擊鼠標右鍵,在彈出的快捷菜單

中選擇Enter Symbol,出現下圖;

b.在上圖光標處可直接輸入元件名稱或用鼠標點取元器件庫中的所需元件,按下

OK 即可輸入元器件,下面我們將以3-8 譯碼器為例加以說明。

c.如果安放相同元件,只要按住Ctrl 鍵,用鼠標拖動所選中的元件復制到指定位

置即可。

d.一個完整的電路包括:輸入端口INPUT、電路元器件集合、輸出端口OUTPUT。

下圖為3-8 譯碼器的電路元件安放結果。

5)添加連線:

把鼠標移到元件引腳附近,則鼠標光標自動由箭頭變為十字連線狀態,按住鼠標

左鍵拖動,即可畫出連線,如果放開鼠標左鍵則一條連線就畫好了(一條連線也

可叫做一個節點,在原理圖編輯中節點是以線出現的)。3-8 譯碼器原理圖如下圖

所示。

6)標記輸入/輸出端口屬性

分別雙擊輸入端口的“PIN-NAME”,當其變成黑色時,即可輸入標記符名稱并回

車確認;輸出端口標記方法類似。本譯碼器的三輸入斷分別標記為:A、B、C;

其八輸出端分別為:D0、D1、D2、D3、D4、D5、D6、d7。如下圖所示。注意,

端口名字不能為空。

7)保存原理圖

單擊保存按鈕圖標,對于新建文件,出現類似文件管理器的圖框,請選擇保存路

徑和文件名稱,原理圖的擴展名為*.gdf 。

8)點擊File\Project\set project to current file 設置此項目為當前文件,如下圖所示。

注意:此操作尤為重要,否則容易出錯。

至此,你已完成了電路原理圖設計輸入的整個過程。當然在使用這種輸入法的時

候,有很多小技巧,如總線的使用等,這里將不再作詳細介紹。

2、文本設計輸入(VHDL)法簡介

文本設計輸入法,這種輸入法就是將電子電路的設計以文字(專用計算機語

言)或文件的形式表現出來,即硬件描述語言,它可分為普通硬件描述語言和行

為描述語言。普通硬件描述語言有ABEL-HDL、CUPL 等,它們支持邏輯方程、

真值表、狀態機等邏輯表達方式。行為描述語言是目前常用的高層次硬件描述語

言,有VHDL 和Verilog-HDL 等,它們都已成為IEEE 標準,并且有許多突出的

優點:如語言與工藝的無關性,可以使設計者在系統設計、邏輯驗證階段便能確

立方案的可行性;如語言的公開可利用性,使它們便于實現大規模系統的設計等;

同時硬件描述語言具有較強的邏輯描述和仿真功能,而且輸入效率高,在不同的

設計輸入庫之間轉換和移植非常方便,通用性很強。因此,運用VHDL、

Verilog-HDL 硬件描述語言設計已是當前的趨勢,下面我們將以VHDL 語言為例

作一簡單介紹。

1)、在主菜單上選擇File\New 或點擊新建快捷圖標,在彈出的菜單中選擇TextEditer File,按下OK 按鈕, 即可輸入文本,現已“Adder”加法器為例,進行VHDL

語言設計輸入,在下面的文本編輯器中輸入該描述語言,如下圖所示。

2)、設計輸入完成以后,在主菜單上選擇File \Save 或點擊保存文件快捷圖標,

彈出如下對話框,請注意文件格式。

3)、選擇文件類型為 •VHD 硬件描述語言,輸入文件名稱“adder”,點擊OK 按

鈕保存文件。再選擇file/project/set project to current file 設置這個項目為當前的項

目文件。

4)、編譯我們所設計的項目,從下圖可以看出其編譯沒有任何錯誤,可以說明此

版本軟件支持VHDL 硬件描述語言設計輸入,有興趣的讀者可以對該項目試著

仿真一下,以得到進一步的驗證。

3、波形輸入法簡介

波形輸入主要用于建立和編程波形設計文件以及輸入仿真向量和功能測試

向量,從而達到對電路的設計實現。

波形設計輸入適合用于時序邏輯和有重復性的邏輯函數。系統軟件可以根據

用戶的輸入 輸出波形自動生成邏輯關系。

波形編輯功能還允許設計者對波形進行拷貝、剪切、粘貼、重復與伸展,從

而可以用內部節點、觸發器和狀態機建立設計文件,并將波形進行組合,顯示各

種進制的狀態值,還可以通過將一組波形重疊到另一組波形上,對兩組仿真結果

進行比較。下面我們將以一個非門為例加以簡單說明。

1)、按下圖方式打開新建波形文件窗口;

2)、按下圖方式分別輸入“input/output”管腳名稱in 和out;

3)、按下圖方式打開波形編輯窗口,用戶可以發現當您選中其輸入或輸出端

口標記時,左邊快捷工具欄的波形編輯工具被激活,這時我們就可以來按電路要

求編輯電路波形了。

4)、按下圖所示,添加邏輯波形。可以看出下面的輸入輸出波形結構實際上

就是非門這個電路用波形的形式來描繪和表現的;

5)、保存文件,注意選擇.wdf 擴展名,如下圖所示。再選擇file/project/set

project to current file 設置這個項目為當前的項目文件。

6)、編譯我們所設計的項目,從下圖可以看出 ,編譯完全正確,沒有語法

錯誤,這說明MAX+plus II 軟件支持波形設計輸入。

說明:有興趣的讀者可以試著把該項目仿真一下,有關編譯和仿真的詳細說

明請參考MAX+plus II 軟件設計與應用舉例章節。在這里提醒讀者一下,用波形

編輯設計輸入時,如果要仿真,請關閉上面所有窗口,然后再選擇File\open 打

開.sym 文件(即該項目自動生成的圖形文件)后再進行仿真,如下圖所示。具

體仿真方法請參考有關章節介紹。

4、層次化設計輸入法簡介:

當設計一個結構較復雜的系統時,采用層次化的設計方法,使系統設計變得

簡潔和方便。層次化設計是分層次、分模塊進行設計描述。描述器件總功能的模

塊放在最上層,稱為頂層設計;描述器件的某一部分功能的模塊放在下層,成為

底層設計。這種分層次的關系就類似于軟件設計分主程序和子程序的關系。層次

化設計的優點其一是支持模塊化,底層模塊可反復被調用,多個底層模塊可分別

由不同的設計者同時設計,從而提高了設計效率。其二是設計方法較自由,可以

采用自上而下或自下而上的設計方法。其三是同一個設計項目的各個模塊可以用

不同的設計輸入法來實現,團隊之間的合作就更加方便靈活,各自的模塊可以用

自己最熟悉的設計方法(語言)來編寫程序而相互不約束。

下面我們以一位全加器的設計為例,簡單介紹一下層次化的設計方法。一位全加

器的整個設計過程包括兩個模塊:底層半加器模塊(H_adder.vhd)、頂層全加器

模塊(F_adder.gdf)。讀者可以看出這兩個模塊是分別由VHDL 語言和原理圖兩

種方法來設計實現的。

1)、編寫底層半加器模塊H_adder.vhd,程序清單如下:

2)、將半加器項目編譯,并創建缺省符號H_adder.sym 。

3)、采用圖形輸入法輸入頂層的圖形文件F_adder.gdf。F_adder.gdf 是全加器設

計中的頂層圖形文件,調用了前面創建的符號H_adder.sym 和一個兩輸入或門,

組成一個設計實體,全加器頂層設計原理圖如下圖所示。

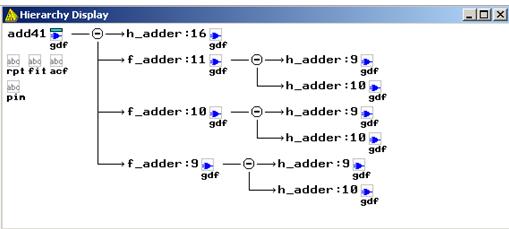

原理圖繪制完成后,就可以在項目的層次顯示窗口中觀察F_adder 的層次結構。

選擇菜單MAX+plus II\Hierarchy Display(層次顯示)或點擊其工具欄快捷按鈕

,打開層次顯示窗口,顯示出F_adder 設計項目的層次樹形結構,如下圖所

示。在上面的層次顯示窗口中可以看出全加器的頂層設計是一個.gdf 的圖形文

件,底層是兩個用VHDL 語言編寫的文本文件,只要我們雙擊這兩個模塊,就

可以看到我們底層設計的文本程序清單。通過以上的學習,相信用戶對可編程邏

輯器件設計的靈活性更加值得青睞。

五、MAX+plus II 軟件設計與應用舉例

說明:本書將以本例程為例詳細介紹altera 公司MAX+plusII 10.0 版本軟件的基

本應用,其它實驗將不再贅述。讀者通過對本實驗的應用舉例后將對MAX+plusII

軟件及CPLD/FPGA 的設計與應用有一個比較完整的概念和思路。此書因篇幅有

限,僅僅介紹了MAX+plusII 軟件的最基本、最常用的一些基本功能,相信讀者

在熟練使用本軟件以后,你定會發現該軟件還有好多非常方便、快捷、靈活的設

計技巧與開發功能。由于編者能力有限,不詳之處再所難免,我們希望得到你的

指正與包涵。

1、項目的設計輸入

各種設計輸入法的詳細使用請參考“設計輸入方法介紹”章節。

下面我們以3-8 譯碼器為例加以說明:

1、打開MAX+plus II 10.0 軟件,用原理圖方式設計的譯碼器電路如下:

2、保存原理圖,本實驗中命名為test1.gdf。

3、點擊File\Project\set project to current file 設置此項目為當前文件,如下圖所示。

注意,此操作在你打開幾個原有項目文件時尤為重要,否則容易出錯。

2、項目的編譯與適配

1.選擇芯片型號

選擇當前項目文件欲設計實現的實際芯片進行編譯適配,點擊Assign\Device

菜單選擇芯片,如下圖對話框所示。如果此時不選擇適配芯片的話,該軟件將自

動把所有適合本電路的芯片一一進行編譯適配,這將耗費你許多時間。該例程中

我們選用CPLD 芯片來實現,如用7000S 系列的EPM7128SLC84-6 芯片;同樣

也可以用FPGA 芯片來實現,你只需在下面的對話窗口中指出具體的芯片型號即

可。

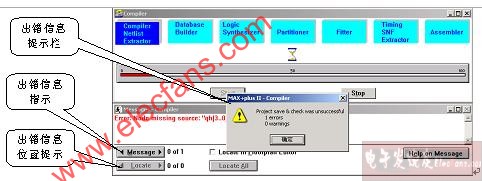

2、編譯適配

啟動MAX+plus II \ Compiler 編譯器菜單,按Start 開始編譯,并顯示編譯結

果,生成下載文件。如果編譯時選擇的芯片是CPLD,則生成 .pof 文件;如果

是FPGA 芯片的話,則生成 .sof 文件,以備硬件下載編程時調用。同時生成 .rpt

報告文件、.sym 符號文件等,可詳細查看編譯結果。如有錯誤待修改后再進行

編譯適配,如下圖所示。注意,此時在主菜單欄里的 Processing 菜單下有許多編

譯時的設置選項,視實際情況選擇設置。

如果說你設計的電路順利地通過了編譯,在電路不復雜的情況下,就可以對

芯片進行編程下載和使用,直到設計的硬件實現,如果你的電路有足夠的復雜,

那么其仿真就顯得非常必要。

3、項目的功能仿真與時序分析

MAX+plus II 教學版軟件支持電路的功能仿真(或稱前仿真)和時序分析

(或稱后仿真)。眾所周知,開發人員在進行電路設計時,非常希望有比較先進

的高效的仿真工具出現,這將為你的設計過程節約很多時間和成本。由于EDA

工具的出現,和它所提供的強大的(在線)仿真功能迅速地得到了電子工程設計

人員的青睞,這也是當今EDA(CPLD/FPGA)技術非常火爆的原因之一。下面

就MAX+plusII 軟件的仿真功能的基本應用在本實驗中作一初步介紹,在以后的

實驗例程中將不在一一介紹。

一)添加仿真激勵信號波形

1.啟動MAX+plusII\Wavefrom editor 菜單,進入波形編輯窗口,如下圖所示。

2、將鼠標移至空白處并單擊鼠標右鍵,出現如下圖所示對話窗口。

3、選擇Enter nodes from snf 選項并按左鍵確認,出現下圖所示對話筐,單

擊和按鈕,選擇欲仿真的所有I/O管腳。

電子發燒友App

電子發燒友App

評論