1、高壓?SiC MOSFET?發(fā)展歷程與研究現(xiàn)狀

1.1 SiC?材料的優(yōu)越性

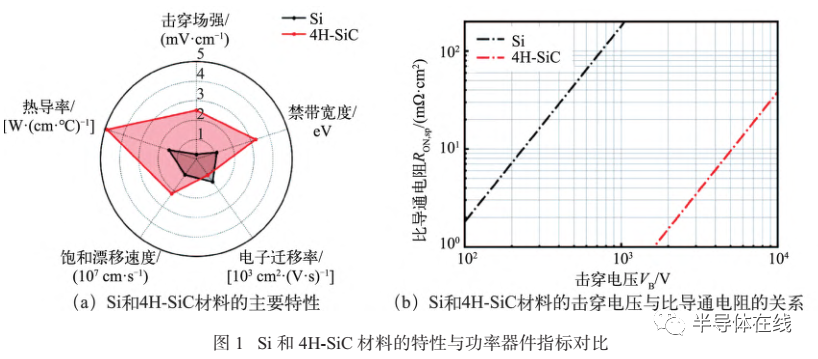

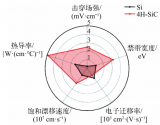

目前已知的?SiC?材料有?250?多種晶體結構,其中4H-SiC?晶型具有更高的遷移率,因此?SiC?功率器件主要基于?4H-SiC?材料。Si、4H-SiC 2?種半導體材料的主要特性如圖?1?所示,其中?Si?的帶隙寬度為?1.12 eV、熱導率為?1.5 W/ (cm·℃)、擊穿場強?Ec?為?2.5×105?V/cm,而?4H-SiC?的帶隙寬度為?3.26 eV、熱導率為4.9 W/(cm·℃)、Ec?可達?2.5×106?V/cm。4H-SiC?功率器件有著?10?倍于?Si?功率器件的擊穿場強,這意味著在同等電壓等級下?4H-SiC?功率器件的尺寸遠小于?Si?功率器件,這將進一步提升器件的功率密度,改善器件的散熱等特性,使其可以在更大電流和更高頻率下工作。從比導通電阻?RON,sp?和擊穿電壓?VB?的關系可以進一步說明?4H-SiC?材料的先進性,二者都是衡量單極型高壓功率器件的核心參數(shù),在穿通結構下存在理論極限關系:RON,sp=(3/2)3?VB2?/εs?μnEc3?,其中?εs?和?μn?分別為半導體材料的介電常數(shù)和電子遷移率,從圖?1(b)可以進一步看出,4H-SiC?功率器件與?Si?相比具有耐壓更高、損耗更低的優(yōu)良特點。

1.2 SiC MOSFET?器件的發(fā)展歷程

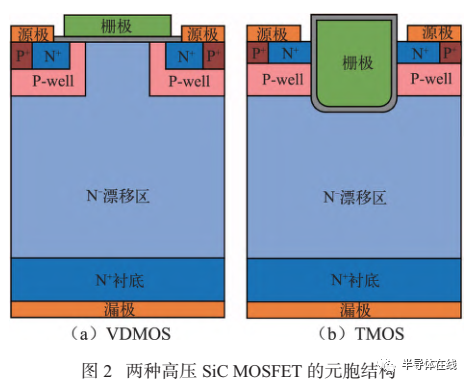

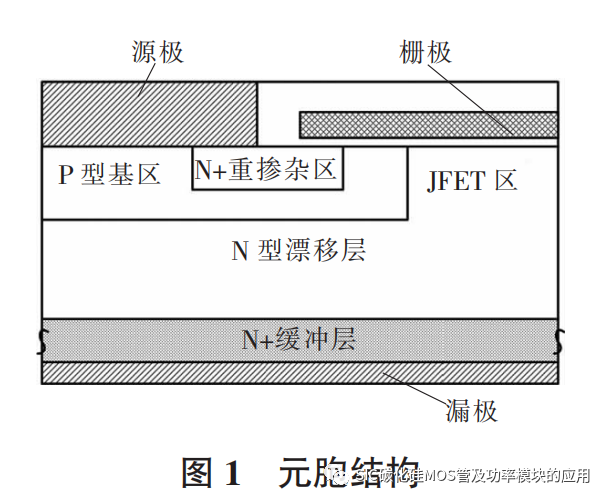

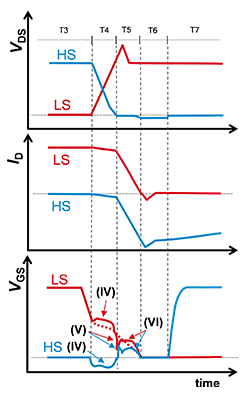

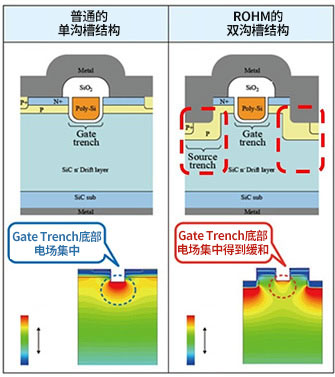

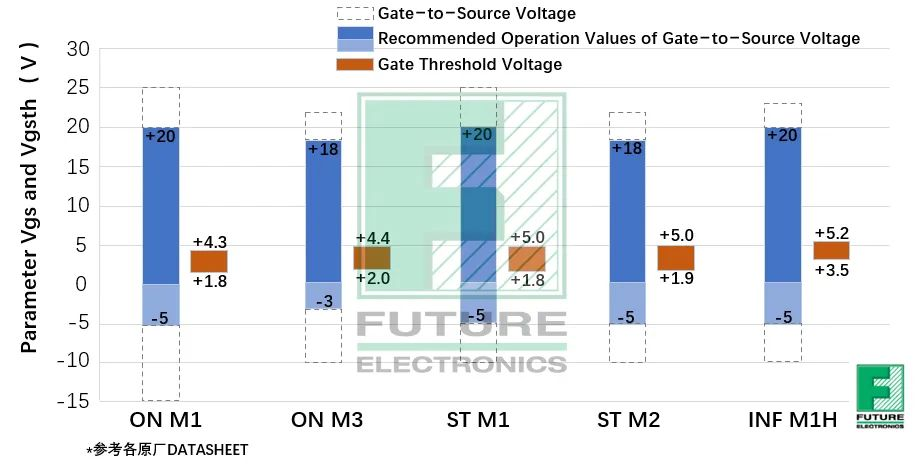

? 功率?SiC MOSFET?主要有?2?種技術路線,根據(jù)柵極工藝分為平面型?MOSFET?(VDMOS) 和溝槽型MOSFET(TMOS),兩種器件的元胞結構如圖?2?所示。多數(shù)產(chǎn)品均采用?SiC VDMOS?結構,其工藝簡單、阻斷能力強,然而導通電阻較大;SiC TMOS?是目前的研究熱點,其溝道遷移率高,但工藝較為復雜,受柵氧可靠性影響導致阻斷能力較差。

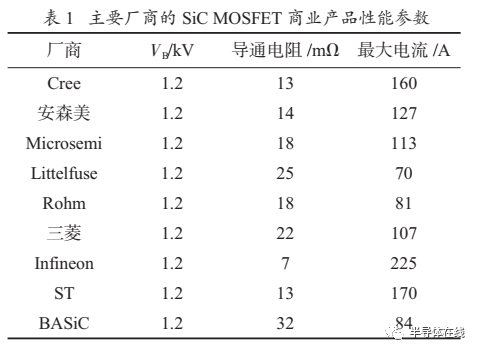

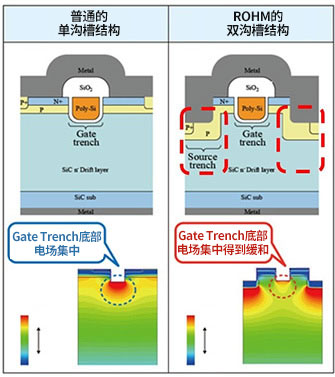

自20?世紀?80?年代第一款?3C-SiC?襯底上的橫向MOSFET?和?1994?年首個功率?SiC MOSFET?研制成功以來,各大公司和研究機構都如火如荼地進行著?SiC功率器件的開發(fā)。2001?年,Infineon?公司推出了首款商用?SiC?二極管器件。2010?年,Cree?公司和?Rohm?公司相繼推出了?SiC VDMOS?產(chǎn)品。2011?年起,各公司開始逐步推出商用?SiC?功率器件。Rohm?公司于?2012?年提出并使用雙溝槽結構?SiC TMOS;Infineon?公司于2017?年推出了?CoolSiCTM?產(chǎn)品;Cree?公司專注于平面型并已推出第三代?1.2 kV/160 A?的?SiC VDMOS。主要廠商的?SiC MOSFET?商業(yè)產(chǎn)品性能參數(shù)如表?1?所示。3.3 kV?及以下等級的功率?SiC MOSFET?已經(jīng)邁入產(chǎn)業(yè)化階段,越來越多的研究也偏向溝槽、雙溝槽(DT)結構;然而對于?3.3 kV?以上、特別是?10 kV?及以上的超高壓等級?SiC MOSFET,只能使用平面型結構以避免溝槽底部的柵氧可靠性問題。

國際上對高壓?SiC MOSFET?的研究起步較早,多家公司及科研機構均同步跟進該領域前沿方向。第一款性能較為完善的?10 kV?等級超高壓?SiC VDMOS?是由美國?Cree?公司?RYU?等人于?2006?提出和研制的,其擊穿電壓為?10 kV,電流等級為?5 A,室溫下測得比導通電阻為?111 mΩ·cm2?,使用了由?65?個浮空場限環(huán)(FLR)組成、總長度為?550?μm?的終端結構。2012?年,日本?AIST?研究所在?DT?結構的基礎上進行溝槽底部P+?區(qū)注入并實現(xiàn)了?3.3 kV/7.0 mΩ·cm2?等級的高壓SiC TMOS。2014?年,Cree?公司的?ALLEN?等人提出了?SiC VDMOS?電壓等級從?900 V?到?15 kV?的提升流程,并進一步縮減裸片尺寸、增強器件性能。2015?年,日本住友電工分別通過靠近溝槽底部深?P+?注入和終端結構注入劑量優(yōu)化,研制了?1.7 kV/3.5 mΩ·cm2?等級的高壓?SiC TMOS?和?3.3 kV/14.2 mΩ·cm2?等級的高壓SiC VDMOS。2015?年,Cree?公司首次展示了全新一代?10 kV?等級的超高壓?SiC VDMOS?器件的全部特性,其導通電阻從以往的?160 mΩ·cm2?改進到?100 mΩ·cm2?。

? 2017?年,Cree?旗下的?Wolfspeed?部門提出了新一代6.5 kV/30 A、 導 通 電 阻 小 于?90 mΩ?的 高 壓?SiC?VDMOS;同年,三菱電機公司研制出?6.5 kV/50 A?等級的高壓?SiC VDMOS,并將肖特基勢壘二極管(SBD)嵌入元胞結構中,還于次年進一步研究了不同終端結構對阻斷特性保護的穩(wěn)健性。2020?年,ABB?公司同樣提出了具有寬反向偏壓安全工作區(qū)域和大浪涌電流能力的?6.5 kV/8 A?的高壓?SiC VDMOS。同年,Rohm?公司發(fā)布了第四代雙溝槽?SiC TMOS,在不犧牲短路耐受時間的條件下降低了比導通電阻和寄生電容。

? 與國際相比,我國高壓?SiC MOSFET?領域雖然起步較晚、目前大多停留在科研階段,但研究已經(jīng)逐漸成熟,與國外的差距正在逐步減小。中國電科集團第五十五所建立了高壓?SiC MOSFET?研發(fā)部門并成功研發(fā)了?1.2 kV/50 A、3.3 kV/30 A、6.5 kV/25 A?和10 kV/15 A?等級的高壓?SiC VDMOS;株洲中車時代電氣股份有限公司、深圳基本半導體有限公司、華潤微電子有限公司等也相繼推出了?1.2 kV?等級系列高壓?SiC VDMOS;電子科技大學的鄧小川等人設計了一種多區(qū)步進間距?FLR?新結構,并據(jù)此生產(chǎn)了?13.6 kV等級超高壓?SiC VDMOS,電流等級為?10 A;浙江大學也研制出?1.2 kV?等級的高壓?SiC VDMOS。

1.3?靜態(tài)特性優(yōu)化現(xiàn)狀

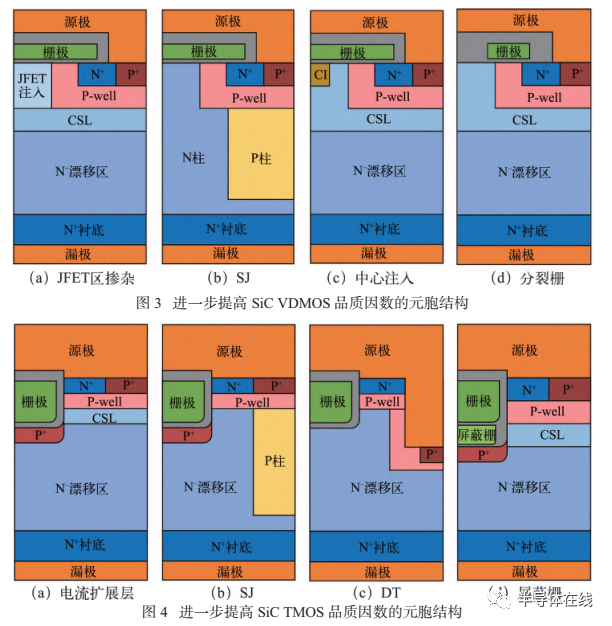

Baliga?品 質 因 數(shù) (BFOM)FB?是 描 述 高 壓?SiC?MOSFET?靜態(tài)特性的核心指標,關系式為?FB=VB 2?/RON,sp,它反映了擊穿電壓與比導通電阻之間的矛盾關系和導通特性的優(yōu)劣程度。對器件元胞結構的主要參數(shù)進行優(yōu)化,可以在維持電壓等級不變的條件下降低比導通電阻,從而提升?BFOM,然而由于溝道擊穿、柵氧可靠性等問題和襯底、電極金屬的存在,比導通電阻無法達到理論值。要想進一步提高?BFOM,需要對器件的元胞結構進行改進,通過引入外加電荷等手段進一步降低導通電阻。目前主要有?2?種改進結構,分別是JFET?區(qū)摻雜結構和超結(SJ)結構,進一步提高?SiCVDMOS?和?SiC TMOS?品質因數(shù)的元胞結構分別如圖3、4?所示。

?

?

1.3.1 JFET?區(qū)摻雜結構

? 從導通電阻的角度考慮,以?VDMOS?結構為例,當器件正向導通時,電流先從溝道水平通過,隨后從狹窄的?JFET?區(qū)以梯形的形狀流入漂移區(qū),降低器件的正向導通能力。TMOS?雖然沒有?JFET?區(qū),但也存在電流流向漂移區(qū)時路徑較窄的問題。如何降低?JFET區(qū)及其周圍電子流通路徑的電阻率,并拓寬電子在JFET?區(qū)的流動范圍以降低導通電阻,是?JFET?區(qū)摻雜結構設計的核心目標。JFET?區(qū)摻雜主要存在?2?種實現(xiàn)方式:1)JFET?區(qū)注入,即在?P-well?區(qū)頸部進行大于外延層濃度的?N?型摻雜以降低電阻率,該方式只適用于平面型;2)電流擴展層(CSL),即在?P-well?注入之前進行一定深度的大于外延層濃度的?N?型摻雜,實現(xiàn)增大電流路徑、減小導通電阻的效果,但是柵氧可靠性會受到一定程度的影響,該方式在高壓?SiC VDMOS?和?SiC TMOS?中都已經(jīng)得到了廣泛的使用,特別是在?SiC TMOS?中可以與溝槽底部?P+?屏蔽層(PS)配合使用以同時實現(xiàn)降低導通電阻和保護柵氧的作用。

? 1.3.2?超結結構

? SJ?結構的出現(xiàn)打破了傳統(tǒng)?Si?基器件比導通電阻與擊穿電壓之間的?RON,sp∝VB 2.5?極限關系,使得相同電壓等級下?RON,sp?大幅降低,是功率?MOSFET?器件自發(fā)明以來的一個重要里程碑。SJ-MOSFET?通過在漂移區(qū)引入異型摻雜,將以往的電阻性耐壓層轉變?yōu)?N/P柱交替排列形成的結型耐壓層,使得?N?柱和?P?柱之間形成橫向耗盡,提高擊穿電壓。在正向導通時,電子從N?型摻雜區(qū)通過,因此可以提高?N?型摻雜濃度,使之在維持擊穿電壓的情況下進一步降低比導通電阻。陳星弼院士于?1991?年首次提出縱向功率器件的?SJ?結構并申請專利,該結構在當時被稱為復合緩沖層。1998年開始,Infineon?公司推出了?CoolMOSTM?產(chǎn)品,其他公司也相繼研制并生產(chǎn)了?Si基?SJ?器件,SJ?技術開始廣泛運用于?Si?基功率器件中。Si?基?SJ?器件的成功讓研究人員轉向?SiC SJ?器件的研發(fā)當中。

? 目前?SiC SJ?器件主要有?2?種技術路線:1) 多次外延加離子注入(ME),即在多次外延形成?N?柱的同時多次離子注入形成?P?柱,此路線工藝方式復雜,但可以形成質量較高的結構,界面態(tài)密度和晶格缺陷較少,不過外延厚度的增加將導致成本無法控制;2) 深槽刻蝕加外延回填(TFE),該路線由日本?AIST?研究所提出,成本較低,然而深槽角度和?P?柱深度需要進行優(yōu)化設計。

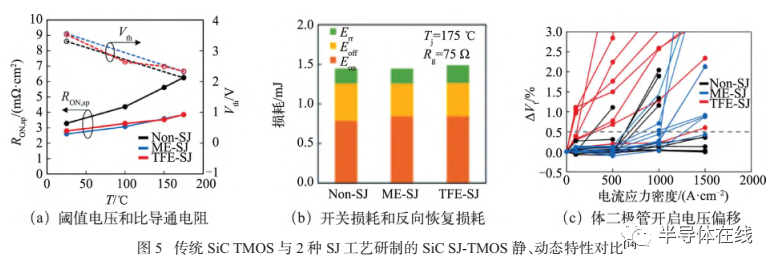

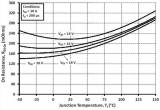

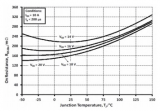

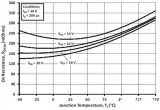

? 日本?AIST?研究所專注于?SiC SJ?器件的研究和制備。該研究所于?2013?和?2014?年分別通過?ME?和?TFE的技術路線研制出?SiC SJ?器件,并借助?TCAD?仿真研究了?ME?工藝下不同擊穿電壓器件的特性預測和?TFE工藝下回填外延區(qū)摻雜濃度對擊穿電壓的敏感性。結果表明,ME?工藝下?3.3 kV?等級器件的漂移區(qū)電阻為1.51 mΩ·cm2?,是?4H-SiC?理論極限的五分之一;兩次TFE?與單次?TFE?相比,回填外延區(qū)摻雜濃度的設計窗口更寬。2022?年,該研究所對?3?種工藝下?1.2 kV?等級SiC SJ-TMOS?器件的靜、動態(tài)特性進行了對比和分析。從圖?5(a)所示的比導通電阻隨溫度的變化趨勢可以看到,2?種?SJ?工藝都可以降低器件溫度系數(shù)并且?TFE工藝的器件溫度系數(shù)更小;在結溫?Tj?為?175?℃、柵極驅動電阻?Rg?為?75?Ω?的條件下,從圖?5(b)所示的開通損耗?Eon、關斷損耗?Eoff?和體二極管反向恢復損耗?Err?的情況可以看到,3?種工藝下器件的動態(tài)特性基本一致,因此在相同特性下成本更低的?TFE?技術更具優(yōu)勢;圖5(c)顯示了?TFE?工藝下器件的體二極管開啟電壓偏移?ΔVf?更大,雙極退化更為嚴重,這是載流子壽命在制造過程中沒有減少和外延?/?襯底界面空穴濃度高導致的,因此如何在控制成本的基礎上提高器件特性還有待進一步研究。

?

? 除了上述兩種工藝之外,浙江大學于?2018?年首次使用溝槽側壁傾斜離子注入技術研制了?1.35 kV/0.92 mΩ·cm2?等級的?SiC SBD,為?SiC SJ-TMOS?的研究提供了新的發(fā)展方向。

? SJ?技術在高壓?SiC MOSFET?器件整體應用中較少,還有著極大的發(fā)展空間。該結構可以提高?SiCTMOS?的電壓等級。TMOS?電壓等級受限于柵氧角落處的尖峰電場問題,而如果采用?SJ?結構,漂移區(qū)?N?型摻雜濃度的提高可以有效降低?RON,sp,同時?P?柱可以有效保護柵氧底部,如張躍等人設計了一種由上下?lián)诫s濃度不同的?P?柱形成的?SiC SJ-TMOS?功率器件,仿真結果表明在擊穿電壓?1 kV?下可得到?0.88 mΩ·cm2?的比導通電阻。SJ?結構也可以與?SBD?同時嵌入MOSFET?元胞中,以同時改善器件比導通電阻和反向恢復特性。日本?AIST?研究院已研制出目前電壓等級最高的?SiC SJ-VDMOS?器件,擊穿電壓達到?7.8 kV,離?15 kV?的超高壓等級還有一段距離,值得進一步設計和研發(fā)。

? SiC SJ?器件的終端結構較傳統(tǒng)?SiC MOSFET?器件來說設計復雜度更高:一方面,終端結構同樣需要考慮電荷平衡問題,以保證效率;另一方面,由于工藝的繁瑣,終端結構的工藝技術應該盡量與元胞保持一致,以降低工藝復雜度,即如果元胞使用的是?ME?工藝,則終端也需使用同樣的工藝形成?N/P?柱的交替結構。該領域目前國際上已有相關研究,如?MASUDA?等人將?ME?工藝和結終端擴展(JTE)技術結合起來,設計和研制了針對?1.2 kV?等級?SiC SJ-TMOS?的一種新型終端結構,然而研究成果總體較少,有待進一步深入研究。

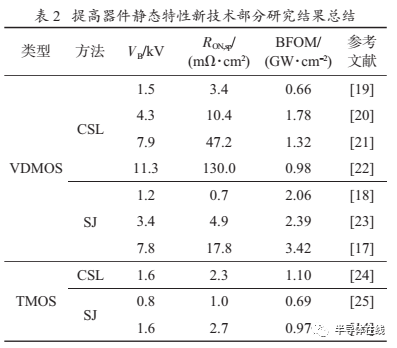

? 國內外針對?2?種結構器件?BFOM?優(yōu)化的研究成果如表?2?所示,其中?JFET?區(qū)注入技術常常與?CSL?技術合并,因此不在表中列出。

?

?

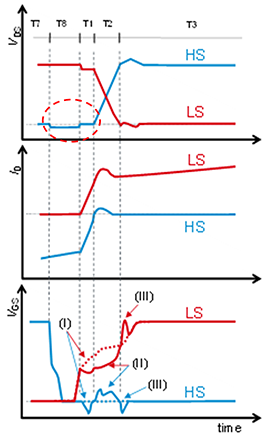

1.4?動態(tài)特性優(yōu)化現(xiàn)狀

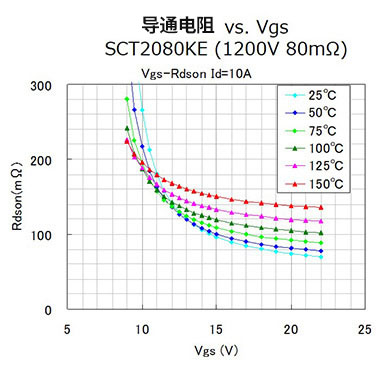

? 高頻品質因數(shù)(HF-FOM)是高壓?SiC MOSFET?另一個主要性能指標,它一般是?RON,sp?和比柵漏電荷?QGD,sp的乘積,反映了器件動態(tài)特性的優(yōu)劣程度,其中影響柵漏電荷的主要因素是轉移電容的大小。

? 對于高壓?SiC VDMOS?來說,目前有幾種技術和結構可以改善器件的?HF-FOM:1)中心注入技術(CI),如圖?3(c)所示,即在柵氧下方注入一個?P?型摻雜區(qū),該技術可以同時實現(xiàn)增強動態(tài)特性和減小柵氧電場的效果,只適用于平面型結構,以?Cree?公司的CIMOSFET?產(chǎn)品為代表[26],該技術與?CSL?技術同時使用可以在兼顧動態(tài)性能的基礎上進一步降低?JFET?區(qū)導通電阻;

? 2)分裂柵(SP)結構,如圖?3(d)所示,即只保留溝道上方的柵極多晶硅而去掉?JFET?區(qū)上方的部分,如?YOON?等人將?SP?應用于?3.3 kV?等級器件并進行了仿真驗證;YU?等人在?SP?的基礎上給源極加上場板結構,在降低柵極邊緣電場強度的同時將HF-FOM?減小了?40%;LYNCH?等人研制了?15 kV?等級?SP?結構器件,柵漏電荷較傳統(tǒng)平面型降低了70%。除此之外,AGARWAL?等人通過理論驗證了將柵氧厚度從?55 nm?降低到?27 nm?后器件靜、動態(tài)特性的提升。

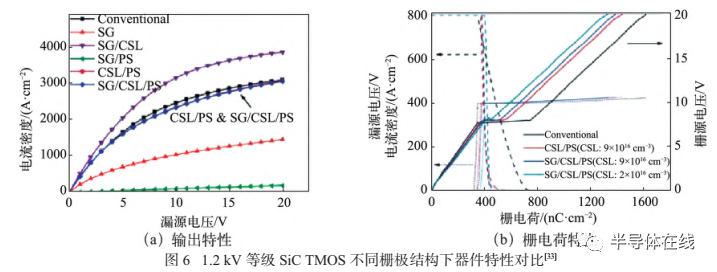

? 對于?SiC TMOS?來說,DT?結構和屏蔽柵(SG)結構可以有效改善動態(tài)特性。1)DT?結構以?Rohm?公司的雙溝槽?SiC TMOS?產(chǎn)品為代表,如圖?4(c)所示,它通過源極溝槽保護柵氧,實現(xiàn)了?1.26 kV/1.41 mΩ·cm2的優(yōu)越特性。YANG?等人在?DT?的基礎上引入了深?PS結構,較改進前柵漏電荷降低了?89%;YANG?等人提出了一種深氧化物溝槽代替源極溝槽的結構,在改善靜態(tài)特性的情況下降低了開關損耗。2)SG?結構首先在?Si?基器件中提出,隨后在?SiC TMOS?中得到了改進,如圖?4(d)所示,它通過橫向耗盡漂移區(qū)和減少柵漏之間有效重疊面積同時降低導通電阻和轉移電容,大幅提升動態(tài)特性。JIANG?等人按是否有?SG、PS?和CSL?將?SiC TMOS?分為?6?種結構,并進行了靜、動態(tài)特性仿真對比,如圖?6?所示。結果顯示,SG?結構可以降低柵電荷,但是?SG?與?PS?結構對導通特性影響嚴重,而通過?CSL?的引入,可以在降低?RON,sp?的基礎上進一步降低?QGD,sp,顯著提高器件的?HF-FOM。

?

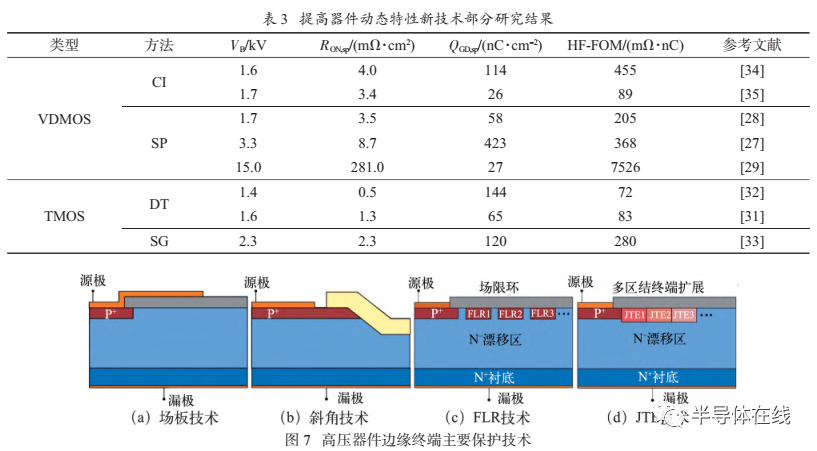

表?3?展示了?2?種元胞結構?HF-FOM?優(yōu)化的部分研究結果。表?3?中只有文獻[29]和[34]為實際流片測試結果,可以看出仿真結果較實際器件特性還有一定距離,因此如何更準確地預測和描述實際器件的動、靜態(tài)特性并在此基礎上進一步改進器件的高頻工作性能,還需進一步研究和實踐。

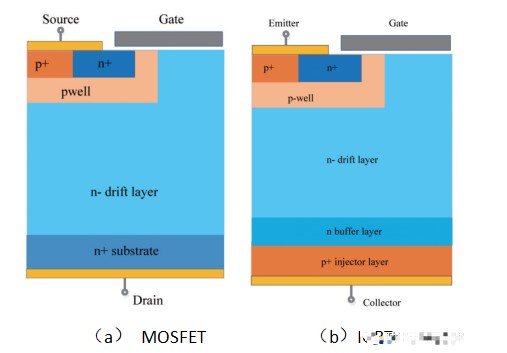

? 1.5?終端研究現(xiàn)狀

? 器件在阻斷狀態(tài)下,主結的邊緣處曲率較小,容易產(chǎn)生電場集中的現(xiàn)象,導致器件的阻斷性能嚴重退化,擊穿電壓大大降低。特別是?4H-SiC?材料,其擴散系數(shù)較?Si?來說更小,對于?MOSFET?和?IGBT?等淺結器件來說,曲率效應更為嚴重。因此高壓?SiC MOSFET的邊緣終端需要進行保護。目前存在的幾種高壓器件邊緣終端主要保護技術如圖?7?所示。

?

場板技術和斜角技術在?Si?基器件中較為成熟,然而其耐壓等級較低,不適用于高壓?SiC?器件。FLR?技術和?JTE?技術被認為更加適用于高壓?SiC MOSFET器件。

? 1.5.1 FLR?技術

? FLR?技術也被稱作浮空場環(huán)技術,即注入多個?P型場環(huán),緩解主結邊緣的電場集中問題,以改善器件的阻斷特性。在實際制造過程中,F(xiàn)LR?往往和主結同時注入,不需要額外的工藝步驟,技術簡單且成本較低,在?SiC?功率器件中已經(jīng)得到了廣泛的使用。已有相關研究推導了?FLR?結構的理論公式,然而對于高電壓等級特別是?10 kV?及以上等級的?SiC MOSFET?來說,往往需要上百個場環(huán),理論分析基本無法指導結構設計,而且受限于工藝條件,環(huán)間距無法做到與計算值一樣精確。這就需要根據(jù)相關參數(shù)進行?FLR?結構設計和實驗驗證。

? FLR?結構主要由環(huán)寬和環(huán)間距決定,根據(jù)二者的設計產(chǎn)生了多種結構,其中最經(jīng)典的便是等環(huán)寬、等間距結構(Con-FLR),除此之外還有固定環(huán)寬、改變間距的結構,如路曉飛等人提出的間距呈指數(shù)變化的FLR?結構、間距呈線形變化的?FLR?結構,鄧小川等人提出的多區(qū)步進間距?FLR?結構,以及環(huán)寬與間距協(xié)調配合的結構等。

? FLR?技術的問題在于終端面積較大,這可以通過與其他技術相結合的方法進行優(yōu)化,例如?WEN?等人針對?10 kV?等級器件,提出了一種刻蝕和?FLR?相結合的刻蝕均勻?FLR?(EU-FLR) 結構,阻斷能力達到14.2 kV?并且終端長度大幅降低。

? 1.5.2 JTE?技術

? 簡單來說,JTE?技術就是在主結旁邊額外注入一段長度的?P?型摻雜,為主結分壓以減小曲率效應。該技術由?KALER?在?1977?年首次提出,其在高壓?Si?基器件上的有效性得到驗證后,JTE?技術便被業(yè)界廣泛關注,多種改良型?JTE?結構也相繼提出。隨著?SiC?材料的研究和應用,功率器件的耐壓等級已經(jīng)超過10 kV,特別是超高壓?SiC PiN?器件,目前國際上已經(jīng)達到將近?30 kV?的水平,針對高壓?SiC?器件的?JTE?技術被相繼提出,從臺面單區(qū)?JTE?到多區(qū)?JTE,再到空間調制?JTE,在?JTE?技術的保護下功率器件越來越逼近雪崩擊穿的理論擊穿電壓,并且其終端區(qū)域的利用效率也不斷提高,如?2018?年?NAKAYAMA?等人利用空間調制?JTE?技術研發(fā)出?27.5 kV?等級?4H-SiC PiN?功率二極管。

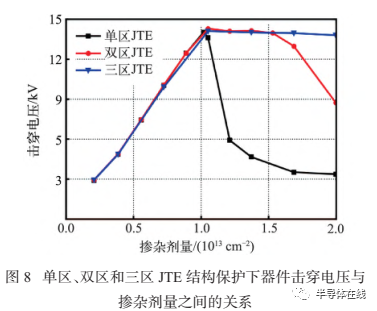

? JTE?技術的核心問題在于終端保護效率對于摻雜劑量的敏感度較高,加上?4H-SiC?中雜質存在不完全電離的情況,即使精準控制注入劑量也會導致實際激活的劑量不受控制,因此大部分?JTE?改進結構都在朝著擴大摻雜劑量窗口的方向進行探索。對?10 kV?等級器件進行終端保護仿真,分別設計單區(qū)、雙區(qū)和三區(qū)JTE?結構,得到的擊穿電壓與摻雜劑量之間的關系如圖?8?所示。仿真中元胞擊穿電壓值為?14.4 kV,可以看到單區(qū)?JTE?的劑量窗口不足?0.3×1013?cm-2?,雙區(qū)結構下敏感性得到了明顯改善,劑量窗口達到?0.8×1013?cm-2?,到三區(qū)結構下劑量窗口超過?1.5×1013?cm-2?,證明了多區(qū)JTE?結構可以有效改善劑量窗口問題。

?

單純地增加區(qū)域數(shù)將增加工藝流程中的離子注入步驟,大大提高成本。目前?JTE?技術趨向于使用固定的?2?種或多種摻雜劑量,通過調制摻雜區(qū)域的形狀和寬度來形成多個不同等效電離電荷濃度的區(qū)域。KAJI?等人首次結合空間調制技術和雙區(qū)?JTE?技術在外延層厚度為?268?μm、摻雜濃度為?1×1015?cm-3?的條件下實現(xiàn)了?26.9 kV?的擊穿電壓[,保護效率達到?70%,劑量窗口大于?1.5×1013?cm-3?。在此基礎上,改進?JTE?結構的保護效率越來越高,終端長度也有所改善,如WEN?等人于?2020?年研制和生產(chǎn)了使用在?13.5 kV?等級?4H-SiC PiN?二極管器件中的一種被稱為電荷場調制?JTE(CFM-JTE)的結構,在?400?μm?的終端長度下實現(xiàn)了?96%的終端保護效率和大于傳統(tǒng)雙區(qū)?JTE?結構?1.8?倍的劑量窗口。

? 將?JTE?技術與其他技術進行結合,可以在相同終端面積下進一步提高保護效率,如?DAI?等人于?2021年提出的刻蝕溝輔助空間調制?JTE?(TSM-JTE)結構;ZHOU?等人提出了一種結合刻蝕與單區(qū)?JTE?的超小角度斜角刻蝕?JTE?結構(ULA-BE-JTE),實現(xiàn)了超過?90%的保護效率。另外,對?JTE?技術的仿真工作已經(jīng)使器件的擊穿電壓達到了?30 kV?以上的等級,如JOHANNESSON?等人在?TCAD?仿真上用?1800?μm?的單側?JTE?區(qū)加?27?個外側保護環(huán)實現(xiàn)了?41.4 kV?的擊穿電壓。

? 2?高壓?SiC MOSFET?的瓶頸與挑戰(zhàn)

? 當下,高壓?SiC MOSFET?還存在一些瓶頸和挑戰(zhàn),這里對?4?個主要問題進行討論。

? 2.1?雙極退化效應

? 高壓?SiC MOSFET?器件存在體二極管結構,理論上可以取代外接反并聯(lián)二極管并降低電路寄生電感與損耗。然而在雙極性運行條件下,體二極管的導通會帶來雙極退化效應,影響器件的導通電阻、漏電流和體二極管導通壓降等特性,不利于器件的長期工作。

? 從應用的角度,人們普遍使用同步整流技術以盡量避免體二極管的開通;從器件結構設計的角度,近年來針對該問題出現(xiàn)了一些致力于將?SBD?或結勢壘肖特基二極管嵌入?MOSFET?元胞結構當中的研究,如DENG?等人提出了一種低勢壘二極管集成新結構,在1.2 kV?等級器件中獲得了較體二極管低約?67%的開啟電壓;LI?等人提出了一種在雙溝槽?SiC MOSFET中加入全耗盡?P-well?區(qū)以降低勢壘并抑制雙極退化效應的新結構。然而嵌入的方式將會導致器件特性和可靠性的改變,KONO?等人研究了?1.2 kV?等級?SBD嵌入式器件的比導通電阻與短路耐受能力之間的權衡關系。如何有效解決該問題還需進一步深入研究。

? 2.2?低電流等級問題

? 高壓?SiC MOSFET?由于其單極工作模式,高擊穿電壓將嚴重限制器件的導通電流能力。例如對于10 kV?等級器件來說,室溫下其電流等級約為?20~40 A/cm2?,當溫度增加到?200?℃以上時,額定電流將下降?50%~70%。加之厚的外延層更容易引入缺陷,終端的存在導致芯片源區(qū)實際面積不大,因此?6.5 kV?及以上的單片并不能滿足相應等級應用場景的需求。針對這一問題目前有?3?種解決方案:1) 制作多芯片并聯(lián)模塊以提高電流等級,如?Wolfspeed?研制了?12?個芯片并聯(lián)的?10 kV/240 A?功率模塊;2)使用雙極型器件,如目前?15 kV?等級及?SiC?柵極可關斷晶閘管器件電流等級可以超過?100 A;3)繼續(xù)改進外延技術,找到控制外延缺陷的新技術。針對電流等級低的問題,未來需要繼續(xù)優(yōu)化器件結構以降低溫度系數(shù),不斷改進關鍵工藝技術以降低缺陷密度,從而進一步提升高壓?SiC?MOSFET?的電流等級。

? 2.3?外延缺陷問題

? 高壓器件的性能主要依賴于外延層的材料和技術。目前主流的外延生長工藝是化學氣相沉積法(CVD),一方面在工藝過程會產(chǎn)生點缺陷,另一方面襯底中的微管、堆垛層錯等擴展缺陷會進入外延中,嚴重影響外延層的質量和芯片良率。研究顯示,對襯底表面采用氫刻蝕等工藝可以有效除去表面損傷和表面缺陷,對熱壁式?CVD?的反應室進行改進也可以提高外延的質量和均勻性。國內外已有表面缺陷小于1 cm-2?、厚度為?30?μm?的成熟?6?英寸外延片,然而厚度大于?50?μm?時缺陷密度將進一步擴大,不利于高壓SiC MOSFET?的發(fā)展和應用。如何改善工藝條件以控制外延缺陷和阻擋襯底缺陷的影響,仍需進一步的實驗測試和驗證。

? 2.4?可靠性問題

? 柵氧的工藝質量和缺陷水平是制約高壓?SiC?MOSFET?長期工作的關鍵因素之一。在重復柵偏電應力和高溫工作環(huán)境的作用下,柵氧界面陷阱會不斷地捕獲或者釋放電荷,嚴重影響器件的參數(shù)穩(wěn)定性和運行可靠性。與?Si?基器件相比,高壓?SiC MOSFET?的SiC/SiO2?界面缺陷密度比?Si/SiO2?界面高出約?2?個數(shù)量級,這是?SiC?與?Si?的材料特性差異和?SiC?工藝技術不成熟導致的,使得高壓?SiC MOSFET?柵氧界面缺陷對電荷的捕獲與釋放效應更加嚴重,進而引起閾值電壓、導通電阻、漏電流等器件參數(shù)的退化和不穩(wěn)定。閾值電壓漂移是器件參數(shù)穩(wěn)定性中的一大問題,在?2006年就有研究展示了高達數(shù)百毫伏的閾值電壓漂移量,AIVARS?等人報道了一氧化氮退火工藝在柵氧界面處 產(chǎn) 生 的 空 穴 陷 阱 會 導 致 閾 值 電 壓 負 向 漂 移 。PUSCHKARSKY?等人針對閾值電壓穩(wěn)定性問題對比了?Si、SiC?功率?MOSFET?二者的區(qū)別,并討論了在動態(tài)應力下的閾值電壓測量技術。柵氧壽命也是評價器件長期可靠性的重要方面,這主要通過時變介質擊穿實驗進行表征。有研究顯示,在器件正常工作的情況下,柵氧電場強度達到?3 MV/cm,柵氧壽命可達到100?年,也有工作通過改進氧化工藝以提高柵氧質量和壽命。整體上,高壓?SiC MOSFET?的柵氧工藝還未成熟,需要進一步優(yōu)化工藝水平,提高器件的可靠性和性能。

? 器件在極端工作條件下的可靠性對于保證系統(tǒng)的穩(wěn)定運行起著至關重要的作用,主要的問題有雪崩失效、短路失效和浪涌失效等。高壓?SiC MOSFET?在非鉗位感性負載下的雪崩失效機理目前有?3?種解釋,分別是由源區(qū)寄生雙極結型晶體管(BJT)開啟導致結溫急劇上升產(chǎn)生壞點、溫度升高導致溝道自開啟和鋁電極達到熔點,這?3?者最終都導致熱失效,然而失效原因各不相同。白志強等人對?P-well?區(qū)的結構和摻雜進行調整和改進,通過降低?BJT?基區(qū)串聯(lián)電阻和?JFET區(qū)曲率效應以提高器件的雪崩耐受性;KIM?等人通過減小柵氧厚度和調窄?JFET?區(qū)寬度降低了飽和電流,以提高雪崩能量。器件的短路失效和浪涌失效除了熱失效原因外,場氧區(qū)斷裂或鋁熔化破壞柵氧導致柵源短路也是兩個原因,這對于沉積、熱氧化工藝也提出了更高的要求。除此之外,由于?SiC?高于?Si?的熱導率和楊氏模量,繼續(xù)使用傳統(tǒng)?Si?器件的封裝技術也將阻礙高壓?SiC MOSFET?器件的可靠性提升。

? 針對以上問題,如何改進現(xiàn)有工藝以提高柵氧質量,如何改進器件結構或封裝結構以緩解熱失效問題或增加散熱能力,都是未來需要進一步研究和解決的問題。

? 3?結束語

? 針對高壓?SiC MOSFET?器件,本文首先回顧和總結了器件發(fā)展歷程與該領域中的最新研究進展,其次介紹了用于優(yōu)化品質因數(shù)的器件改進結構,進而針對高電壓等級要求闡述了幾種適用于高壓器件的終端保護結構的保護機理與發(fā)展趨勢,最后對高壓器件當前存在的瓶頸和挑戰(zhàn)進行了討論。

? 高壓?SiC MOSFET?器件將在當前乃至未來的電力電子領域發(fā)揮越來越重要的作用,推動電能變換朝著更高電壓、更高頻率、更高功率密度的方向前進。近年來,高壓?SiC MOSFET?器件得到了越來越多的機構和企業(yè)中科研工作者的關注,發(fā)展勢頭越來越猛烈,這對于未來電能傳輸和變換應用方面的發(fā)展有著巨大的推動作用。雖然受到國外對我國先進半導體材料和工藝上的限制,但國內諸多高校和科研機構仍在持續(xù)進行技術研發(fā)并跟進國際最新發(fā)展方向,與國際先進水平的差距逐漸縮小,國內從業(yè)者需要堅持吸取先進技術和經(jīng)驗,早日達到國際領先水平。

編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評論