CSS-3---單節電池保護解決方案

引言:前面兩節分別介紹了PCM的幾種方案,本節聚焦于PCM的性能評估以及可能遇到的問題優化。

1. 功率MOSFET的性能要求

離子電池容量從早期的600mAh、1000mAh到現在已經達到6000mAh、10000mAh。 為了實現更快的充電速度和更短的充電時間,通常采用增加電流和大電流充電的快充技術。 大電流充電對電池組中的功率MOSFET提出了更高的技術要求。

此外在生產線和使用過程中,對大容量鋰離子電池有一些特定的技術要求。 所有這些因素都對大容量鋰離子電池PCM中功率MOSFET的充放電管理提出了嚴格的技術設計挑戰。

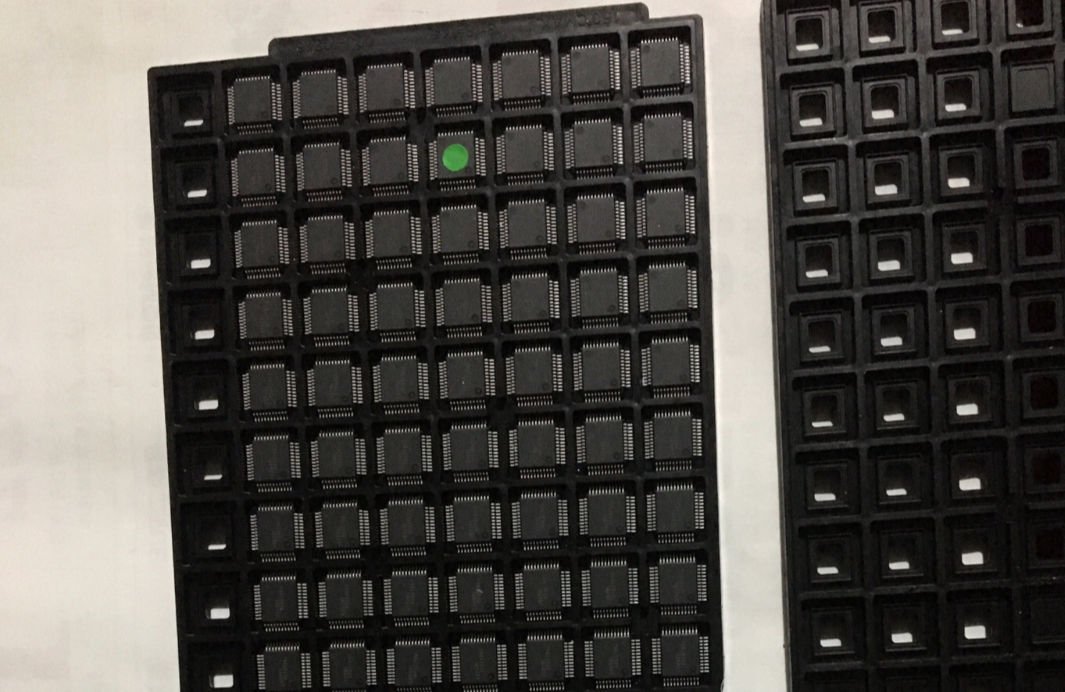

為了實現功率MOSFET的低導通電阻RDSon,有必要提高MOSFET單元密度。 其他技術也用于降低電阻,例如厚金屬鍵合線和薄晶片。 N溝道功率MOSFET可以以減小的形狀因數實現較低的導通電阻RDSon。

功率MOSFET封裝通常使用引線,為了進一步降低導通電阻,在PCM中通過使用新的芯片級CSP封裝技術完全消除了封裝線電阻。 同時芯片級CSP的封裝技術具有更好的導熱性,從而降低功率MOSFET的溫升,這有助于提高其可靠性。

使用CSP封裝技術的功率MOSFET在沒有外部塑料外殼和其他材料保護的情況下,在PCM生產過程中會受到各種熱應力和機械應力的影響,例如PCB板的焊接過程,這可能會導致模具開裂的高風險。 因此應使用各種技術,例如在功率MOSFET芯片表面涂覆新材料,以確保其抵抗機械應力和熱應力的能力,并提高可靠性。

短路能力

大容量鋰離子電池在應用中,特別是在極端條件下,如輸出負載短路,會有非常大的電流通過電池。 當IC檢測到輸出過流時,它將延遲一段時間以進行保護動作。 在延遲時間期間,MOSFET的工作電流非常大,這要求MOSFET對大電流應力具有魯棒性,因此所有鋰離子電池都需要進行短路測試。

理論上芯片尺寸越大,對短路電流的魯棒性越強。然而隨著形狀因素的減小,性能將受到限制。因此應用電路設計需要記住確保魯棒設計以抵抗大短路電流的影響所需的要求。

雪崩魯棒性

當電池組的輸出端短路且開關關閉時,MOSFET雪崩能力非常重要。功率MOSFET的選擇應包括根據應用條件確定的足夠雪崩能力。

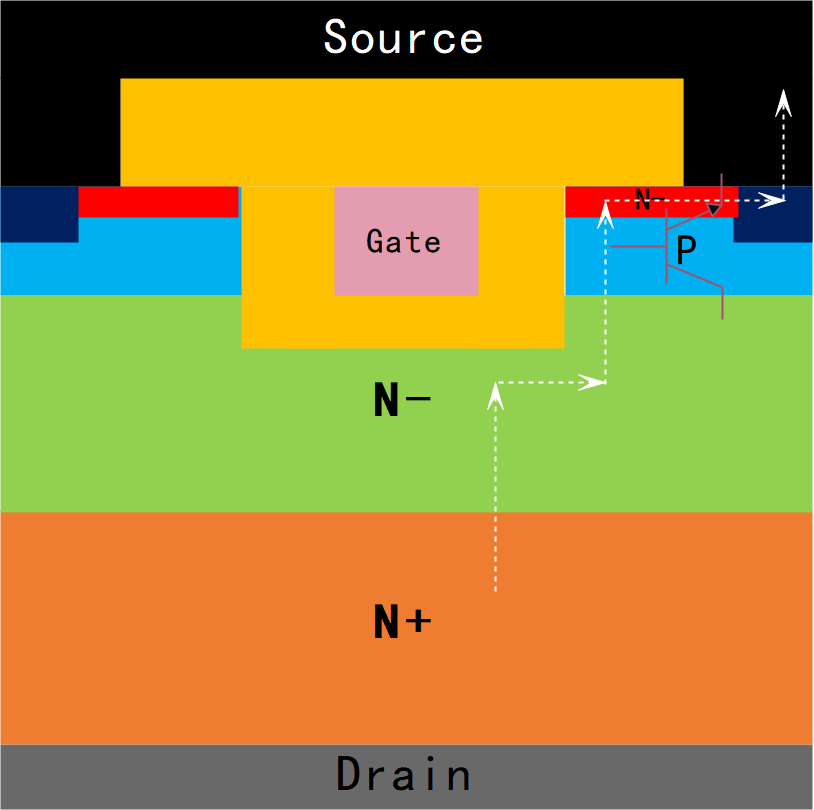

dv/dt保護

在反向連接測試期間,每個電池的最大工作電壓為4.4V,最大充電電壓也為4.4V。當充電器反向連接到電池組時,MOSFET承受8.8V的電壓應力。在大容量鋰離子電池的生產過程中,外部直流電源在測試過程中會直接接觸電池組的兩個輸出端。因此MOSFET會承受8.8V高dv/dt電壓應力。

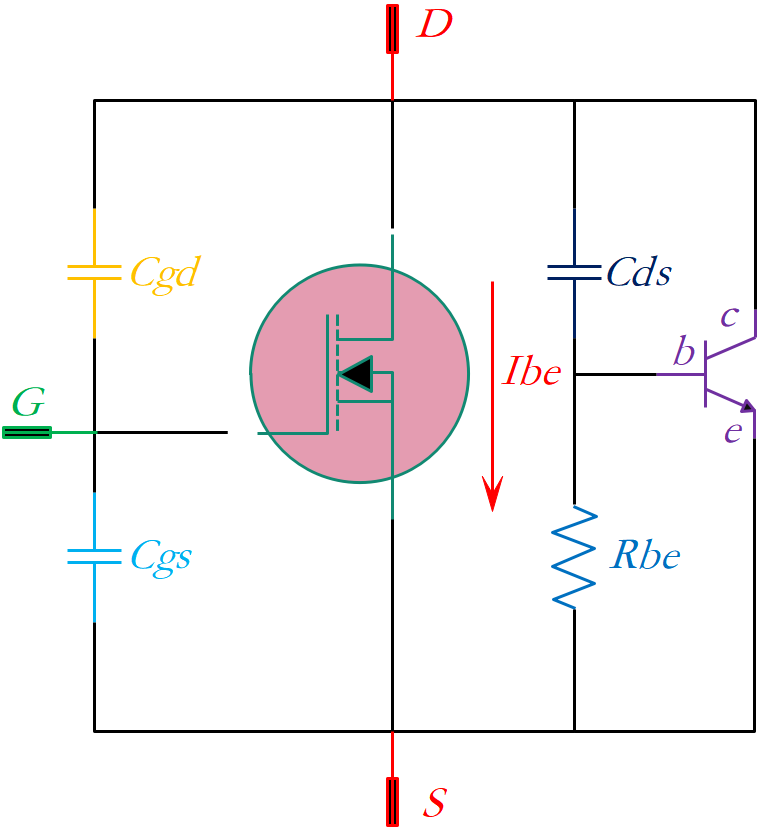

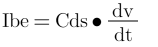

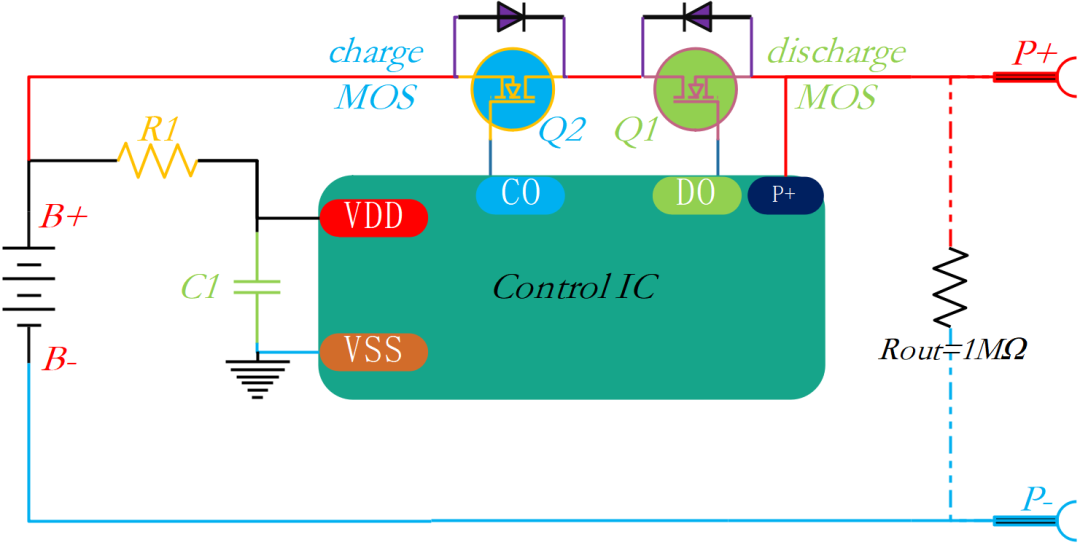

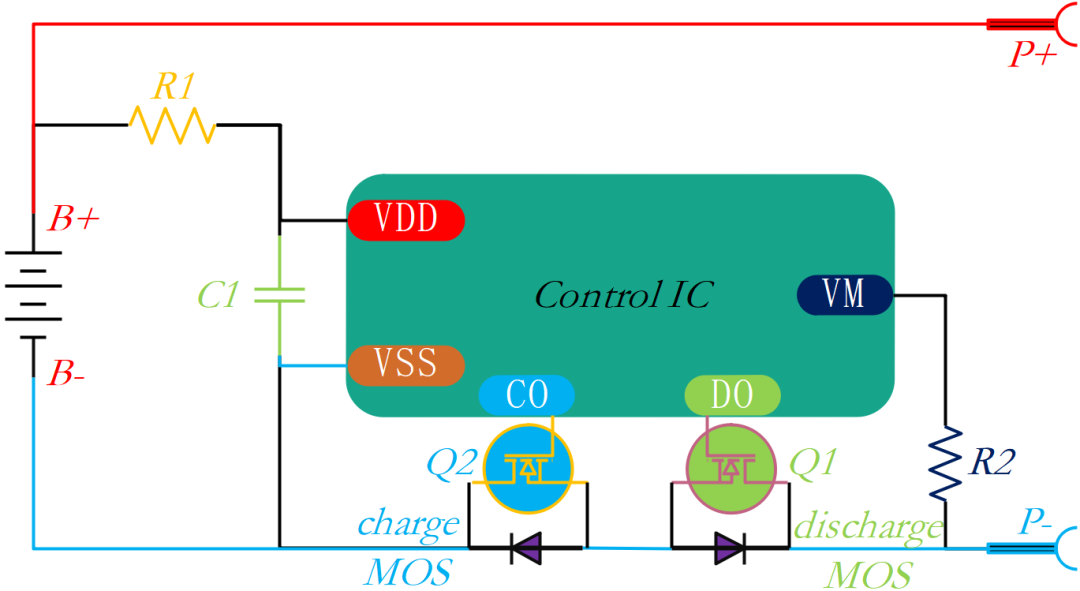

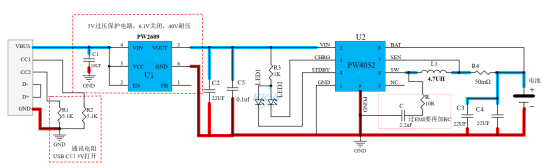

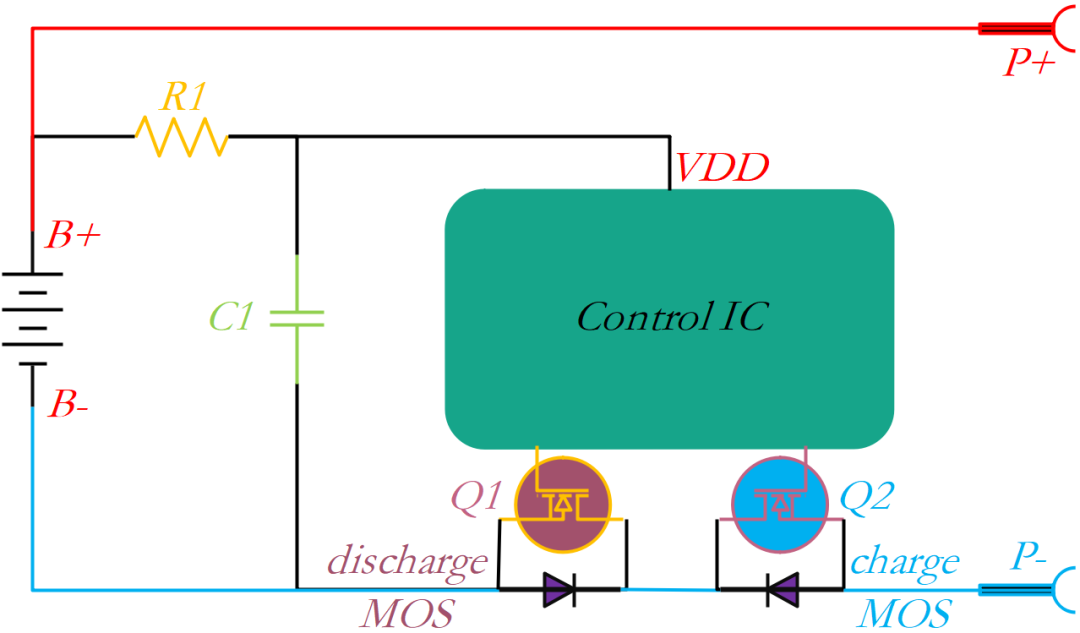

圖3-1:高電壓應力模型

如果MOSFET在漏極到源極之間經歷高dv/dt,如圖3-1模型,寄生電容CDS將具有I=CDSdv/dt的充電電流。如果電流足夠大,它將觸發寄生NPN雙極導通,MOSFET很容易損壞,如圖3-2所示。

圖3-2:高dv/dt雙極導通圖

為了避免損壞電路,直接接觸的電壓越高,電池組的魯棒性越強。該測試是MOSFET對dv/dt公差的實際測量。通常在電池組輸出短路和保護關閉的過程中也會產生較大的動態dv/dt。過高的dv/dt將對功率MOSFET造成動態雪崩損壞。因此有必要優化功率MOSFET的結構,以確保其對直接接觸高電壓和高dv/dt具有足夠的耐受力。

在正常環境溫度下,MOSFET的溫度通常不超過65°C。PCM控制板通常與電池組裝在一起,PCB尺寸是一個限制因素,通常具有較高的熱阻。因此可能需要對系統的熱設計進行特殊考慮。

例如47W的手機快速充電器的充電電壓為5V,最大充電電流為9.4A。典型RDSON約為0.8mΩ,需要并聯兩枚以進一步降低電阻。電流路徑在板的頂部和底部之間是對稱的,以保持電流平衡。建議兩個MOSFET之間的距離不小于3mm,以避免彼此發熱影響。最大化功率路徑的銅面積并在MOSFET附近的銅焊盤上添加一些用于散熱的通孔是提高散熱能力和降低MOSFET溫度升高的良好設計。

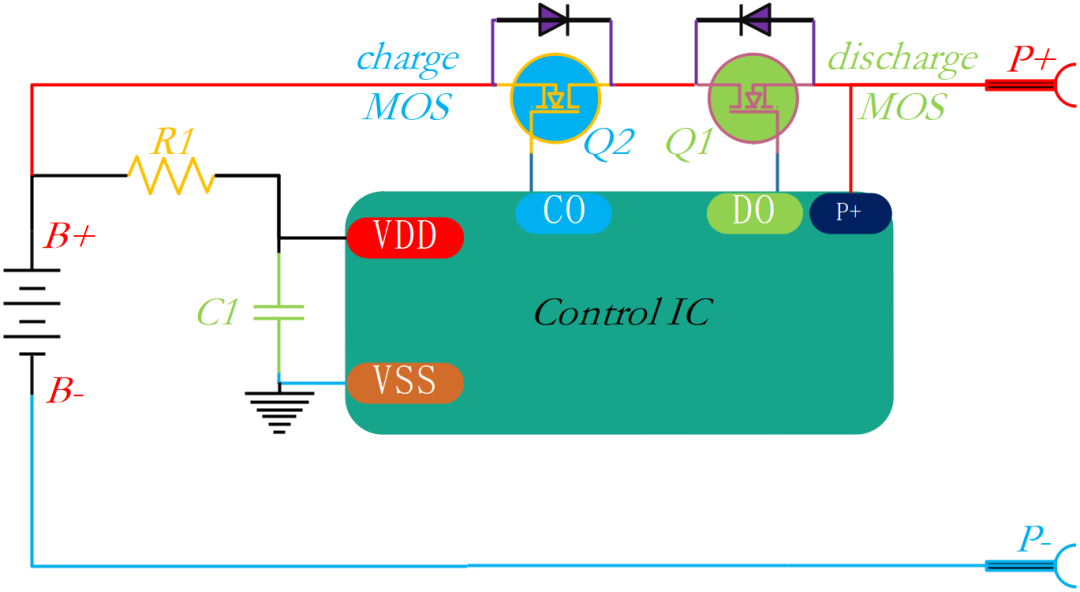

2. 輸出泄漏電流

在電池組生產過程中,即使充電MOSFET和放電MOSFET都關閉,當電池電壓施加在MOSFET上時,有時仍會通過MOSFET產生輸出泄漏電流。通常泄漏電流非常小,對系統沒有影響。如果泄漏電流更高,高達100nA,仍在數據表的限制范圍內,則該泄漏電流將在輸出阻抗上具有一定的電壓。

通常輸出阻抗約為10MΩ,電壓等于輸出阻抗和泄漏電流的乘積。在上述條件下,輸出電壓為1V,100nA*10MΩ。當輸出電壓在P+和P-之間高于0.8V時,有的保護IC將判斷有充電電壓施加在P+端,充電MOSFET將試圖打開電池充電IC的預充電功能。這就會造成IC開始工作,增加電池的靜態功率損失,在嚴重情況下,電池將耗盡電量。

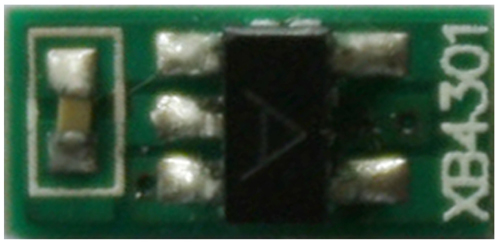

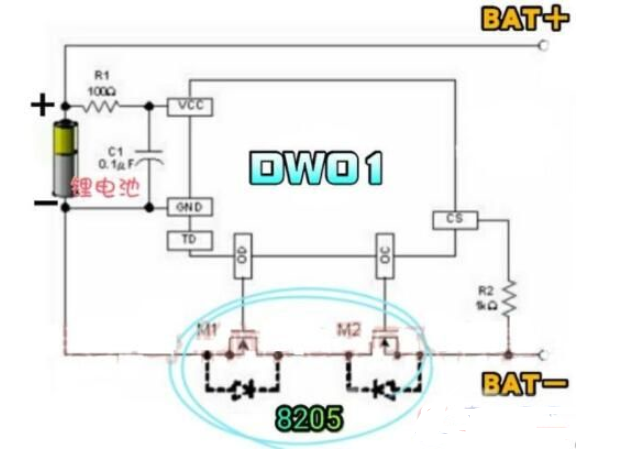

圖3-3:高側共漏連接

通常,數據表中30V MOSFET的IDSS小于1μA。在實際的筆記本電池應用中,電池電壓通常在9V到13.2V之間。在13.2V的電池電壓下,放電MOSFET的漏電流IDSS是否高于100nA是未知的。

3. 避免輸出漏電流的解決方案

在實際系統中,電池的輸出端子連接到主板,主板包括電容器、電阻器和許多其他設備,這些部件可能會產生一定的泄漏電流。主板電池接口的測量阻抗通常小于1MΩ。連接電池組后,通過1MΩ阻抗的上述泄漏電流不會導致系統出現任何問題。在制造步驟的任何階段,當電池組未連接到主板時,有兩種解決方案可以避免輸出泄漏電流的影響。

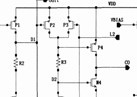

解決方案A:建議將1MΩ電阻器與電池組P+和P-的輸出端子并聯,如圖3-4所示。在測試實際使用效果后,可以有效地消除該泄露問題。

圖3-4:并聯輸出電阻器

在添加1MΩ電阻器后,泄漏電流導致的P+端子電壓將降至0.46V,并且MOSFET不再會被電池保護IC誤判導通。但是放置此電阻器的缺點是會導致電池輕微放電。例如如果通過該電阻器的漏電流為0.46μA=0.46V/1M,在電池組存儲十年期間,電阻器消耗的總能量等于0.46μA24小時365天*10年=40.3mA*小時。它僅小于筆記本電腦正常4100mA*小時電池能量的1%,這是可以接受的。輸出1MΩ放電電阻器也可以放置在電池組生產線的測試站上。

解決方案B:建議將IC內部預充電功能的P+端子電壓檢測值從單個電池的0.8V增加到2V,并將串聯的三個電池單元的檢測值增加到6V,這樣一來即使泄漏電流較大,系統也可以保持正常。

電子發燒友App

電子發燒友App

評論