2.設(shè)計(jì)的實(shí)現(xiàn)

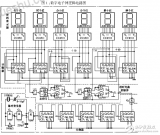

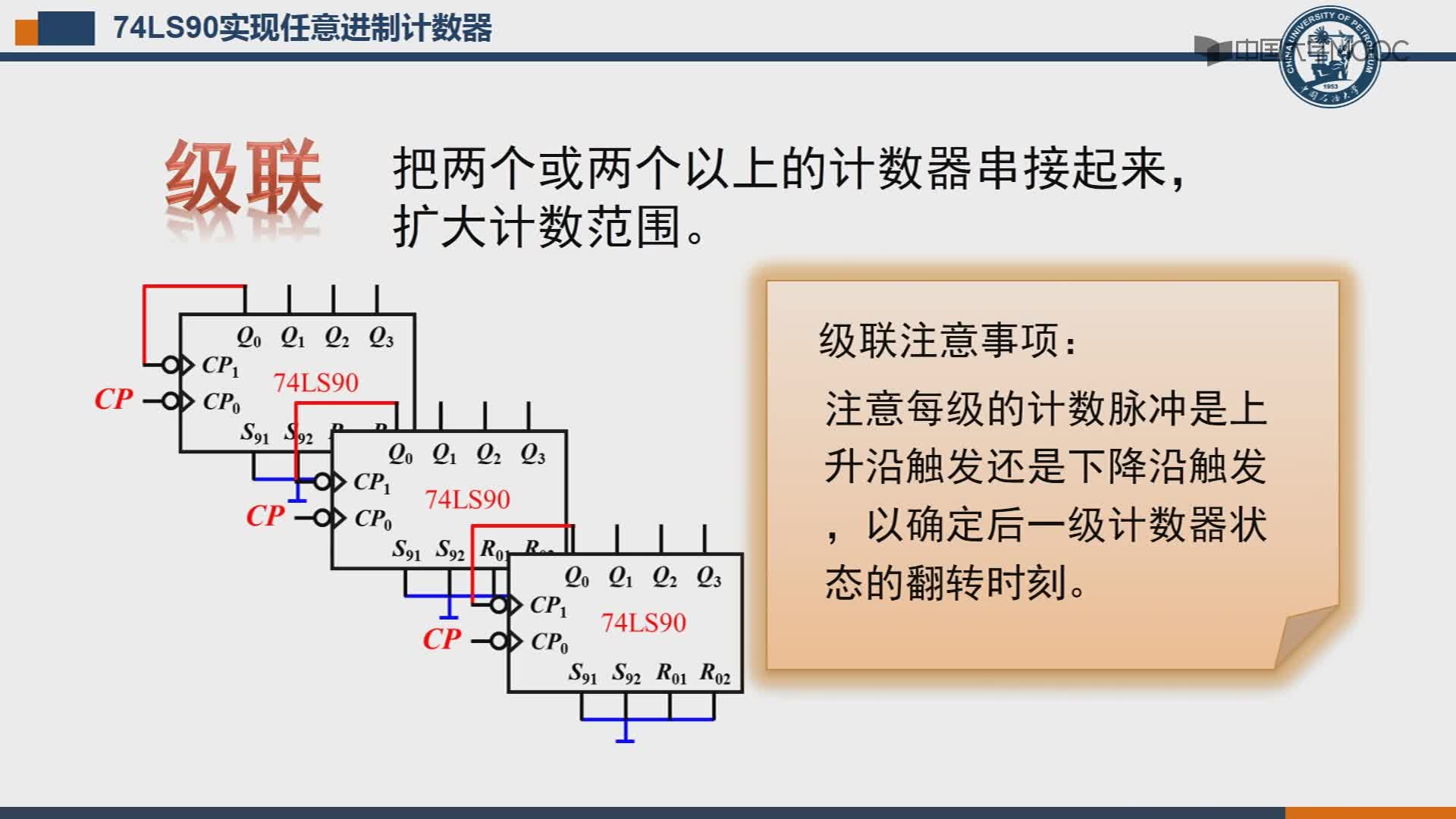

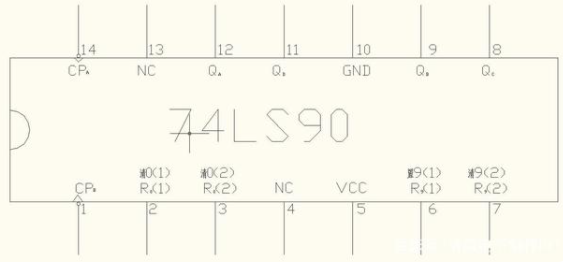

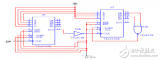

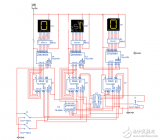

1) 兩芯片之間級(jí)聯(lián);把作高位芯片的進(jìn)位端與下一級(jí)up端連接這是由兩片74LS90連接而成的60進(jìn)制計(jì)數(shù)器,低位是連接成為一個(gè)十進(jìn)制計(jì)數(shù)器,它的clk端接的是低位的進(jìn)位脈沖。高位接成了六進(jìn)制計(jì)數(shù)器。當(dāng)輸出端為0101 的時(shí)候在下個(gè)時(shí)鐘的上升沿把數(shù)據(jù)置數(shù)成0000 這樣就形成了進(jìn)制計(jì)數(shù)器,連個(gè)級(jí)聯(lián)就成為了60進(jìn)制計(jì)數(shù)器,分別可以作為秒和分記時(shí)。

2) 方案的實(shí)現(xiàn):

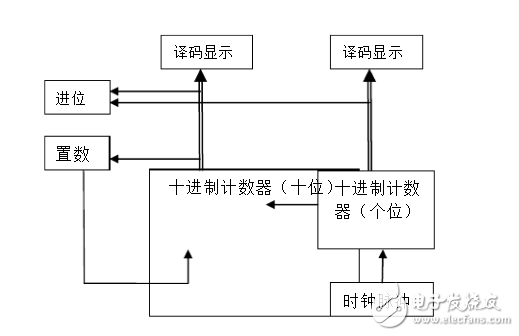

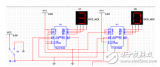

使用200HZ時(shí)鐘信號(hào)作為計(jì)數(shù)器的時(shí)鐘脈沖。根據(jù)設(shè)計(jì)基理可知,計(jì)數(shù)器初值為00,按遞增方式計(jì)數(shù),增到59時(shí),再自動(dòng)返回到00。此電路可以作為簡(jiǎn)易數(shù)字時(shí)鐘的分鐘顯示。下圖為60進(jìn)制計(jì)數(shù)器的總體框圖。

六十進(jìn)制計(jì)數(shù)器的設(shè)計(jì)與仿真

1.基本電路分析設(shè)計(jì)

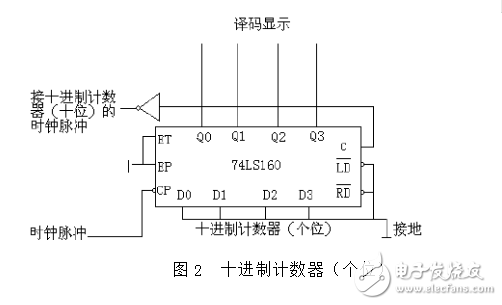

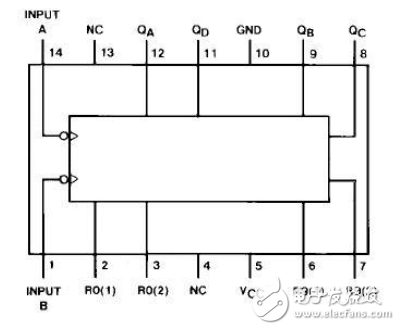

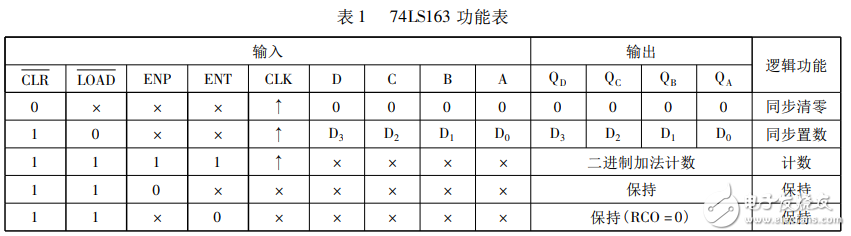

1) 十進(jìn)制計(jì)數(shù)器(個(gè)位)電路本電路采用74LS160作為十進(jìn)制計(jì)數(shù)器,它是一個(gè)具有異步清零、同步置數(shù)、可以保持狀態(tài)不變的十進(jìn)制上升沿計(jì)數(shù)器。

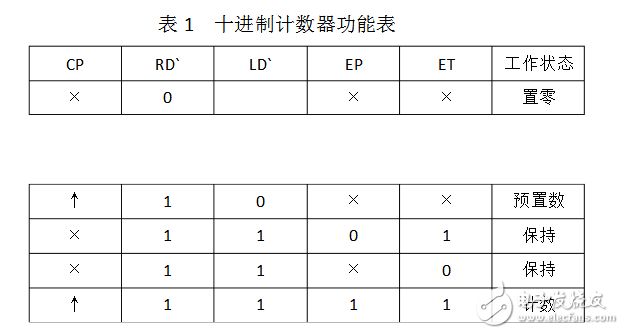

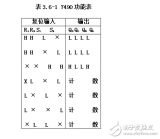

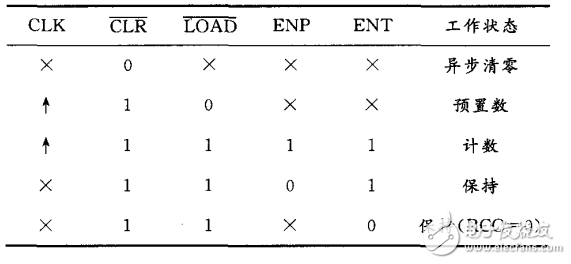

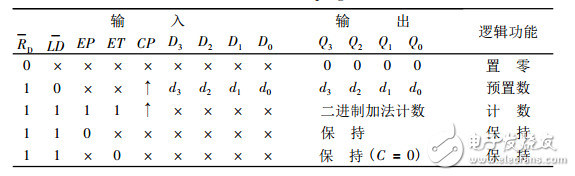

2) 功能表如下;

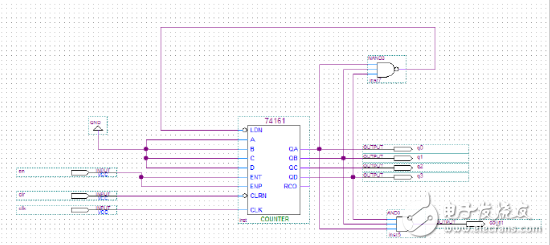

連接方式如下圖:

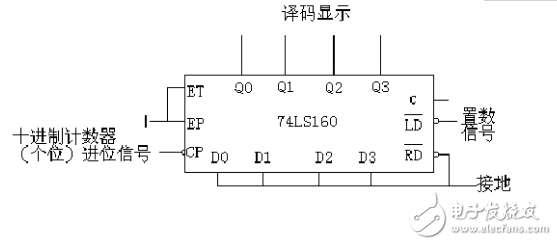

3) 十進(jìn)制計(jì)數(shù)器(十位)電路

圖3 十進(jìn)制計(jì)數(shù)器(十位)

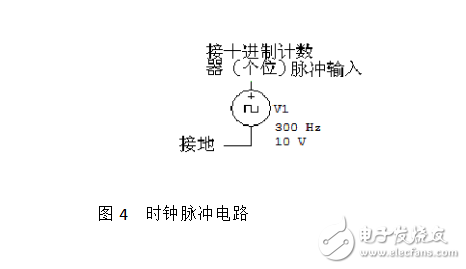

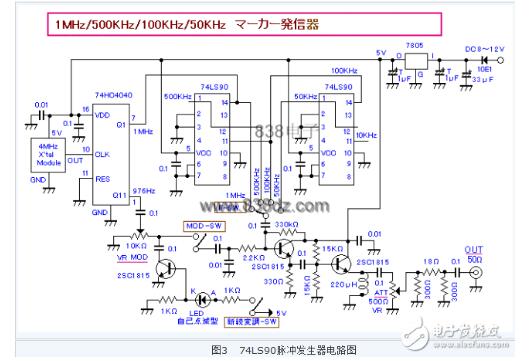

4) 時(shí)鐘脈沖電路

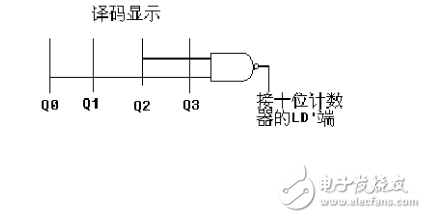

5) 置數(shù)電路

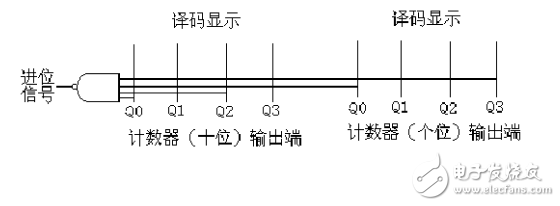

6) 進(jìn)位電路

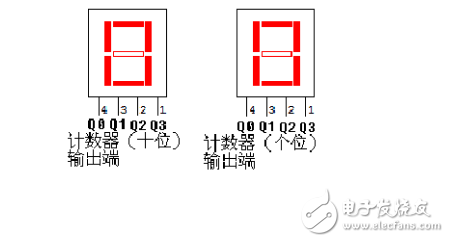

7)譯碼顯示電路

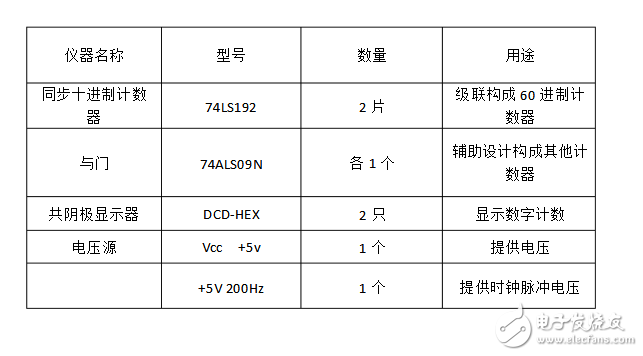

8)選定儀器列表

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論