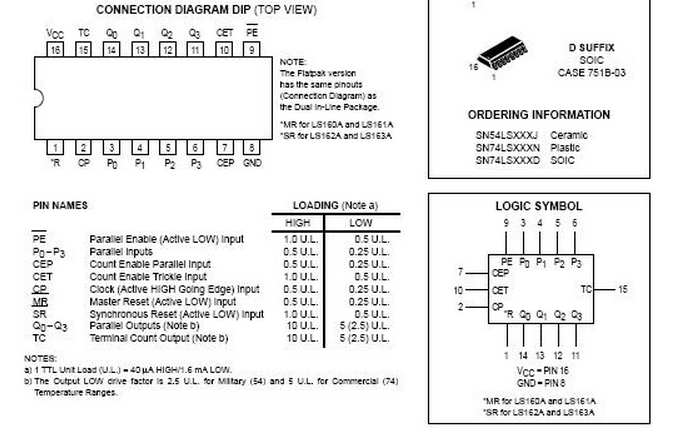

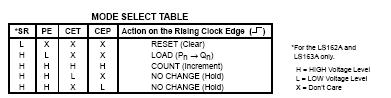

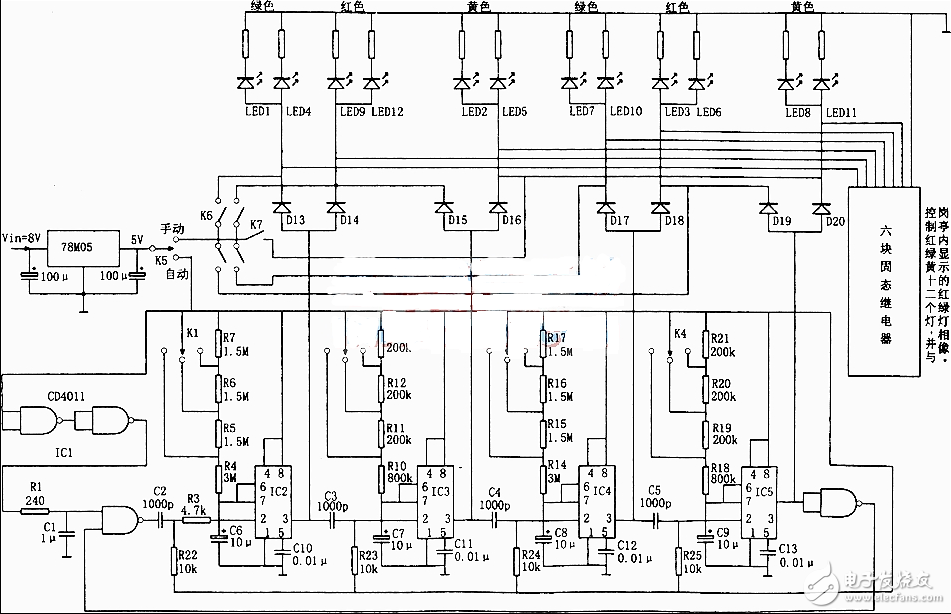

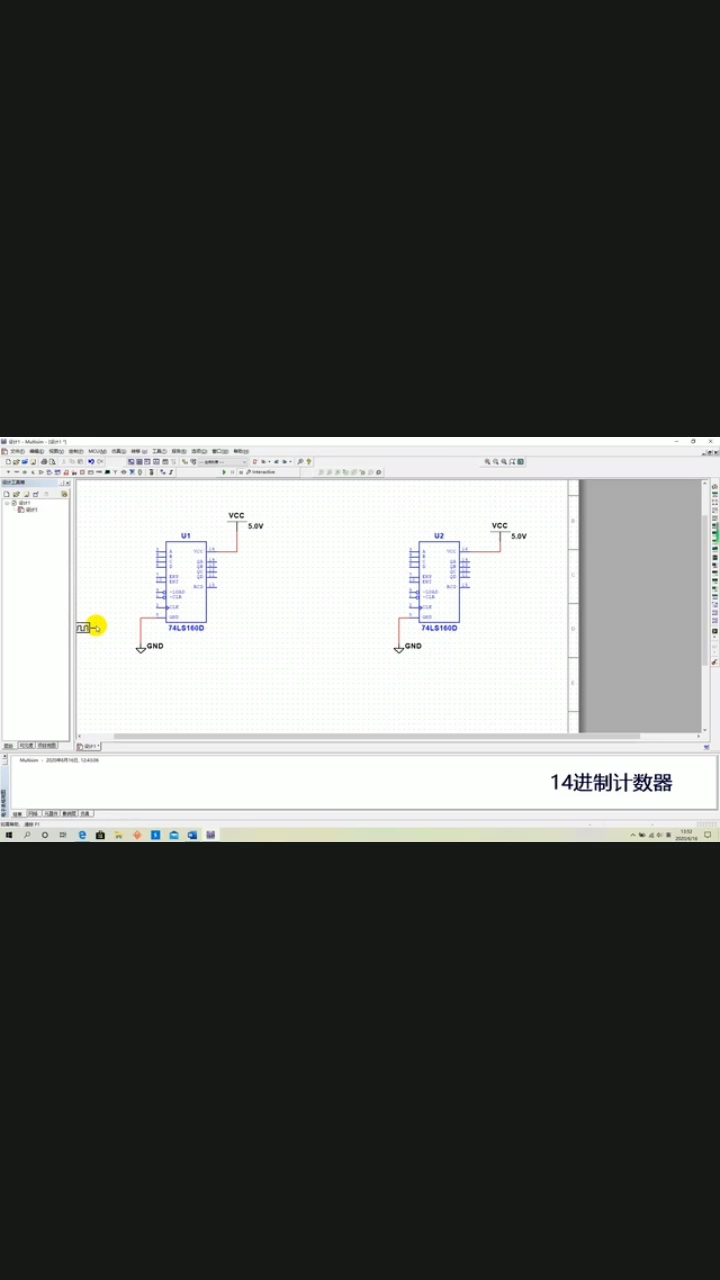

74ls160系列電路:

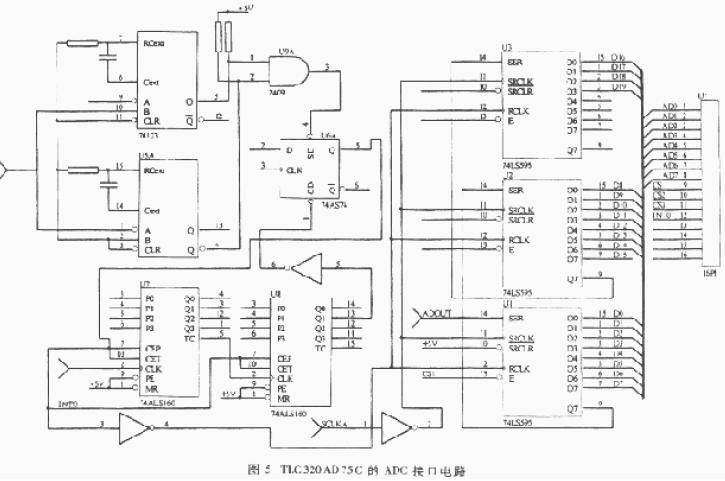

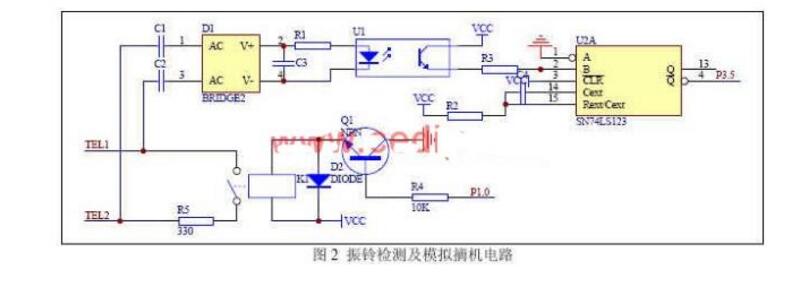

下圖是TLC320AD75C 的ADC 與MCS51 接口電路,DAC 接口電路是上述電路的逆過(guò)程,

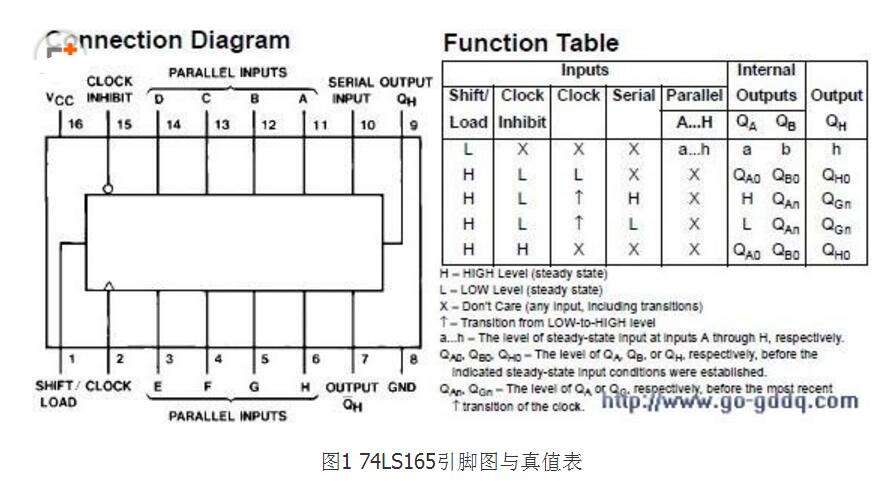

只要將8位輸出鎖存移位寄存器(三態(tài)、串入并出)74LS595 改成8位輸入鎖存移位寄存器

74LS597(三態(tài)、并入串出)即可,此處不再詳述。圖5與圖3的畫法一樣,鑒于篇幅的限

制,省略掉了一些電路細(xì)節(jié),讀者應(yīng)用本文中的電路時(shí)應(yīng)補(bǔ)上。下面簡(jiǎn)單講述一下圖5所示電

路的工作過(guò)程。根據(jù)圖4串行接口時(shí)序,要求利用LRCKA 和SCLKA 生成圖4(d)所示的脈

沖。在該脈沖的高電平期間20 位串行數(shù)據(jù)送到由三片74LS595 級(jí)聯(lián)而成的串入并出接口電路

中;在脈沖的下降沿將74LS595 中移位寄存器中的數(shù)據(jù)傳輸?shù)芥i存器;在脈沖的低電平期間發(fā)

中斷到MCS51 的INTO,MCS51 依次發(fā)出三個(gè)片選信號(hào),讀走該20 位數(shù)據(jù),從而完成一個(gè)聲

道的采集工作。因此如何產(chǎn)生圖4(d)所示的脈沖是本電路的核心問題。在圖5所示電路中,

74LS123 捕捉到的LRCKA 上升沿和下降沿通過(guò)線與的方式生成圖4(e)形式的極窄脈沖。在該

脈沖的低電平期間置位74LS74;兩片74LS160 接成20 進(jìn)制的計(jì)數(shù)器,在74LS74 輸出高電平

到來(lái)時(shí)對(duì)SCLKA 進(jìn)行計(jì)數(shù),當(dāng)計(jì)滿20 個(gè)脈沖時(shí)輸出一高電平脈沖,該脈沖經(jīng)一非門倒相去

74LS74 的復(fù)位端。74LS74 在上述的置位與復(fù)位作用下即產(chǎn)生圖4(f)所示的脈沖,同時(shí)在該脈

沖的低電平期間還要去清除計(jì)數(shù)器,停止計(jì)數(shù)器工作,直至該脈沖的下一個(gè)高電平到來(lái)。要指

出的是圖4(f)所示脈沖比圖4(d)所示的脈沖有一延遲,但只要該延遲時(shí)間小于T

SCLKA/2,即圖4(f)所示脈沖的上升沿比轉(zhuǎn)換開始后SCLKA 的第一個(gè)上升沿早,同步計(jì)數(shù)器

就可正確計(jì)數(shù),不會(huì)漏掉1位串行數(shù)據(jù)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論