個(gè)性化地定制自己的uvm代碼生成器模板和腳本

使用uvm代碼生成器創(chuàng)建基本的uvm驗(yàn)證環(huán)境框架,然后丟棄代碼生成器模板并擴(kuò)展和維護(hù)生成出來的代碼。....

ARM SMMU Data structure之Context Descriptors

是否進(jìn)行stage 1 translation,獲取stage 1 translation tabl....

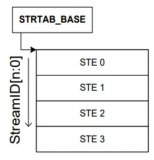

SMMU數(shù)據(jù)結(jié)構(gòu)格式之Level 1 Stream Table Descriptor介紹

上圖就是SMMU Level 1 Stream Table Descriptor的數(shù)據(jù)格式,簡稱Le....

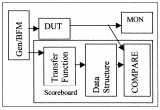

淺析芯片驗(yàn)證中的scoreboard

在芯片驗(yàn)證中,我們隨機(jī)發(fā)送數(shù)據(jù)激勵(lì),同時(shí)使用scoreboard進(jìn)行數(shù)據(jù)完整性檢查。

SMMU數(shù)據(jù)結(jié)構(gòu)格式之Stream Table Entry...V和Config介紹

更新一個(gè)valid STE時(shí)需要非常小心,因?yàn)榇藭r(shí)SMMU可能會訪問這個(gè)STE數(shù)據(jù),這其中存在著“競....

芯片驗(yàn)證中的checker和scoreboard介紹

典型的和驗(yàn)證組件相對比較獨(dú)立的checker,這些checker通常與時(shí)序相關(guān),例如檢查DUT中的狀....

芯片功能驗(yàn)證中的Sequences和Scenarios介紹

如果你做過功能驗(yàn)證并且開發(fā)過隨機(jī)用例,那么你就會知道場景組合會如雪球般地爆炸增長。

偽隨機(jī)數(shù)和真隨機(jī)數(shù)的區(qū)別是什么呢?

隨機(jī)驗(yàn)證中的隨機(jī)其實(shí)都是基于偽隨機(jī)發(fā)生器的,即每次都使用一個(gè)唯一的種子生成相應(yīng)的激勵(lì)。

功能驗(yàn)證在設(shè)計(jì)中的重要性

當(dāng)一家公司決定研發(fā)一款芯片時(shí),起初架構(gòu)師和幾位頂層設(shè)計(jì)一起創(chuàng)建一些需求、規(guī)范文檔。

淺析驗(yàn)證的激勵(lì)生成流程

在定向測試用例中,我們就是在不同的時(shí)刻將“0”或者“1”驅(qū)動(dòng)到接口總線上。如果我們希望提高這個(gè)總線操....

一個(gè)高效的現(xiàn)代EDA仿真驗(yàn)證流程

下圖是一個(gè)典型的EDA仿真驗(yàn)證環(huán)境,其中主要的組件就是激勵(lì)生成、檢查和覆蓋率收集。

受約束隨機(jī)驗(yàn)證的效果真的比直接用例測試好嗎?

當(dāng)介紹uvm驗(yàn)證時(shí)大家肯定都看過上面類似的圖片,以展示受約束的隨機(jī)驗(yàn)證相比直接用例測試如何具有先進(jìn)性....

UVM中的utility宏

UVM中所有的對象都應(yīng)該在factory 中注冊, utility 宏就是用于將對象注冊到工廠的。

使用SystemVerilog解決數(shù)組問題

數(shù)獨(dú)是一種非常流行的游戲,數(shù)獨(dú)本質(zhì)上也是一個(gè)約束問題,所以我們可以讓SystemVerilog的約束....

為什么不是uvm_transaction構(gòu)建UVM事務(wù)呢?

UVM 中的事務(wù)是一個(gè)具有信號屬性(例如地址和數(shù)據(jù))以及錯(cuò)誤、延遲等額外信息的類。總之,這個(gè)所謂事務(wù)....

一些有趣的數(shù)組相關(guān)的SystemVerilog約束

我們在工作中常常會針對數(shù)組施加各式的約束,下面列舉一下有趣的Systemverilog數(shù)組約束示例。

SystemVerilog coding過程中你在哪里聲明臨時(shí)變量

眾所周知,語句塊中需要用到的變量只能在語句塊最開始定義。

如何降低形式驗(yàn)證的復(fù)雜度?

當(dāng)計(jì)數(shù)器和內(nèi)存處于我們所需要證明斷言的邏輯錐中,它們可能是Formal無法完成證明的根本原因。

可以通過降低約束的復(fù)雜度來優(yōu)化Formal的執(zhí)行效率嗎?

我們可以通過降低約束的復(fù)雜度來優(yōu)化Formal的執(zhí)行效率,但是這個(gè)主要是通過減少Formal驗(yàn)證空間....

介紹一種能夠完成自然語言和SVA相互轉(zhuǎn)換的小工具

結(jié)論就是,SVA本身就是比較清晰的描述性語言,SVA和自然語言的轉(zhuǎn)換工具基本上沒有價(jià)值吧。

如何降低Formal assertion的復(fù)雜性呢?

分解一個(gè)復(fù)雜端到端斷言屬性的一種方法是基于模塊化分級斷言證明

介紹使用SVA的幾個(gè)優(yōu)勢

SVA支持多時(shí)鐘域(clock domain crossing (CDC))邏輯,例如異步FIFO。

SVA Assertion有什么優(yōu)勢?

如果我們設(shè)計(jì)正確工作時(shí)需要滿足FRAME_上升沿后的1~2拍會出現(xiàn)LDP_的下降沿,如下圖所示

System Verilog中的Mailboxes

Mailboxes是進(jìn)程間通信的另一種方式,但是比semaphores更強(qiáng)大,因?yàn)镸ailboxes....

SystemVerilog中的fork-join_none

fork-join_none和fork-join、fork-join_any的區(qū)別一樣在于進(jìn)程退出機(jī)....

SystemVerilog中的電平敏感事件控制

在verilog中絕大多數(shù)使用的都是邊沿敏感事件,例如@(posedge event)和@(nege....

SystemVerilog中的Semaphores

SystemVerilog中Semaphore(旗語)是一個(gè)多個(gè)進(jìn)程之間同步的機(jī)制之一,這里需要同步....