Allegro Package Designer Plus中設(shè)置Degassing向?qū)?/a>

? Cadence Allegro Package Designer Plus提供了一個(gè)完整的原理圖....

利用SIP Layout工具構(gòu)建PoP封裝結(jié)構(gòu)的方法

? PoP封裝結(jié)構(gòu) 將要?jiǎng)?chuàng)建的元件參數(shù)如下: 1、共有3顆die,上面封裝基板正面放置2顆, Wir....

如何使用SIP Layout建立PiP封裝結(jié)構(gòu)

? PiP封裝結(jié)構(gòu) 將要?jiǎng)?chuàng)建的元件參數(shù)如下: 1、共有2顆die,上方的封裝基板正面放置1顆,Wir....

什么是高密度DDR芯片

高密度DDR(Double Data Rate)芯片是一種先進(jìn)的動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器(DRAM)芯片,....

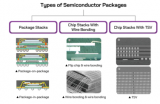

異構(gòu)集成封裝類型詳解

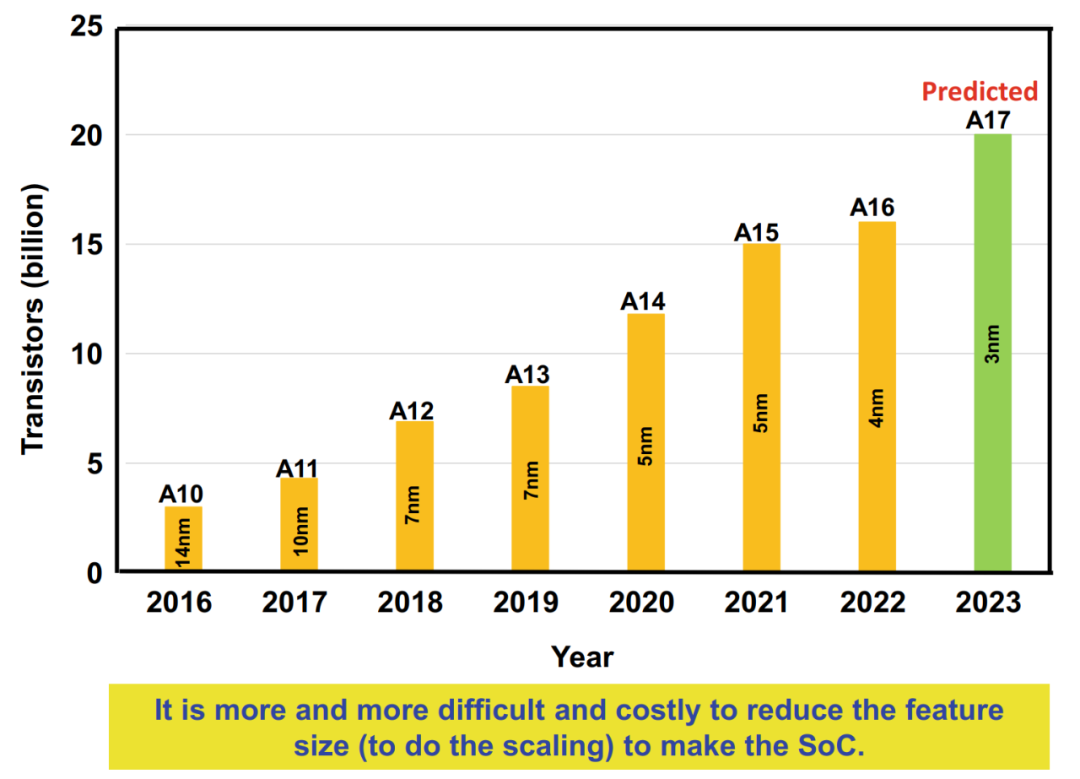

隨著摩爾定律的放緩,半導(dǎo)體行業(yè)越來(lái)越多地采用芯片設(shè)計(jì)和異構(gòu)集成封裝來(lái)繼續(xù)推動(dòng)性能的提高。這種方法是將....

堆疊封裝技術(shù)的類型解析

DDR作為一種內(nèi)存技術(shù)正朝著更高性能、更低功耗的方向發(fā)展。應(yīng)用前景廣闊,將對(duì)半導(dǎo)體、計(jì)算機(jī)、汽車、新....

淺談?dòng)⑻貭栐谙冗M(jìn)封裝領(lǐng)域的探索

隨著工藝節(jié)點(diǎn)的進(jìn)步,英特爾也在不斷推進(jìn)下一代封裝技術(shù)的發(fā)展。對(duì)高性能硅需求與工藝節(jié)點(diǎn)開發(fā)相結(jié)合,創(chuàng)造....

芯片封裝技術(shù)中不同術(shù)語(yǔ)的基本定義

在現(xiàn)代芯片封裝技術(shù)中,"bump" 和 “micro bump” 是用于不同封裝類型的關(guān)鍵組件,尤其....

如何提升Pspice仿真速度

OrCAD PSpice A/D和高級(jí)分析技術(shù)(A/A)結(jié)合了業(yè)界先進(jìn)的模擬、模數(shù)混合信號(hào)以及分析工....

一句話概括DDR、LPDDR、GDDR的區(qū)別

以DDR開頭的內(nèi)存適用于計(jì)算機(jī)、服務(wù)器和其他高性能計(jì)算設(shè)備等領(lǐng)域,目前應(yīng)用廣泛的是DDR3和DDR4....

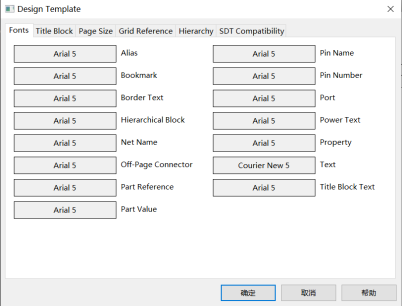

orcad capture修改元件庫(kù)后如何更新原理圖

OrCAD Capture是一款具有簡(jiǎn)單易用、功能特點(diǎn)豐富的電路原理圖輸入工具。

DSN設(shè)計(jì)差異深度技術(shù)指南與解析

DSN是當(dāng)前已經(jīng)打開原理圖文件; 02.DSN是需要對(duì)比的文件; Design Differene對(duì)....

Allegro中元器件位號(hào)重排并反標(biāo)回原理圖

因?yàn)槲惶?hào)重排是按照位置來(lái)的,所以應(yīng)在所有元器件位號(hào)絲印全部排列好后再進(jìn)行重排,推薦在出光繪之前進(jìn)行重....

Orcad CIS功能下原理圖Part參數(shù)更新指南

原理圖Part參數(shù)是指在設(shè)計(jì)電路時(shí),對(duì)于每個(gè)元件所需填寫的相關(guān)信息,如元件名稱、型號(hào)、封裝等。這些參....

卓越性能與微型化技術(shù)的完美融合—高密度DDR4芯片

在現(xiàn)代電子系統(tǒng)的核心組件中,內(nèi)存的性能與穩(wěn)定性至關(guān)重要。高密度DDR4芯片作為當(dāng)前內(nèi)存技術(shù)的杰出代表....

RDL線寬線距將破亞微米賦能扇出封裝高效能低成本集成

RDL 技術(shù)是先進(jìn)封裝異質(zhì)集成的基礎(chǔ),廣泛應(yīng)用扇出封裝、扇出基板上芯片、扇出層疊封裝、硅光子學(xué)和 2....

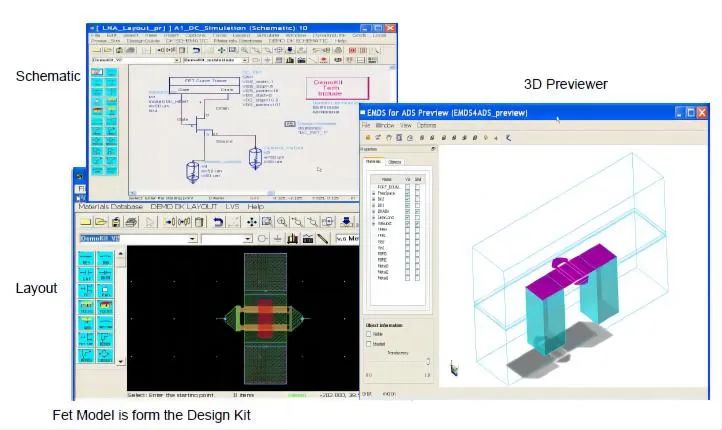

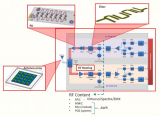

怎樣使用AWR軟件進(jìn)行MMIC產(chǎn)品開發(fā)的設(shè)計(jì)?

半導(dǎo)體器件為移動(dòng)設(shè)備、通信基礎(chǔ)設(shè)施和航空航天應(yīng)用提供卓越的射頻性能。

為什么需要封裝設(shè)計(jì)?

做過封裝設(shè)計(jì),做過PCB板級(jí)的設(shè)計(jì),之前和網(wǎng)友有過交流,問題是:為什么要封裝設(shè)計(jì)?信號(hào)完整性體系從大....

如何輕松完成剛?cè)峤Y(jié)合PCB彎曲的電磁分析?

憑借獨(dú)特的輪廓、高速互連、輕質(zhì)且高度可靠的柔性層壓板,剛?cè)峤Y(jié)合 PCB 廣泛適用于各種電子設(shè)備,從可....

2022 OrCAD 17.4 版本更新——十大亮點(diǎn)

增強(qiáng)的設(shè)計(jì)檢查功能添加新的選項(xiàng)-“在線DRC(Onine DRC)”,如果用戶選擇檢查某一項(xiàng)檢查項(xiàng)目....

PCB高速電路板Layout設(shè)計(jì)指南

為了滿足當(dāng)今電子產(chǎn)品的需求,數(shù)字電路的速度變得越來(lái)越快。高速設(shè)計(jì)曾經(jīng)是一個(gè)冷門的電子產(chǎn)品領(lǐng)域,但如今....

AWR Design Environment平臺(tái)新版本亮點(diǎn)功能和優(yōu)勢(shì)一覽

Cadence AWR Design Environment 平臺(tái)可提高工程團(tuán)隊(duì)的生產(chǎn)力并減少周轉(zhuǎn)時(shí)....

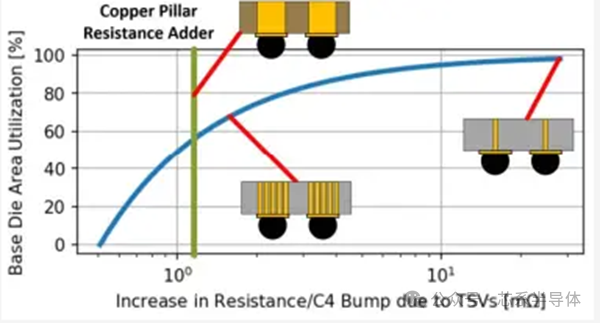

硅通孔設(shè)計(jì)有助于實(shí)現(xiàn)更先進(jìn)的封裝能力

硅通孔有三種設(shè)計(jì)樣式,用于連接中介層上堆疊的 3D 裸片,需要根據(jù)制造過程中的實(shí)現(xiàn)情況來(lái)選擇這些堆疊....