介 紹

傳統(tǒng)時(shí)序優(yōu)化的方法和訓(xùn)練方向主要集中在檢查和改善RTL代碼或是時(shí)序約束。盡管這種方法行之有效,但在實(shí)戰(zhàn)中因?yàn)榧夹g(shù)和商業(yè)方面的限制,很多更改都不可能真正的執(zhí)行下去。比如某些對設(shè)計(jì)比較大的修改,可能會(huì)讓產(chǎn)品的發(fā)布日期承擔(dān)滯后的風(fēng)險(xiǎn)。當(dāng)下盛行可重復(fù)使用的設(shè)計(jì)模塊,設(shè)計(jì)中經(jīng)常會(huì)出現(xiàn)不能輕易更改的第三方IP核。最糟糕情況的解決方案(“worstcase scenario” solution)也不過就是把目標(biāo)器件升級到一個(gè)更大的或是有更快速度等級的版本,盡管它們都將帶來一筆不小的花費(fèi)。

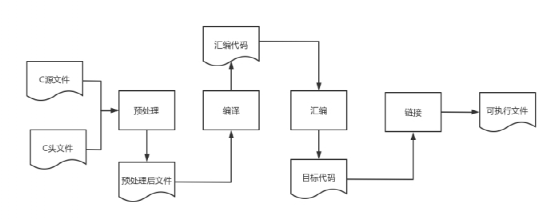

萬幸的是,當(dāng)今FPGA工具(比如Xilinx的 Vivado)都有很多開關(guān)和設(shè)置選項(xiàng)來幫助時(shí)序收斂。InTime的方法,就是通過調(diào)整FPGA工具的編譯過程來解決用戶的時(shí)序問題和其他性能問題。Xilinx 的ISE和Vivado軟件包含了很多綜合和布局布線的參數(shù),每一項(xiàng)都至少有兩個(gè)值可以直接影響最終結(jié)果。InTime幫助設(shè)計(jì)師深入挖掘這些工具的性能,以達(dá)到要求的結(jié)果。

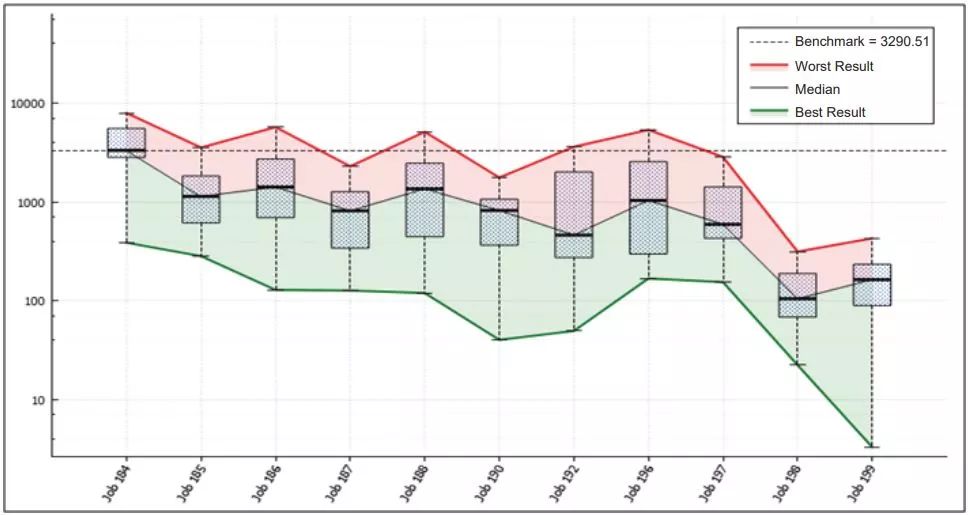

上圖是一個(gè)客戶案例,X軸代表采用不同綜合和布局布線的編譯批次,Y軸顯示的是失敗最差余量(Failing Worst Slack, 0代表時(shí)序通過)的絕對值,單位為納秒。在這里您可以清楚地看到InTime把失敗最差余量從-0.45ns (-450ps) 減少到了0ns,僅通過調(diào)整編譯參數(shù)就達(dá)到了時(shí)序目標(biāo),而且對設(shè)計(jì)沒有任何變動(dòng)。

很多情況下,用戶經(jīng)常使用默認(rèn)的綜合和布局布線的參數(shù)。因?yàn)椴淮_定會(huì)有什么后果,很少有人會(huì)嘗試改變這些參數(shù)。再加上很多參數(shù)是相互聯(lián)動(dòng)的,多個(gè)參數(shù)如果被同時(shí)設(shè)置錯(cuò)誤會(huì)讓時(shí)序變得更加糟糕;所以調(diào)試參數(shù)這項(xiàng)任務(wù),就變得更加舉步維艱。

更多內(nèi)容還請點(diǎn)擊 “閱讀原文”,下載白皮書

了解InTime的流程

優(yōu)化設(shè)計(jì)的步驟

步驟一:生成數(shù)據(jù)

步驟二:使用“Deep Dive”配方

步驟三:Auto Placement配方或Extra Optimization 配方

云端運(yùn)行InTime和Vivado

結(jié)論

-

IP核

+關(guān)注

關(guān)注

4文章

329瀏覽量

49549 -

編譯

+關(guān)注

關(guān)注

0文章

659瀏覽量

32912

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA設(shè)計(jì)時(shí)序約束指南【賽靈思工程師力作】

選擇賽靈思(Xilinx)FPGA 7系列芯片的N個(gè)理由

直接在Vivado上用亞馬遜云來編譯優(yōu)化設(shè)計(jì)~

用FPGA 嵌入式處理器實(shí)現(xiàn)高性能浮點(diǎn)元算

基于賽靈思FPGA的卷積神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)設(shè)計(jì)

賽靈思ISE? 設(shè)計(jì)套件11.1版對FPGA有什么優(yōu)化作用?

如何利用賽靈思28納米工藝加速平臺(tái)開發(fā)?

基于Xilinx的InTime優(yōu)化設(shè)計(jì)及流程詳講

從賽靈思FPGA設(shè)計(jì)流程看懂FPGA設(shè)計(jì)

賽靈思的AI平臺(tái)斬獲“2019 年度最佳視覺產(chǎn)品獎(jiǎng)”

賽靈思推出首個(gè)基于機(jī)器學(xué)習(xí)優(yōu)化算法 FPGA EDA 工具套件

賽靈思Vivado ML版優(yōu)化應(yīng)用設(shè)計(jì)

賽靈思軟件通過調(diào)整編譯參數(shù)以及運(yùn)行并行編譯來優(yōu)化FPGA時(shí)序性能

賽靈思軟件通過調(diào)整編譯參數(shù)以及運(yùn)行并行編譯來優(yōu)化FPGA時(shí)序性能

評論