觸發器是順序電路的基本構建模塊,可以從一種形式轉換為另一種形式,能夠存儲單個數據位

我們在整個電子教程部分已經看過順序邏輯觸發器將無限期地保持其兩種穩定狀態之一,直到應用某種形式的外部觸發脈沖使其改變狀態。

作為觸發器是雙穩態器件,這些時序電路有時被稱為“鎖存器”,因為它們的輸出被鎖定或鎖存到其輸入狀態,直到其輸入條件發生另一次變化。

我們還看到雙穩態翻轉 - 觸發器是時序邏輯電路中最基本的存儲元件,并且可以配置為通過互連兩個反相門來產生簡單的存儲器元件以產生反饋。注意,組合邏輯電路不需要任何形式的存儲器,因此不使用觸發器。然而,時序邏輯電路確實具有存儲器,因此使用各種類型的觸發器設計來記住它們的當前狀態。

數字邏輯門的互連以產生存儲器件導致諸如開關去抖電路的應用此外,由雙穩態鎖存器構成的存儲器元件構成了累加器和寄存器的基礎,計算機或微控制器在其上進行復雜的算術運算。

創建單個一位觸發器的最基本方法是使用兩個 NOR門門,如圖所示。通過使用交叉耦合門并將輸出從一個門饋送到另一個門的輸入端(輸入 - 輸出互換),電路具有閉環(正反饋),因此其輸出取決于輸入的狀態,使得電路順序并具有存儲器。

觸發器也屬于一類稱為多諧振蕩器的數字開關電路。基本雙穩態多諧振蕩器是一種再生電路,具有兩個有源數字門,設計成當一個數字門導通時,另一個門被截止,反之亦然。這兩個數字門產生兩個穩定的輸出,包括HIGH和LOW,其中一個是另一個的補碼。

但我們可以制作許多不同類型的異步和同步觸發器電路(異步翻轉 - 觸發器不需要時鐘信號輸入,但是同步的那個來自基本的交叉耦合NANDGates和NORGates,不同類型之間的觸發器的轉換有時會有點混亂。

基本上有四種不同類型的人字拖,這些是:

1。置位復位(SR)觸發器或鎖存器

2。 JK觸發器

3。 D(數據或延遲)觸發器

4。 T(Toggle)觸發器

為了幫助我們更好地理解可用的不同類型的觸發器,以下順序邏輯教程向我們展示了如何進行觸發器的轉換簡單地通過修改從SR觸發器開始的特定類型觸發器的輸入,從一種類型到另一種類型。

Set-Reset SR觸發器

所有雙穩態鎖存器和雙穩態多諧振蕩器中最基本的是置位(SR)觸發器。基本的SR觸發器是一個重要的雙穩態電路,因為所有其他類型的觸發器都是由它構建的。 SR觸發器使用兩個交叉耦合數字 NAND門構建,例如TTL 74LS00,或兩個交叉耦合數字 NOR門,例如TTL 74LS02。 / p>

通常認為SR雙穩態和觸發器是透明的,因為它們的輸出會改變或立即響應其輸入的變化。此外,由于它們由數字邏輯門和反饋組成,因此SR觸發器被視為異步時序邏輯電路。

基本SR觸發器有兩個輸入 S (設置)和 R (復位)和兩個輸出 Q 和 Q ,其中一個輸出是另一個的補充。然后SR觸發器是雙輸入,雙輸出設備。考慮下面的電路。

基本NAND和NOR SR觸發器

以上是使用負輸入 NAND 門或正輸入 NOR 門的異步SR雙穩態觸發器的兩種基本配置。對于使用兩個交叉耦合 NAND 門的SR雙穩態鎖存器,兩個輸入通常為高電平,邏輯電平為“1”。

在邏輯電平“0”施加低電平當 R 保持為高電平時 S 輸入使輸出 Q 變為高電平,設置鎖存器。同樣,輸入 S 保持為高電平的 R 輸入上的邏輯電平“0”會使 Q 輸出變為低電平,從而復位鎖存器。對于SR與非門鎖存器,禁止 S = R = 0 的條件。

使用兩個交叉耦合 NOR來觸發觸發器的轉換

gate,當輸出 Q = 1 且 Q = 0 時,雙穩態鎖存器被稱為處于置位狀態。當 Q = 0 且 Q = 1 時, NOR 門鎖存器被稱為處于復位狀態。然后我們可以看到 NOR 和 NAND 門觸發器的操作基本上只是彼此的補充。

執行使用兩個交叉耦合 NAND 門的SR觸發器需要低輸入。但是,我們可以通過使用逆變器將 NAND SR觸發器的操作轉換為與 NOR 門實現相同的方式,具有有效HIGH(正邏輯)輸入,( NOT Gates )在基本雙穩設計中。

然后將觸發器從低電平有效轉換為有效高電平輸入的方式如下:

有效HIGH觸發器

上面的基本SR觸發器及其高效的HIGH等效,都是異步類型觸發器,意味著它的輸入和當前狀態決定了下一個狀態。但作為一位存儲器存儲器件,我們可能希望它保持其當前輸出狀態,而不管其兩個輸入發生了什么,并且可以通過包含額外輸入來修改基本SR觸發器的操作來控制其行為。雙穩態電路。

觸發器基本電路的轉換是通過使用兩個額外的 AND 門來實現的,它們與控制輸入一起啟用和禁用 S 和 R 輸入。這個新電路稱為時鐘或門控SR觸發器。

門控置位 - 復位(SR)觸發器

門控SR觸發器按順序操作,其輸出狀態僅響應其在時鐘應用或使能輸入上的輸入而改變。由于通過該時鐘使能輸入控制輸出的改變,所以門控SR觸發器電路被稱為“同步”觸發器。然后異步SR觸發器不需要時鐘,但是同步的那個。

基于標準 NOR 的SR觸發器到門控SR觸發器的轉換是使用連接到置位和復位輸入的兩個 AND 門(TTL 74LS08)實現。附加控制或“啟用”輸入 EN 連接到 AND 門,當時鐘輸入為低電平時,輸出為低電平,如圖所示。

門控SR觸發器電路

時鐘或使能輸入, EN 連接到兩個 AND 門的兩個輸入之一,當使能輸入為低電平(AND門控原則)時,產生低電平輸出。然后,對輸入 S 或 R 的任何更改都不會影響輸出的狀態, Q 和 Q 觸發器。

當使能輸入為高電平時,兩個 AND 門變為透明,因此對輸入 S 和 R的任何更改將像以前一樣改變輸出的狀態。然后我們可以看到邏輯電平“1”(高電平)或“0”(低電平)可以通過向時鐘使能輸入施加高電平來存儲在門控觸發器的輸出端,并且該輸出當啟用輸入保持為低電平時,無論輸入條件如何,狀態都可以保留任何所需的時間段。

門控觸發器符號

由于門控SR觸發器是三輸入設備,邏輯符號顯示三個輸入: S , R 和 EN 。 EN 輸入標有一個小三角形,表示觸發器響應邊沿或轉換輸入。

觸發器轉換為時鐘觸發器通過簡單地將該使能輸入連接到定時信號來實現。輸出狀態的任何變化都將與時鐘 CLK 信號同步發生。注意,時鐘信號被定義為一系列連續脈沖,每個脈沖具有兩個獨立的狀態,即“ON”狀態和“OFF”狀態,其占空比代表其“ON”時間除以總的時間周期。脈沖,(“ON”時間+“OFF”時間)。幾乎所有數字時鐘信號都具有50%的占空比。

時鐘SR觸發器可以在時鐘信號的上升沿或下降沿或脈沖的下降沿改變狀態。因此,當時鐘脈沖從一個電平變為另一個電平時,邊沿觸發的觸發器僅響應或改變狀態。例如,HIGH到LOW或LOW到HIGH。

正邊沿觸發觸發器的輸出僅在時鐘脈沖的上升沿(0到1)改變狀態而不是應對下降的負邊緣。同樣,負邊沿觸發的觸發器在時鐘脈沖的下降沿(1到0)改變狀態,并且不響應上升的正沿。

門控SR觸發器預設和清除

我們可以進一步采用這個門控SR觸發器電路來生成一個雙穩態鎖存器,其中包含額外的輸入,稱為預設和清除輸入可用于將觸發器設置為獨立于時鐘的初始狀態。我們可以覆蓋所有輸入并將輸出預設為已定義的狀態,而不是輸出 Q 和 Q 加載未定義的值。

<但是,為什么我們要這樣做呢?當電源首次施加到觸發器電路時,輸出的初始邏輯狀態可以完全隨機,這取決于首先鎖存哪個邏輯門,然后我們不知道觸發器電路處于哪個開關狀態。因此觸發器的初始狀態是不確定的,因為它可能處于SET狀態,( Q = 1 )或者它可能處于RESET狀態,( Q = 0 預設, PR 和清除, CLR 如圖所示。

具有預設和清除輸入的觸發器

>

當CLEAR輸入為“0”且PRESET輸入為“1”時,這些附加輸入允許清除觸發器( Q = 0 ) ”。同樣,只要PRESET輸入為“0”且CLEAR輸入為“1”,觸發器就可以預置為邏輯“1”狀態。在此示例中,如果PRESET和CLEAR輸入為高電平有效( P = CLR = 1 ),則電路作為普通門控SR觸發器電路工作。很明顯,PRESET和CLEAR輸入不應同時處于低電平有效( P = C = 0 ),因為這會導致狀態不確定。

此PRESET和CLEAR如果我們想要在準備下一個序列的順序操作期間將觸發器置于已知的置位或復位狀態,那么選項也很方便。

將觸發器從一種類型轉換為另一種類型通過修改連接或使用額外的門很容易實現。正如我們所看到的,基本的SR觸發器有兩個輸入, S 和 R 來存儲單個位,但要做到這一點,我們必須同時激活這兩個輸入。此外,禁止輸入組合: S = R = 1 可能會意外發生,從而導致SR觸發器切換到未定義狀態。

消除對兩個獨立的輸入和無意切換到不確定狀態的可能性,通過在置位和復位輸入之間連接一個反相器(非門),我們可以將基本的RS觸發器轉換為D型觸發器。

(數據)D型觸發器

D型觸發器或數據鎖存器只有一個輸入,稱為“D”,或數據輸入,加上時鐘輸入, CLK 以及通常的兩個輸出, Q 和 Q 。在延遲一個時鐘脈沖之后,D型觸發器在輸入和輸出之間傳輸其數字數據,因此“D”部分也稱為“延遲”輸入。

通過簡單地連接 S 和 R 輸入之間的反相器,可以輕松地從SR觸發器構建D型觸發器,從而連接到逆變器的輸入到 S 輸入,并且變頻器的輸出連接到 S 輸入,如圖所示。

D型觸發器

上面給出了將觸發器轉換為D型的兩種不同電路。頂部電路是傳統的門控D型配置,帶有額外的逆變器。底部電路以完全相同的方式工作,但沒有逆變器,節省了一個門。與所有觸發器配置一樣,D型觸發器可以使用 NAND 或 NOR 門實現,無論是否有額外的預設和清除。

在輸入之間使用逆變器可確保 S 和 R 輸入始終是彼此的補充,從而消除了以下不確定條件: S = R = 1 。因此,D型觸發器也稱為“透明鎖存器”,因為當時鐘輸入為高電平時輸出 Q 跟隨 D 輸入, CLK = 1 將輸入端的二進制信息直接傳送到輸出端,就像觸發器不存在一樣,使其透明。

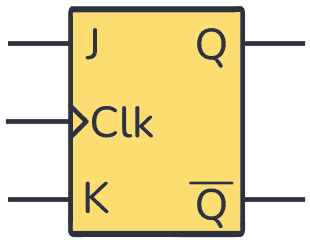

JK觸發器

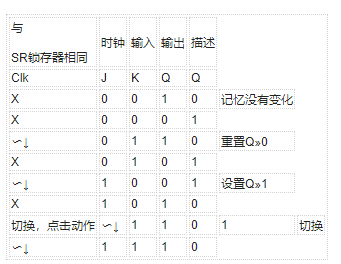

JK觸發器在許多方面與之前的SR觸發器非常相似,可能是所有觸發器設計中使用最多的。術語“J”和“K”并不真正意味著或涉及任何特殊描述,而是最初在觸發器初始開發時使用的,因為這兩個字母不用作任何其他數字設備的一部分。對于JK觸發器,“J”相當于Set,“K”相當于Reset。

我們之前看到SR觸發器有兩個或者可能有三個有意義的輸入組合不允許 S = R = 1 組合的輸入序列,但可以輕松修改它以實現不同的切換功能。然后JK觸發器通常被認為是通用器件。

JK觸發器有兩個輸入“J”和“K”,因此所有四種可能的輸入配置:無變化,設置,重置和切換有效。 “J”輸入的作用類似于“S”,“K”輸入的作用類似于“R”,當其中一個輸入為高電平時,它會改變狀態。然而,JK觸發器的優點在于,當“J”和“K”都為邏輯“1”時為高電平時,觸發器會切換,即從“0”變為“1”或從“1”變為“1”。 “到”0“產生自己的補充狀態。

JK觸發器電路

將觸發器轉換為JK觸發器是通過額外的3輸入將 Q 和 Q 輸出與 S 和 R 輸入交叉連接AND 門如圖所示。

如果 J 和 K 輸入都為HIGH,邏輯“1”則為 Q只要時鐘輸入( CLK )為HIGH,輸出就會改變狀態(Toggle)。因此,輸出將是不穩定的,從而產生這種基本JK電路的競爭問題。通過確保時鐘輸入僅在非常短的時間內處于邏輯“1”,或者產生稱為主從觸發器的更復雜的JK觸發器電路,可以避免這個問題。

主從觸發器

將觸發器轉換為“主從”配置涉及添加第二雙穩態電路。主從配置由兩個級聯連接的SR鎖存器組成。一個雙穩態觸發器作為主器件接收外部輸入,而另一個作為其從器件,直接從主觸發器獲取其輸入,如圖所示。

基本主從配置

當時鐘 CLK 脈沖變為高電平時, S 和 R 輸入正常通過主觸發器 FF A 傳輸。然而,相鄰的從觸發器 FF B 保持隔離,因為其時鐘輸入, CLK 為低電平,邏輯“0”由于反轉通過反相器。

現在當初始時鐘脈沖返回LOW為“0”時,主機被禁用并阻止外部數據輸入傳遞信息到其輸出,而從機觸發器現在變為啟用狀態并因此將鎖存的信息傳遞到 Q 和 Q 的輸出。然后輸入到從觸發器的時鐘是主觸發器的時鐘輸入的補充。

主從觸發器被稱為電平觸發或脈沖觸發雙穩態,因為在輸入時鐘脈沖處于高電平的整個時間內讀取輸入數據。此外,主從觸發器不僅限于SR主從。還有JK主從和D型主從觸發器。在幾乎所有的觸發器中,從觸發器都是標準的SR觸發器,而觸發器的類型則來自主器件,它將是SR,JK或D型配置。

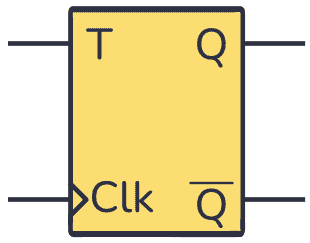

(Toggle)T型觸發器

T型(切換)觸發器是單輸入雙穩態,其操作類似于上面的D型。我們在上面看到了JK觸發器配置,如果 J = K = 1 ,它的輸出將在下一個時鐘周期的應用中切換。然后將觸發器轉換為Toggle類型只是將輸入連接為HIGH的問題。

T型觸發器在商業上不可用,但可以用JK觸發器構建(或者,通過將 J 輸入與 K 輸入連接,并將兩者都連接到邏輯電平“1”,或者D型觸發器。當 J 且 K 為高電平時,觸發器每次在其時鐘輸入觸發時都會改變狀態。此時鐘輸入現在稱為“切換輸入”,如果輸出變為“1”則為“1”,如果為“1”則輸出為“0”,即切換為“0”。

切換T型觸發器

當應用時鐘輸入時,切換觸發器改變狀態, T = 1 并在 T = 0 時保持不變。然后從“0”到“1”的轉換將導致輸出切換,為觸發器命名。撥動T型觸發器是許多數字電路的基本構建模塊,包括分頻器和數字計數器。

Toggle T型觸發器可以用兩種簡單的方式從JK觸發器構造。首先, J 和 K 輸入可以連接在一起,如圖所示,時鐘輸入變為切換,如圖所示。第二種方法是將 J 和 K 輸入連接在一起,以提供切換輸入,時鐘輸入保持不變。當 T 和 CLK =或等于“1”時,輸出切換。當 T 或 CLK 為低電平時,輸出保持不變。

數據D型觸發器可以像JK觸發器一樣轉換通過將 Q 輸出直接連接到D輸入,并將切換信號 T 作為時鐘輸入,如上所示,作為觸發器執行。將 Q 連接到輸入會產生負反饋。

由于來自切換觸發器的輸出在每次應用時鐘信號時改變狀態,因此其輸出頻率為 - 輸入信號頻率的一半,從而充當分頻器。如果更多的觸發觸發器級聯在一起形成一個鏈,因為第一個觸發器的輸出充當級聯排列中第二個T觸發器的時鐘,第二個觸發器充當時鐘輸入對于第三個T觸發器等,沿鏈創建一個分頻。

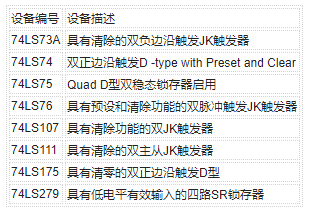

觸發器和鎖存器是順序邏輯電路最基本的構建模塊。因此,許多IC制造商生產各種不同的觸發器芯片,使用下面列出的TTL和CMOS技術。

流行的觸發器IC類型

觸發器轉換摘要

我們在本教程中已經看到雙穩態設備是存在兩個明確定義的狀態的設備,并且設備可以隨時采用任一穩定狀態。觸發器從一種類型到另一種類型的轉換可以非常容易地完成,因為只需要稍微修改就可以將一種類型轉換成另一種類型。可以使用帶反饋的邏輯門電路構建觸發器。

我們還看到觸發器可以有一個,兩個或三個輸入,其中一個輸入連接到時鐘信號。所有觸發器都有兩種輸出狀態: Q = 1 和 Q = 0 ,它們響應時鐘的應用而變化。對于SR鎖存器, S = 1 設置 Qto1 , R = 1 重置 Qto0 。

JK觸發器被歸類為通用觸發器,其設計與SR觸發器類似,當 J = 1 時,它設置 Qto1 ,當 K = 1 時,它會重置 Qto0 。條件 J = K = 1 導致 Q 切換。

上面討論的所有觸發器都可以有額外的異步CLEAR和PRESET輸入,使 Q 被清除為“0”或預設為“1”,與時鐘信號無關。 / p>

D型雙穩態可以通過在 J 和 K 輸入之間增加一個逆變器來構建JK觸發器。 D型觸發器廣泛用于數字系統以傳輸數據,據說是透明的,因為輸入中的任何機會都會被立即接受,輸出也會相應改變。

T或切換翻轉 - 當 T = 1 時,翻轉會改變應用時鐘脈沖的狀態,否則 Q 不會改變。觸發器觸發器通常用于分頻或設計二進制計數器,因為二進制計數器需要互補。切換觸發器不是商用的,但可以通過將JK觸發器的 J 和 K 輸入連接在一起來實現。

通過重新配置輸入或通過添加額外的邏輯門,通常可以將觸發器從一種類型轉換為另一種類型,我們已經看到SR觸發器可以轉換為JK觸發器本身可以轉換為數據鎖存器,JK觸發器和D型都可以轉換為T型觸發器。

-

邏輯門

+關注

關注

1文章

142瀏覽量

24086 -

算術運算

+關注

關注

0文章

6瀏覽量

5703 -

人字拖

+關注

關注

0文章

2瀏覽量

6848

發布評論請先 登錄

相關推薦

JK人字拖觸發器和函數表

Impact Footwear推出下一代3D打印人字拖:個性化定制自己的拖鞋

具有清除和預設的雙正邊緣觸發D型觸發器SNx4LVC74A數據表

人字拖的轉換觸發器預設和清除配置類型摘要

人字拖的轉換觸發器預設和清除配置類型摘要

評論