摘要: 針對(duì)當(dāng)前無人機(jī)數(shù)據(jù)鏈日趨小型化,采用射頻收發(fā)一體化設(shè)計(jì),基于FPGA 對(duì)零中頻射頻收發(fā)器AD9361 進(jìn)行配置,實(shí)現(xiàn)機(jī)載視頻和遙控遙測(cè)的無線傳輸。測(cè)試結(jié)果表明,該設(shè)計(jì)可以實(shí)現(xiàn)無人機(jī)與地面站之間數(shù)據(jù)的可靠傳輸,同時(shí)滿足小型無人機(jī)對(duì)數(shù)據(jù)鏈體積、重量、功耗和低成本的要求。

無人機(jī)數(shù)據(jù)鏈?zhǔn)菍?shí)現(xiàn)無人機(jī)與地面站之間雙向傳輸信息的無線通信系統(tǒng),主要完成機(jī)載視頻的實(shí)時(shí)下傳、載荷控制及狀態(tài)回報(bào)和遙控遙測(cè)信息的分發(fā)[1]。其中射頻收發(fā)系統(tǒng)是無線傳輸?shù)闹匾M成部分,針對(duì)小型無人機(jī)數(shù)據(jù)鏈體積小、重量輕、功耗低等特點(diǎn),一般的集成式寬帶收發(fā)器解決方案在性能、可調(diào)帶寬方面受限,缺乏實(shí)現(xiàn)實(shí)用性; 而分立式軟件定義無線電( SDR) 的設(shè)計(jì)成本高昂,缺乏有效的硬件和RF 信號(hào)鏈設(shè)計(jì)技術(shù),從而導(dǎo)致開發(fā)周期過長(zhǎng),因此,需要一款高度集成式軟件定義RF 收發(fā)器[2]。集成式RF 收發(fā)器AD9361 的優(yōu)勢(shì)在于為多種無線電方案提供統(tǒng)一的可再編程軟件無線電平臺(tái),具備出色的靈活性和可配置性以及支持現(xiàn)場(chǎng)升級(jí)[3]。

姜浩等人提出采用PC + FPGA 配置AD9361 的方法,PC 機(jī)通過PCIe 接口將配置指令發(fā)送到FPGA,F(xiàn)PGA 通過SPI 接口發(fā)送配置指令到AD9361[4]。Jorge Santos 等人提出采用FPGA + MicroBlaze的方案配置AD9361,并在Xilinx KC705 開發(fā)板上進(jìn)行了實(shí)現(xiàn)和驗(yàn)證[5]。方良提出利用FPGA+ ARM 的方式實(shí)現(xiàn)AD9361 的配置,基于Zedboard和AD9361子板建立軟件無線電平臺(tái)進(jìn)行雙向視頻的傳輸[6]。本文提出一種FPGA 獨(dú)立實(shí)現(xiàn)AD9361配置的方案,該方案滿足小型數(shù)據(jù)鏈對(duì)于功耗、體積和成本的嚴(yán)苛要求,同時(shí)不受FPGA 型號(hào)的限制,可方便移植于不同的FPGA 平臺(tái)。

1 整體系統(tǒng)方案

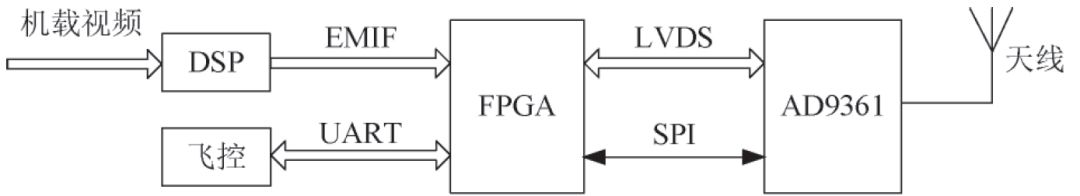

無人機(jī)機(jī)載數(shù)據(jù)鏈設(shè)備的系統(tǒng)架構(gòu)如圖1 所示。首先,F(xiàn)PGA 通過EMIF 接收DSP 的高清壓縮視頻、通過UART 接收飛控計(jì)算機(jī)的遙測(cè)數(shù)據(jù),壓縮后的視頻數(shù)據(jù)和遙測(cè)數(shù)據(jù)在FPGA 組幀編碼調(diào)制后通過LVDS 發(fā)送到AD9361,AD9361 對(duì)數(shù)據(jù)進(jìn)行上變頻后經(jīng)由天線發(fā)射出去; 同時(shí),AD9361 對(duì)天線接收到的信號(hào)進(jìn)行下變頻后,通過LVDS 將地面的遙控?cái)?shù)據(jù)發(fā)送到FPGA,數(shù)據(jù)在FPGA 中經(jīng)過解調(diào)譯碼解幀后通過UART 發(fā)送到飛控計(jì)算機(jī)中。其中,AD9361 的配置是FPGA 通過SPI 讀寫寄存器完成的。

圖1 無人機(jī)機(jī)載數(shù)據(jù)鏈設(shè)備的系統(tǒng)架構(gòu)圖

2 AD9361 配置流程

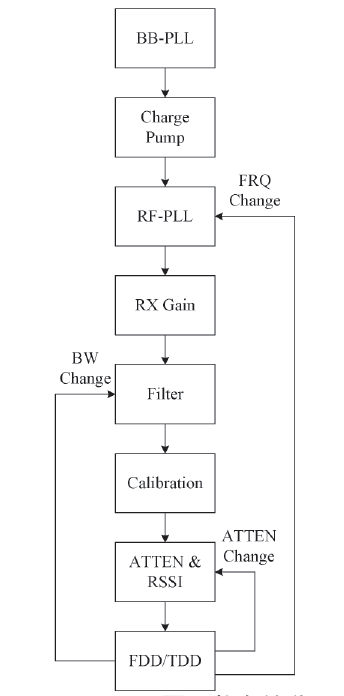

AD9361 有0 - 0x3FF 共1 024 個(gè)寄存器,有些寄存器不需要配置,保持上電默認(rèn)值即可,而有些寄存器需要進(jìn)行多次寫入,比如fir 濾波器、增益表等[7 - 8]。圖2 給出了AD9361 配置的狀態(tài)轉(zhuǎn)移圖。

圖2 AD9361 配置狀態(tài)轉(zhuǎn)移圖

BB - PLL: BB - PLL ( Base Band PLL,基帶鎖相環(huán)) 狀態(tài)是AD9361 初始化配置的起始狀態(tài),該狀態(tài)設(shè)置了晶振的輸入類型、參考時(shí)鐘頻率、AD9361內(nèi)部基帶鎖相環(huán)頻率和環(huán)路濾波器參數(shù)、單雙通道選擇等。SPI 讀0x5E 寄存器最高位為1 則說明基帶鎖相環(huán)成功鎖定。

Charge Pump: Charge Pump ( 電荷泵) 狀態(tài)是對(duì)AD9361 內(nèi)部電荷泵的電流進(jìn)行設(shè)置并校準(zhǔn),接收電荷泵設(shè)置0x23D 寄存器,發(fā)射電荷泵設(shè)置0x27D 寄存器。

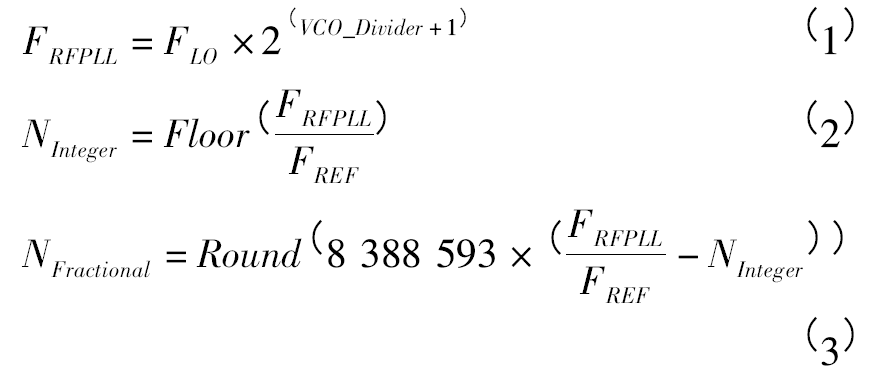

RF - PLL: RF - PLL ( Radio Frequency PLL,射頻鎖相環(huán)) 狀態(tài)對(duì)AD9361 的發(fā)射和接收頻率進(jìn)行設(shè)置,包括射頻鎖相環(huán)的頻率、壓控振蕩器參數(shù)、環(huán)路濾波器參數(shù)、混頻器增益表等。其中,壓控振蕩器和環(huán)路濾波器的參數(shù)分別寫入到FPGA 的rom ip 核中,通過查找表的方式進(jìn)行調(diào)用。射頻鎖相環(huán)的頻率范圍是6 ~ 12 GHz,發(fā)射和接收頻率范圍是從70~ 6 000 MHz,發(fā)射頻率和接收頻率是獨(dú)立的,即使精度設(shè)為1 MHz,如果將整個(gè)頻率范圍都存入rom ip核,至少需要存11 000 多組數(shù)據(jù),無論是工作量還是存儲(chǔ)空間都是巨大的,因此為了優(yōu)化設(shè)計(jì),發(fā)射頻率和接收頻率的設(shè)置通過式1 ~ 式3 來實(shí)現(xiàn)。

以發(fā)射頻率為例,式1:

FLO為AD9361 的發(fā)射頻率,

FRFPLL為發(fā)射鎖相環(huán)頻率,

VCO_Divider 是鎖相環(huán)分頻,根據(jù)表1 選擇相應(yīng)VCO_Divider 的值,例如

AD9361 的發(fā)射頻率FLO設(shè)置為4 635 MHz,則對(duì)應(yīng)的VCO_Divider 為0,然后根據(jù)式1 得到發(fā)射鎖相環(huán)的頻率FRFPLL為9 270 MHz。由于在BB - PLL 狀態(tài)中已經(jīng)將FREF參考時(shí)鐘設(shè)置為40MHz,那么通過式2就可以得到發(fā)射頻率的整數(shù)部分NInteger = 0xE7 并寫入到AD9361 的0x271 和0x272 寄存器中,通過公式3 得到發(fā)射頻率的小數(shù)部分NFractional = 0x5F_FFF5并寫入0x273 - 0x275 寄存器中。

設(shè)置接收頻率的公式和發(fā)射頻率相同,不同的是接收頻率的整數(shù)部分NInteger要寫入AD9361 的0x231 和0x232 寄存器,NFractional寫入0x233 - 0x235 寄存器。

表1 發(fā)射頻率FLO與鎖相環(huán)分頻VCO_Divider 的對(duì)應(yīng)關(guān)系

RX Gain: RX Gain( 接收增益) 狀態(tài)包括對(duì)LNA( 低噪聲放大器) 、TIA( 跨阻放大器) 、LPF( 低通濾波器) 、接收增益表、增益控制方式等進(jìn)行配置。接收增益表分為整體表和分立表,整體表配置簡(jiǎn)單,分立表配置復(fù)雜但是抗干擾能力更強(qiáng)。不同的頻率范圍又對(duì)應(yīng)著不同的增益表,接收頻率為70 ~ 1 550MHz、1 551 ~ 3 650 MHz、3 651 ~ 6 000 MHz 時(shí)需要設(shè)置不同增益表來調(diào)整輸入信號(hào)的增益。增益控制方式分為自動(dòng)增益控制( AGC) 和手動(dòng)增益控制( MGC) ,自動(dòng)增益控制又分為快速增益和慢速增益,通常情況下,時(shí)分雙工模式( TDD) 采用快速自動(dòng)增益,而頻分雙工模式( FDD) 采用慢速自動(dòng)增益。

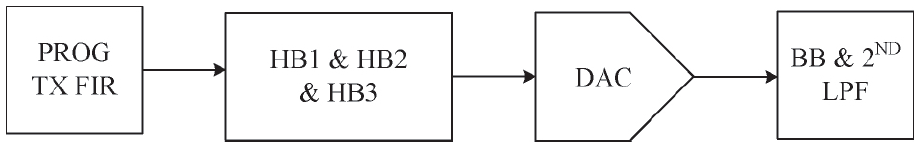

Filter: Filter( 濾波器) 狀態(tài)是對(duì)AD9361 內(nèi)部的數(shù)字和模擬濾波器進(jìn)行配置,發(fā)射和接收端各有4個(gè)數(shù)字濾波器和2 個(gè)模擬濾波器,圖3 給出了發(fā)射端濾波器的通路,經(jīng)過編碼后的IQ 兩路數(shù)據(jù)先后經(jīng)過FIR 濾波器和HB1、HB2、HB3 等3 個(gè)半帶濾波器插值后送入DAC 進(jìn)行數(shù)模轉(zhuǎn)換,接下來用一個(gè)3 階巴特沃斯低通濾波器BB LPF 和一個(gè)單極低通濾波器2ND LPF 來減小模擬信號(hào)的帶外雜散。

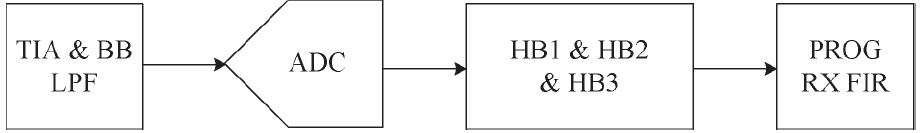

圖4 給出了接收端濾波器的通路,天線接到的模擬信號(hào)經(jīng)過一個(gè)單極低通濾波器TIA LPF 和一個(gè)3 階巴特沃斯低通濾波器BB LPF 后進(jìn)入到ADC 中進(jìn)行模數(shù)轉(zhuǎn)換,然后經(jīng)過HB1、HB2、HB3 等3 個(gè)半帶濾波器和FIR 濾波器輸出IQ 兩路數(shù)據(jù)到后面的數(shù)字信號(hào)處理模塊。

圖3 AD9361 發(fā)射信號(hào)濾波器通道

圖4 AD9361 接收信號(hào)濾波器通道

Calibration: Calibration( 校準(zhǔn)) 狀態(tài)包括基帶直流偏置校準(zhǔn)、射頻直流偏置校準(zhǔn)、發(fā)射正交校準(zhǔn)、接收正交校準(zhǔn)跟蹤、基帶和射頻直流跟蹤校準(zhǔn)。校準(zhǔn)的目的是通過對(duì)直流偏置、增益、相位誤差等進(jìn)行改善來提高系統(tǒng)的性能,各個(gè)校準(zhǔn)所需要的時(shí)間跟發(fā)射和接收頻率成反比,頻率越高,校準(zhǔn)時(shí)間越短。

ATTEN&RSSI: ATTEN( Attenuation,衰減控制)和RSSI( Receive Signal Strength Indicator,接收信號(hào)強(qiáng)度指示) 狀態(tài)包括發(fā)射信號(hào)的衰減值和接收信號(hào)強(qiáng)度的指示。衰減值可設(shè)置的范圍是0 ~ 89. 75dBm,精度是0. 25 dBm,RSSI 顯示與實(shí)際信號(hào)大小成反比,信號(hào)越強(qiáng),RSSI 值越小。

FDD/TDD: FDD( Frequency Division Duplex,頻分雙工) 或TDD( Time Division Duplex,時(shí)分雙工) 狀態(tài)通過配置0x13 - 0x15 寄存器切換AD9361 內(nèi)部的ENSM 狀態(tài)機(jī)來實(shí)現(xiàn)FDD 或者TDD,AD9361 正常工作時(shí)的一直保持該狀態(tài)。

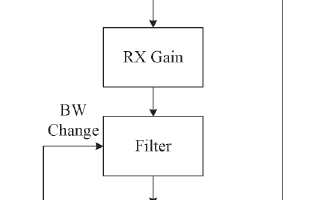

當(dāng)FPGA 接收到切換頻率( FRQ change) 指令時(shí),狀態(tài)機(jī)從FDD/TDD 狀態(tài)跳轉(zhuǎn)到RF - PLL 狀態(tài),改變發(fā)射或接收頻率后再跳轉(zhuǎn)到FDD/TDD 狀態(tài)正常工作; 當(dāng)FPGA 接收到切換帶寬( BW change) 指令時(shí),狀態(tài)機(jī)從FDD/TDD 狀態(tài)跳轉(zhuǎn)到Filter 狀態(tài),改變?yōu)V波器帶寬后再跳轉(zhuǎn)到FDD/TDD 狀態(tài)正常工作;當(dāng)FPGA 接收到切換衰減( ATTEN change) 指令時(shí),狀態(tài)機(jī)從FDD/TDD 狀態(tài)跳轉(zhuǎn)到ATTEN&RSSI 狀態(tài),改變衰減值后跳轉(zhuǎn)到FDD/TDD 狀態(tài)正常工作。

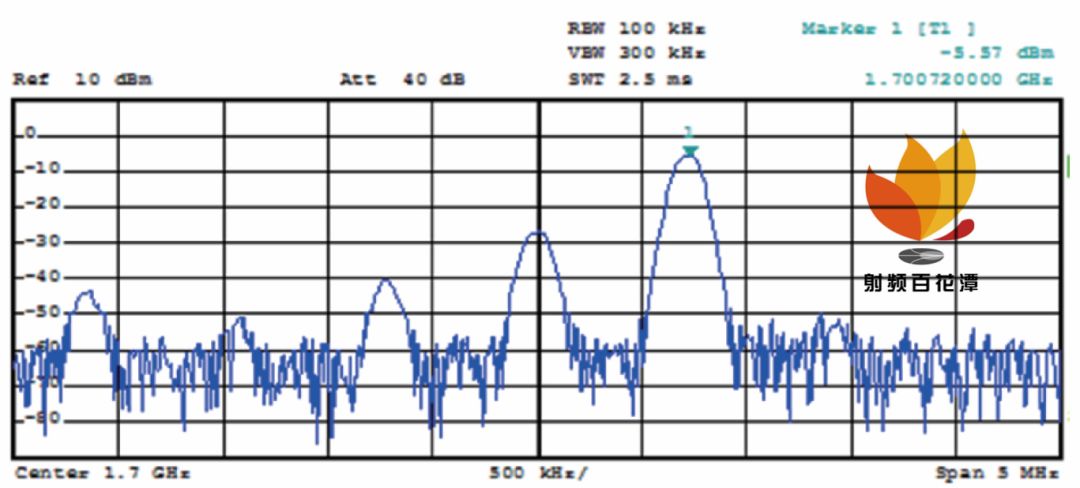

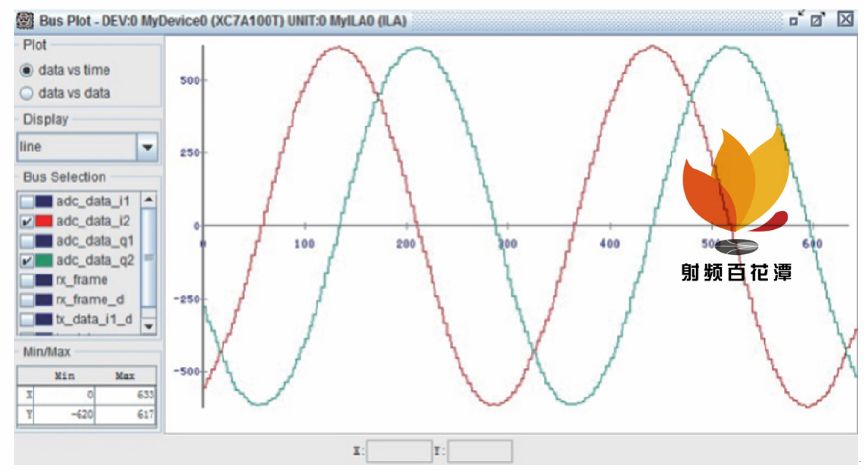

3 系統(tǒng)測(cè)試3. 1 單音測(cè)試基于Artix7 - 100T FPGA 配置AD9361 發(fā)射和接收頻率1. 7 GHz,發(fā)射和接收帶寬1 MHz,發(fā)射衰減10 dBm,雙工模式為FDD,單發(fā)單收。FPGA 內(nèi)部生成一個(gè)DDS ip 核,DDS 產(chǎn)生720KHz 的正弦波和余弦波作為AD9361 的I 路和Q 路發(fā)射數(shù)據(jù),圖5 給出了單音頻譜,可以看出頻譜從1. 7 GHz 向上搬移了720 KHz,輸出功率為- 5. 57dBm。圖6 是ChipScope采集到AD9361 實(shí)時(shí)接收的數(shù)據(jù),正確的還原出了發(fā)射的IQ 兩路信號(hào)。

圖5 AD9361 單音頻譜

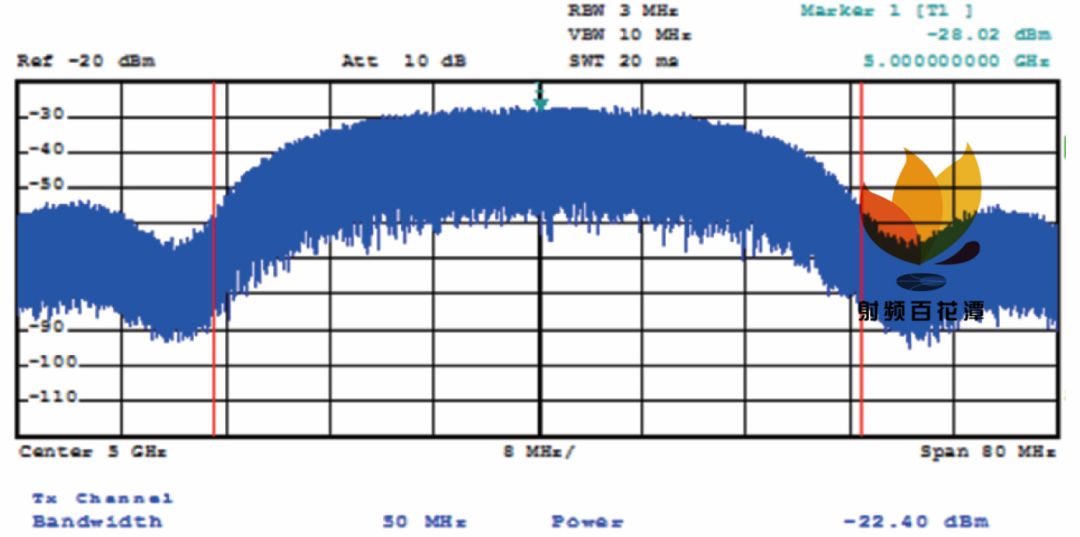

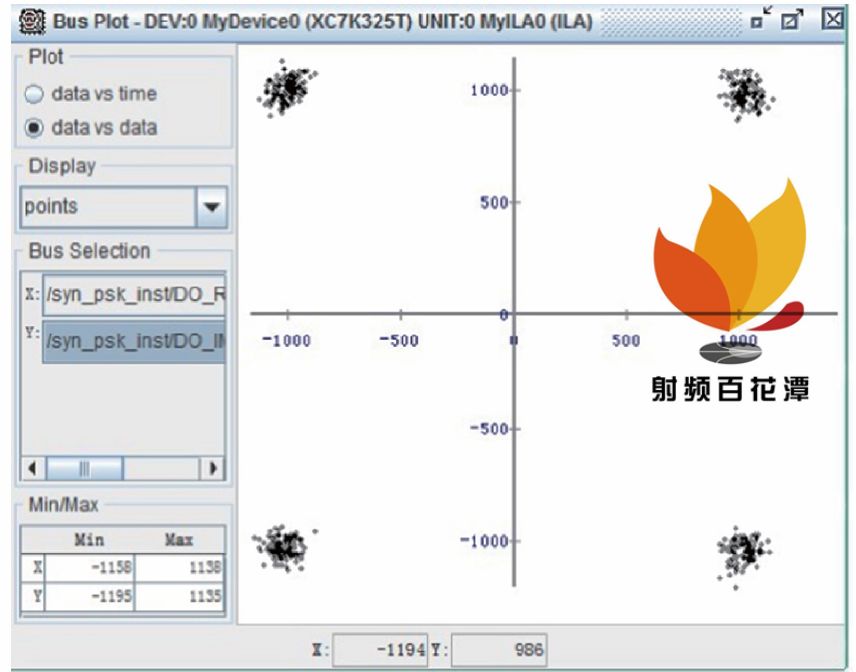

3. 2 寬帶測(cè)試基于Kintex7 - 325T FPGA 配置AD9361 發(fā)射和接收頻率5 GHz,發(fā)射和接收帶寬48MHz,發(fā)射衰減25 dBm,雙工模式為FDD,單發(fā)雙收。FPGA內(nèi)部產(chǎn)生一個(gè)32Mbps 業(yè)務(wù)速率的QPSK 信號(hào),符號(hào)速率55Mbps,經(jīng)過成型濾波后送入AD9361 的IQ 兩路,圖7給出了QPSK 調(diào)制信號(hào)的發(fā)射頻譜,中心頻率為5GHz,通道功率為- 22. 4 dBm。圖8 給出了AD9361接收到信號(hào)后經(jīng)過QPSK 解調(diào)的星座圖,能夠看出信號(hào)解調(diào)正常,可以進(jìn)行后續(xù)的譯碼解幀等工作。

圖6 ChipScope 采集AD9361 的IQ 兩路數(shù)據(jù)

圖7 QPSK 調(diào)制信號(hào)的發(fā)射頻譜

圖8 QPSK 解調(diào)后星座圖

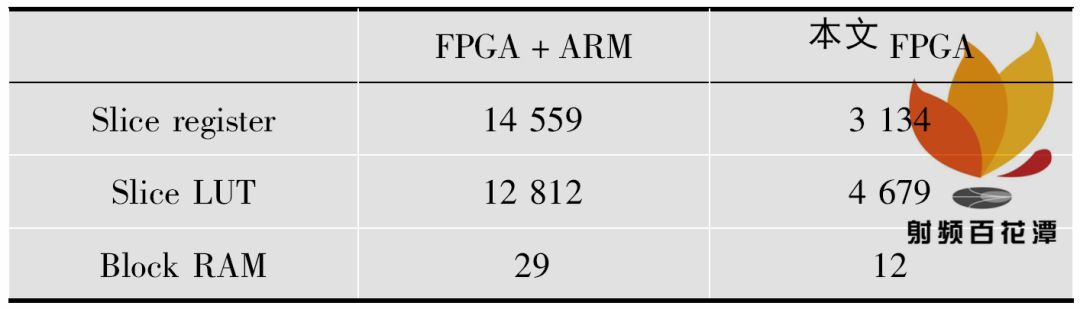

3. 3 資源占用分別用ADI 官方提供的FPGA + ARM 方式和本文FPGA 的方式配置AD9361,表2 給出了在Zedboard開發(fā)板上布線后的資源占用情況,通過對(duì)比可以看出,本文采用的FPGA 獨(dú)立配置AD9361 方式比FPGA + ARM 方式在資源上節(jié)省了60%以上。

表2 不同方式配置AD9361 占用FPGA 資源情況

結(jié)論

本文詳細(xì)的介紹了基于FPGA 獨(dú)立實(shí)現(xiàn)AD9361 射頻收發(fā)器的配置方法和步驟,該方法比ADI 官方提供的FPGA + ARM 或FPGA + MicroBlaze等解決方案更加通用,會(huì)大幅降低FPGA 的資源占用率。

本文分別在Xilinx 平臺(tái)Artix - 7、Kintex - 7、Zynq - 7000 等三種不同型號(hào)FPGA 上實(shí)現(xiàn)了AD9361 的配置,說明該方法方便移植于任意型號(hào)FPGA,甚至可以通過生成網(wǎng)表文件跨平臺(tái)使用。此外由于不需要DDR3 作為緩存,可以節(jié)約硬件電路板卡的面積、整體功耗和成本。本方案可實(shí)現(xiàn)機(jī)載數(shù)據(jù)鏈的小型化和低成本,滿足在軍品和民品領(lǐng)域無線視頻傳輸和遙控遙測(cè)的需求。(

-

FPGA

+關(guān)注

關(guān)注

1630文章

21759瀏覽量

604360 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3438瀏覽量

106076 -

無人機(jī)

+關(guān)注

關(guān)注

230文章

10470瀏覽量

181118 -

零中頻

+關(guān)注

關(guān)注

0文章

64瀏覽量

9144

原文標(biāo)題:基于FPGA配置AD9361在無人機(jī)數(shù)據(jù)鏈上的應(yīng)用

文章出處:【微信號(hào):gh_f97d2589983b,微信公眾號(hào):高速射頻百花潭】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AD9361和AD9371收發(fā)器,該如何選擇?

【應(yīng)用筆記】用Cyclone V FPGA配置AD9361

AD9361零中頻方案和低中頻方案,請(qǐng)問怎樣抑制鏡像頻率-1MHz的信號(hào)?

AD9361做零中頻接收機(jī),載波同步方面有什么建議?

請(qǐng)問AD9361能實(shí)現(xiàn)零中頻嗎?

基于AD9361設(shè)計(jì)QPSK調(diào)制解調(diào)收發(fā)器

射頻捷變收發(fā)器AD9361

AD9361射頻捷變收發(fā)器概述

AD9361射頻捷變收發(fā)器的功能特性及應(yīng)用分析

AD9361 RF捷變收發(fā)器的性能及應(yīng)用

如何通過FPGA+AD9361 SDR實(shí)現(xiàn)機(jī)載視頻無線傳輸

AD9361高性能高集成射頻敏捷收發(fā)器Linux設(shè)備驅(qū)動(dòng)程序

基于FPGA對(duì)零中頻射頻收發(fā)器AD9361進(jìn)行配置

基于FPGA對(duì)零中頻射頻收發(fā)器AD9361進(jìn)行配置

評(píng)論