碳化硅(SiC)MOSFET的優(yōu)異技術(shù)功能必須搭配適合的成本定位、系統(tǒng)相容性功能、近似于硅的FIT率以及量產(chǎn)能力,才足以成為主流產(chǎn)品。電力系統(tǒng)制造商需在實(shí)際商業(yè)條件下符合所有上述多項(xiàng)要素,以開創(chuàng)功率轉(zhuǎn)換的新局面,尤其是以能源效率以及「以更少投入獲得更多產(chǎn)出」為目標(biāo)的案例。

在未來,將有越來越多的功率電子應(yīng)用無法僅倚賴硅(Si)裝置滿足目標(biāo)需求。由于硅裝置的高動(dòng)態(tài)損耗,因此藉由硅裝置提高功率密度、減少電路板空間、降低元件數(shù)量及系統(tǒng)成本,同時(shí)提高功率轉(zhuǎn)換效能,即成為一個(gè)相互矛盾的挑戰(zhàn)。為解決此問題,工程師們逐漸開始采用以碳化硅材料為基礎(chǔ)的功率半導(dǎo)體來部署解決方案。

在這十多年來,諸如太陽能變頻器中的MPP追蹤或開關(guān)式電源供應(yīng)器中的功率因數(shù)校正等應(yīng)用中,使用Si IGBT加上SiC二極體或具有SiC二極體的超接面Si MOSFET已成為最先進(jìn)的解決方案,可實(shí)現(xiàn)高轉(zhuǎn)換效率及高可靠度的系統(tǒng)。市場(chǎng)報(bào)告甚至強(qiáng)調(diào)SiC二極體正進(jìn)入生產(chǎn)率的平原期。SiC技術(shù)中的量產(chǎn)技術(shù)、生產(chǎn)品質(zhì)監(jiān)控以及具有優(yōu)異FIT率的現(xiàn)場(chǎng)追蹤記錄,為采用包含SiC MOSFET之產(chǎn)品策略奠定了下一步基礎(chǔ)。

SiC MOSFET/Si IGBT效能大有優(yōu)勢(shì)

SiC半導(dǎo)體材料中的晶體管功能,為整體電力供應(yīng)鏈(從能源產(chǎn)生、傳輸及分配給消費(fèi)者)的能源效率(以較少能源獲得更多能源)提供了更大的潛力。

讓我們仔細(xì)研究一下SiC MOSFET與Si IGBT的效能優(yōu)勢(shì)。圖1顯示了先進(jìn)的硅解決方案范例:如果目標(biāo)為高效率與高功率密度,具有650V與1200V Si IGBT的3-Level T類拓?fù)涞囊粋€(gè)相位腳通常會(huì)用于三相系統(tǒng),例如光電變頻器與UPS。采用此種解決方案,效率最高可達(dá)到20~25kHz的切換頻率。由于裝置電容較低、部分負(fù)載導(dǎo)通損耗較低,以及沒有關(guān)斷尾電流,因此1200V SiC MOSFET的電流損耗比1200V Si IGBT低約80%。在外部切換位置使用1200V SiC MOSFET可大幅提升效率,并在指定的框架尺寸中達(dá)到更高的輸出功率。

圖1 先進(jìn)的硅解決方案范例

進(jìn)一步提高切換頻率會(huì)導(dǎo)致硅基解決方案效率與最大輸出功率迅速降低,但SiC MOSFET的低切換損耗不會(huì)有此問題。透過此范例的證明,工作頻率高達(dá)72kHz的三倍仍帶來比24kHz運(yùn)作之硅解決方案更高的效率。因此可縮減被動(dòng)元件實(shí)體尺寸、減少冷卻作業(yè),并達(dá)到更低的系統(tǒng)重量與成本。

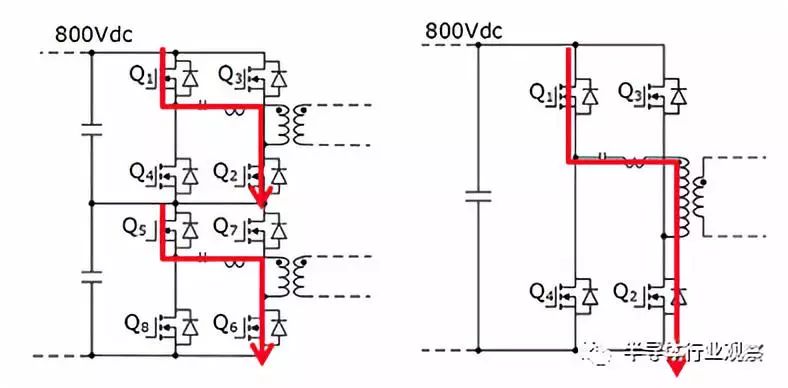

另一個(gè)三相電力轉(zhuǎn)換范例是電動(dòng)車的充電基礎(chǔ)設(shè)施。1200V SiC MOSFET可為DC-DC轉(zhuǎn)換級(jí)建構(gòu)一個(gè)LLC全橋級(jí),其中典型的硅解決方案倚賴650V Si超接面MOSFET,需要兩個(gè)串聯(lián)的LLC全橋來支援800V的DC鏈路。而四組SiC MOSFET加上驅(qū)動(dòng)器IC即可取代八組Si超接面MOSFET加上驅(qū)動(dòng)器IC,如圖2所示。除了零件數(shù)量減少及電路板空間縮減之外,還可以使效率達(dá)到最佳化。在每個(gè)導(dǎo)通狀態(tài)下,相較于Si解決方案中的四個(gè)切換位置,SiC MOSFET解決方案僅打開兩個(gè)切換位置。在快速電池充電中使用SiC MOSFET,可實(shí)現(xiàn)高效率的充電周期。

圖2 四組SiC MOSFET加上驅(qū)動(dòng)器IC即可取代八組Si超接面MOSFET加上驅(qū)動(dòng)器IC

由于動(dòng)態(tài)損耗比1200V Si級(jí)低一個(gè)量級(jí),因此SiC MOSFET亦可藉由提高效能,為傳統(tǒng)的簡(jiǎn)單拓?fù)涮峁┲匦率褂玫臋C(jī)會(huì)。在圖3中,將使用1200V SiC MOSFET的傳統(tǒng)2-Level解決方案與先前提及的先進(jìn)3-Level硅解決方案進(jìn)行比較。2-Level拓?fù)浣Y(jié)構(gòu)的優(yōu)點(diǎn)是控制方案非常簡(jiǎn)單,且減少50%的零件數(shù)量。此種解決方案可用于光電與UPS變頻器,以及驅(qū)動(dòng)系統(tǒng)、電池充電及能源儲(chǔ)存解決方案中具有雙向性的主動(dòng)式前端。如圖3所示,盡管切換頻率從24kHz提高至48kHz,但在2-Level SiC MOSFET解決方案的高負(fù)載條件下,效率提高了0.3~0.4%,這的確令人驚奇,因?yàn)槠淝袚Q電壓較3 -Level運(yùn)作高出兩倍(800V比400V)。

圖3 使用1200V SiC MOSFET的傳統(tǒng)2-Level解決方案與先進(jìn)3-Level硅解決方案比較

然而,以SiC MOSFET進(jìn)行設(shè)計(jì)也存在著挑戰(zhàn)。設(shè)計(jì)人員必須考量SiC MOSFET的切換瞬變。相較于經(jīng)常可在1200V Si IGBT中見到的5~20V/ns,50V/ns或更高的dv/dt并不罕見。因此,電路板層級(jí)上的寄生耦合電容將導(dǎo)致過多的能源損耗。對(duì)于以更簡(jiǎn)單的2-Level解決方案取代3-Level Si IGBT解決方案的情況而言,如果切換電壓與頻率皆加倍,則寄生耦合電容將產(chǎn)生高出八倍的能源損耗。圖3顯示當(dāng)SiC MOSFET在標(biāo)準(zhǔn)IGBT 2-Level解決方案中隨插即用時(shí)的原始效率線,而下一個(gè)效率線則顯示有關(guān)汲極-源極寄生電路板電容的PCB謹(jǐn)慎設(shè)計(jì)能如何減少損耗。當(dāng)切換頻率增加時(shí),應(yīng)考量的第二個(gè)主題涉及電感器的磁芯損耗。

由于漣波電流及其相應(yīng)的損耗在整個(gè)負(fù)載范圍內(nèi)維持恒定,藉由改變芯材料來改善磁芯損耗主要會(huì)影響部分負(fù)載效率。相較于3-Level Si IGBT解決方案,這兩項(xiàng)改善最終將帶來高于98.5%的理想效率線。這顯示SiC MOSFET主要并非Si IGBT的隨插即用選項(xiàng),而且需要大量的設(shè)計(jì)作業(yè)才能將效能提升到更高水準(zhǔn)。

硅主流技術(shù)影響SiC可靠性/穩(wěn)固性

目前為止,SiC MOSFET需要比Si IGBT或Si MOSFET更高的閘極驅(qū)動(dòng)電壓,而且經(jīng)常面臨極為接近零伏特的低閘極-源極臨界值電壓裕度。此微小的裕度使得閘極電壓振鈴尖峰處于高dv/dt旋轉(zhuǎn)率,成為系統(tǒng)設(shè)計(jì)人員關(guān)注的問題。新型溝槽技術(shù)實(shí)現(xiàn)了標(biāo)準(zhǔn)化閘極驅(qū)動(dòng)方案,使+15V的Si IGBT足以導(dǎo)通,而4V基準(zhǔn)臨界值電壓可在電流關(guān)斷時(shí)提供穩(wěn)固的訊噪比。

SiC MOSFET還需要匹配的驅(qū)動(dòng)器IC才能釋放其所有潛力。這些驅(qū)動(dòng)器必須處理高達(dá)50V/ns或更高的dv/dt以及高切換頻率,對(duì)時(shí)序與公差帶來了更嚴(yán)格的要求。SiC MOSFET也可能需要負(fù)閘極電壓,特別是用于硬切換拓?fù)浠蛎桌浙Q制時(shí)。因此,如英飛凌的EiceDRIVER IC便適合驅(qū)動(dòng)SiC MOSFET,且可根據(jù)應(yīng)用需求提供各種功能,包含緊密的傳播延遲匹配、精確的輸入濾波器、寬輸出側(cè)供電范圍、負(fù)閘極電壓功能或米勒鉗制,以及擴(kuò)展的CMTI功能。

SiC的可靠性與穩(wěn)固性保證與硅主流技術(shù)密切相關(guān)。SiC是大功率的半導(dǎo)體,但是以此種材料設(shè)計(jì)MOSFET涉及各種技術(shù)挑戰(zhàn),包括調(diào)整效能參數(shù)以達(dá)到可靠性與穩(wěn)固性。

設(shè)計(jì)平面SiC MOSFET時(shí),必須在區(qū)域特定導(dǎo)通電阻與閘極氧化物可靠性之間取得主要的平衡,亦即「芯片成本與效能以及可靠性之間的權(quán)衡」。

平面SiC-SiO2介面上的缺陷密度在4H-SiC中非常高,這導(dǎo)致MOSFET通道中的電子散射,并因此降低電子通道移動(dòng)率。效能降低會(huì)導(dǎo)致通道電阻增加,以及導(dǎo)通狀態(tài)下功率損耗增加。只有透過在氧化物上施加過大的電場(chǎng)加以導(dǎo)通,或透過更高的閘極-源極電壓或更薄的SiO2層,區(qū)域特定的導(dǎo)通電阻才能夠保持在優(yōu)良的低水準(zhǔn)程度。

對(duì)于SiC材料中的溝槽MOSFET裝置結(jié)構(gòu)而言,由于垂直晶格平面中的SiO2介面具有遠(yuǎn)低于平面介面的缺陷密度,因此毋須過度驅(qū)動(dòng)氧化物。然而,由于SiC材料中的高電場(chǎng),溝槽結(jié)構(gòu)對(duì)于溝槽轉(zhuǎn)角處的阻隔模式而言是更大的挑戰(zhàn)。實(shí)現(xiàn)適當(dāng)場(chǎng)衰減的設(shè)計(jì)措施比平面結(jié)構(gòu)更為復(fù)雜。

采用比例提升SiC成本不再高不可攀

在廣泛采用SiC MOSFET之前,客戶需確保合作的供應(yīng)商能夠穩(wěn)定提供優(yōu)質(zhì)產(chǎn)品,且在需求增加時(shí)仍能維持水準(zhǔn)。電源芯片商為此所建立的生產(chǎn)流程具有高容量及高靈活性,經(jīng)驗(yàn)證可制造Si與SiC芯片,并組裝成獨(dú)立封裝或電源模組。多項(xiàng)先進(jìn)的功率裝置技術(shù)先前皆已成功獲得提升,例如CoolMOS、TRENCHSTOP IGBT及CoolSiC蕭特基二極體;也致力于透過市場(chǎng)推廣與增加產(chǎn)量推動(dòng)CoolSiC MOSFET產(chǎn)品發(fā)展。

過去以來,SiC裝置價(jià)格較硅裝置高,是阻礙市場(chǎng)廣泛采用SiC裝置的因素之一。由于SiC與硅裝置在原始晶圓制程中存有根本上的差異,因此SiC裝置仍較為昂貴,而且在可預(yù)見的未來不會(huì)達(dá)到同等的成本。多年來由于采用比例提升、規(guī)模經(jīng)濟(jì)、新的區(qū)域有效芯片設(shè)計(jì),以及生產(chǎn)更大的晶圓直徑,SiC二極體價(jià)格已經(jīng)下降。目前市場(chǎng)上SiC裝置價(jià)格的下降及供貨的增加,使得電源設(shè)計(jì)廠商面臨提高電源轉(zhuǎn)換效能并降低系統(tǒng)成本的壓力,其需求也因此有所變更。

-

MOSFET

+關(guān)注

關(guān)注

148文章

7704瀏覽量

216212 -

功率器件

+關(guān)注

關(guān)注

42文章

1843瀏覽量

91337 -

SiC

+關(guān)注

關(guān)注

30文章

3036瀏覽量

63736

原文標(biāo)題:SiC MOSFET進(jìn)入主流市場(chǎng),功率器件新局面正式開啟

文章出處:【微信號(hào):iawbs2016,微信公眾號(hào):寬禁帶半導(dǎo)體技術(shù)創(chuàng)新聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

評(píng)論