本篇主要介紹PCIe總線(xiàn)的復(fù)位方式。

PCIe總線(xiàn)規(guī)定了兩個(gè)復(fù)位方式:Conventional Reset和FLR(Function Level Reset),而Conventional Reset又可以進(jìn)一步分為兩大類(lèi):Fundamental Reset和Non-Fundamental Reset。Fundamental Reset方式包括Cold和Warm Reset方式,可以將PCIe將設(shè)備中的絕大多數(shù)內(nèi)部寄存器和內(nèi)部狀態(tài)都恢復(fù)成初始值;而Non-FundamentalReset方式為Hot Reset方式。

1、傳統(tǒng)復(fù)位方式(Conventional)

傳統(tǒng)的復(fù)位方式分為Cold、Warm和Hot Reset。PCIe設(shè)備可以根據(jù)當(dāng)前的設(shè)備的運(yùn)行狀態(tài)選擇合適的復(fù)位方式,PCIe總線(xiàn)提供多種復(fù)位方式的主要原因是減小PCIe設(shè)備的復(fù)位延時(shí)。其中傳統(tǒng)復(fù)位方式的延時(shí)大于FLR方式。使用傳統(tǒng)復(fù)位方式時(shí),Cold Reset使用的時(shí)間最長(zhǎng),而Hot Reset使用的時(shí)間最短。

1.1、Cold Reset

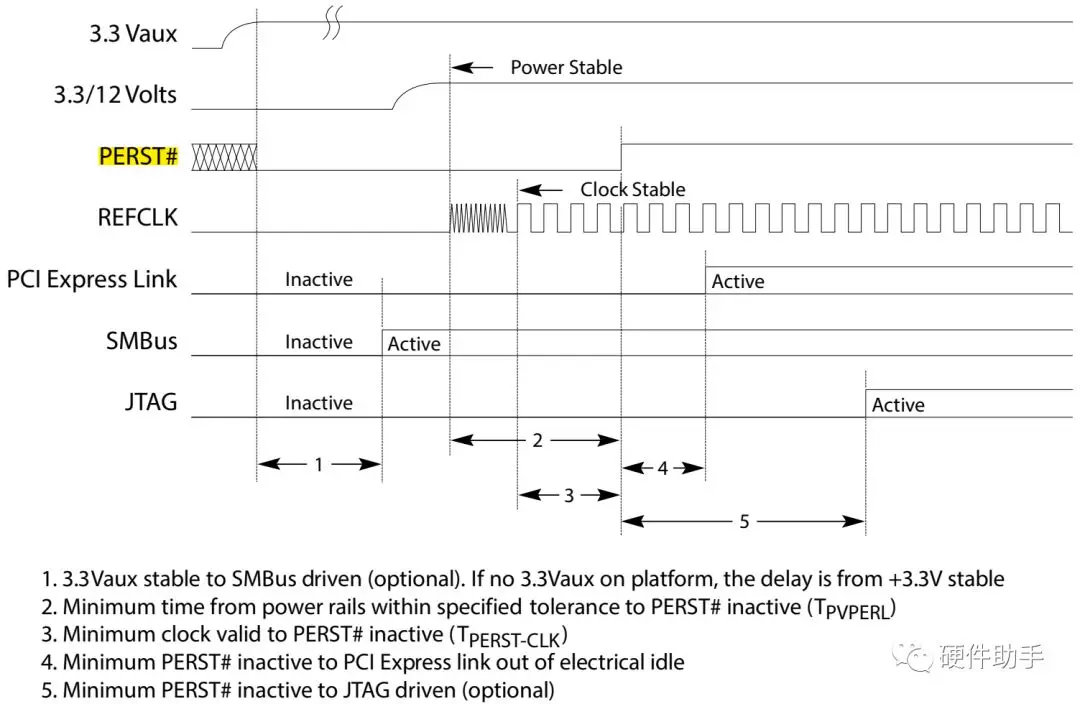

當(dāng)一個(gè)PCIe設(shè)備的Vcc電源上電后,處理器系統(tǒng)將置該設(shè)備的PERST#信號(hào)為有效,此時(shí)將引發(fā)PCIe設(shè)備的復(fù)位方式,這種方式屬于Fundamental Reset。PCIe設(shè)備進(jìn)行Clod Reset時(shí),所有使用Vcc進(jìn)行供電的寄存器和PCIe端口邏輯將無(wú)條件進(jìn)入初始狀態(tài)。但是使用這種方式依然無(wú)法復(fù)位使用Vaux(備用電源)供電的寄存器和邏輯,這些寄存器和邏輯只能在處理器完全掉電時(shí)徹底復(fù)位。

1.2、Warm Reset

在PCIe的設(shè)備完成上電后,也可能重新進(jìn)行Fundamental Reset,這種復(fù)位方式也被稱(chēng)為Warm Reset。PCIe并沒(méi)有定義Warm Reset的具體實(shí)現(xiàn)方式。

1.3、Hot Reset

當(dāng)PCIe設(shè)備出現(xiàn)某種異常時(shí),可以使用軟件手段對(duì)該設(shè)備進(jìn)行復(fù)位。如系統(tǒng)軟件將Bridge Control Register 的Secondary Bus Reset位置為1,該橋片將secondary總線(xiàn)上的PCIe設(shè)備進(jìn)行Hot Reset。PCIe總線(xiàn)將通過(guò)TS1和TS2序列對(duì)下游設(shè)備進(jìn)行Hot Reset。

在TS1和TS2序列中包含一個(gè)Hot Reset位。當(dāng)下游設(shè)備收到一個(gè)TS1和TS2序列,而且Hot Reset位為1時(shí),下游設(shè)備將使用Hot Reset方式進(jìn)行復(fù)位操作。

Hot Reset方式并不屬于Fundamental Reset。PCIe設(shè)備進(jìn)行Hot Reset方式時(shí),也可以將PCIe設(shè)備的多數(shù)寄存器和狀態(tài)恢復(fù)為初始值。

同時(shí),在PCIe總線(xiàn)中,如果需要對(duì)鏈路的Link Width進(jìn)行改變時(shí),也將會(huì)用到Hot Reset。具體的流程如下:

Ensure the Link is in the L0LTSSM state.

Program the 6-bit “Link ModeEnable” field of the “Port LinkControl Register” on page 732. This isused bythe LTSSM in DETECT.

Programthe 9-bit “PredeterminedNumber of Lanes” field of the “Gen2 Control Register” on page 771. Thisindicatesto the LTSSM, the number of lanes to check for exiting from L2.IDLE orPOLLING.ACTIVE.

Trigger a Hot Reset, by settingthe Secondary Bus Reset bit in the RC Bridge ControlRegister (of the Type 1 PCIConfiguration Space Header) to 1.

Wait for 2 mS. The core’s LTSSMwill transition from L0 -》 RCVRY -》 HOTRESET.

Clear theSecondary Bus Resetbit. The core’s LTSSM will transition from HOTRESET -》 DETECT.

2、FLR(Function Level Reset)

除了傳統(tǒng)的復(fù)位方式之外,PCIe總線(xiàn)還提供了FLR方式。系統(tǒng)軟件通過(guò)填寫(xiě)某些寄存器,如synosys的PCIe的IP是可以通過(guò)配置PCI ExpressCapability的DeviceControl Register的第16bit完成FLR。支持FLR方式的PCIe設(shè)備需要在其BAR空間中提供一個(gè)寄存器,當(dāng)系統(tǒng)軟件對(duì)該寄存器的Function LevelReset位寫(xiě)1時(shí),PCIe設(shè)備將使用FLR方式復(fù)位PCIe設(shè)備的內(nèi)部邏輯。FLR方式對(duì)PCIe設(shè)備是可選的。

在一個(gè)大規(guī)模的并行處理系統(tǒng)中,系統(tǒng)軟件使用分區(qū)的概念管理所有硬件資源,包括處理器資源和所有IO資源,這些IO資源中通常會(huì)包含PCIe設(shè)備。在這種處理器系統(tǒng)中,任務(wù)在指定的分區(qū)中運(yùn)行,當(dāng)這個(gè)任務(wù)執(zhí)行完畢后,系統(tǒng)軟件需要調(diào)整硬件資源的分區(qū)。此時(shí)受到影響的PCIe設(shè)備需要使用FLR方式復(fù)位內(nèi)部的邏輯,以免造成對(duì)新的分區(qū)的資源污染,并保護(hù)之前任務(wù)的結(jié)果。

當(dāng)PCIe設(shè)備使用FLR方式進(jìn)行復(fù)位時(shí),有些與PCIe鏈路相關(guān)的狀態(tài)和寄存器并不會(huì)被復(fù)位:

Sticky Registers。與傳統(tǒng)的復(fù)位方式相同,F(xiàn)LR方式不能復(fù)位這些寄存器,但是系統(tǒng)軟件對(duì)部分Sticky Registers進(jìn)行修改。當(dāng)Vaux(備用電源)被移除后,這些寄存器中的保存的數(shù)據(jù)才會(huì)丟失。

HwInit類(lèi)型的寄存器。在PCIe設(shè)備中,有效配置寄存器的屬性為HwIint,這些寄存器的值由芯片的配置引腳決定,后者上電復(fù)位后從EEPROM中獲取。Cold和Warm Reset可以復(fù)位這些寄存器,然后從EEPROM中從新獲取數(shù)據(jù),但是使用FLR方式不能復(fù)位這些寄存器。

此外,還有一些特殊的配置寄存器不能被FLR方式復(fù)位,如Max_Payload_Size、RCB和一些與電源管理、流量控制和鏈路控制直接相關(guān)的寄存器。

FLR方式不會(huì)影響LTSSM狀態(tài)機(jī)。

-

總線(xiàn)

+關(guān)注

關(guān)注

10文章

2890瀏覽量

88159 -

PCIe

+關(guān)注

關(guān)注

15文章

1241瀏覽量

82747 -

復(fù)位

+關(guān)注

關(guān)注

0文章

172瀏覽量

24224

原文標(biāo)題:PLC控制電路設(shè)計(jì)中常用的電氣符號(hào)和文字符號(hào)

文章出處:【微信號(hào):gongkongworld,微信公眾號(hào):工控資料窩】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

請(qǐng)問(wèn)在PCB設(shè)計(jì)過(guò)程中兩種電源分配方式的具體含義是什么?

PCIe總線(xiàn)的復(fù)位方式是什么?

SQL語(yǔ)言的兩種使用方式

簡(jiǎn)單談?wù)?b class='flag-5'>兩種復(fù)位電路的工作原理

逆變器的兩種電流型控制方式

PCIe兩種中斷傳遞方式

單片機(jī)實(shí)現(xiàn)利用中斷復(fù)位的兩種方式

兩種總線(xiàn)數(shù)據(jù)兩種傳遞形式:PIO、DMA介紹資料下載

MSP430單片機(jī)的兩種SPI總線(xiàn)實(shí)現(xiàn)方式

PCIe總線(xiàn)的兩種復(fù)位方式

PCIe總線(xiàn)的兩種復(fù)位方式

評(píng)論