聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

131334 -

design

+關(guān)注

關(guān)注

0文章

158瀏覽量

45743 -

Vivado

+關(guān)注

關(guān)注

19文章

813瀏覽量

66657

發(fā)布評論請先 登錄

相關(guān)推薦

ZYNQ基礎(chǔ)---AXI DMA使用

Xilinx官方也提供有一些DMA的IP,通過調(diào)用API函數(shù)能夠更加靈活地使用DMA。 1. AXI DMA的基本接口 axi dma IP

Vivado之實現(xiàn)布局布線流程介紹

一、前言 本文將介紹Vivado進行綜合,以及布局布線的內(nèi)部流程,熟悉該流程后結(jié)合Settings中對應(yīng)的配置選項,對于時序收斂調(diào)試將更具有針對性。 二、Implementation(實現(xiàn)) 實現(xiàn)

AMD Vivado Design Suite 2024.2全新推出

AMD Vivado Design Suite 2024.2 全新推出,使用 AMD Versal Adaptive SoC 進行設(shè)計的重大改進。此版本為 AMD Versal 自適應(yīng) SoC

U50的AMD Vivado Design Tool flow設(shè)置

AMD Alveo 加速卡使用有兩種流程,AMD Vitis Software Platform flow 和 AMD Vivado Design Tool flow。比較常見的是 Vitis

vivado導(dǎo)入舊版本的項目,IP核心被鎖。

vivado導(dǎo)入其他版本的項目的時候,IP核被鎖,無法解開,請問該如何解決。

使用軟件:vivado 2019.2

導(dǎo)入項目使用版本:vivado 2018

發(fā)表于 11-08 21:29

使用Vivado通過AXI Quad SPI實現(xiàn)XIP功能

本博客提供了基于2023.2 Vivado的參考工程,展示如何使用Microblaze 地執(zhí)行(XIP)程序,并提供一個簡單的bootloader。

AMD Vivado Design Suite 2024.1全新推出

AMD Vivado Design Suite 2024.1 可立即下載。最新版本支持全新 AMD MicroBlaze V 軟核處理器,并針對 QoR 和 Dynamic Function

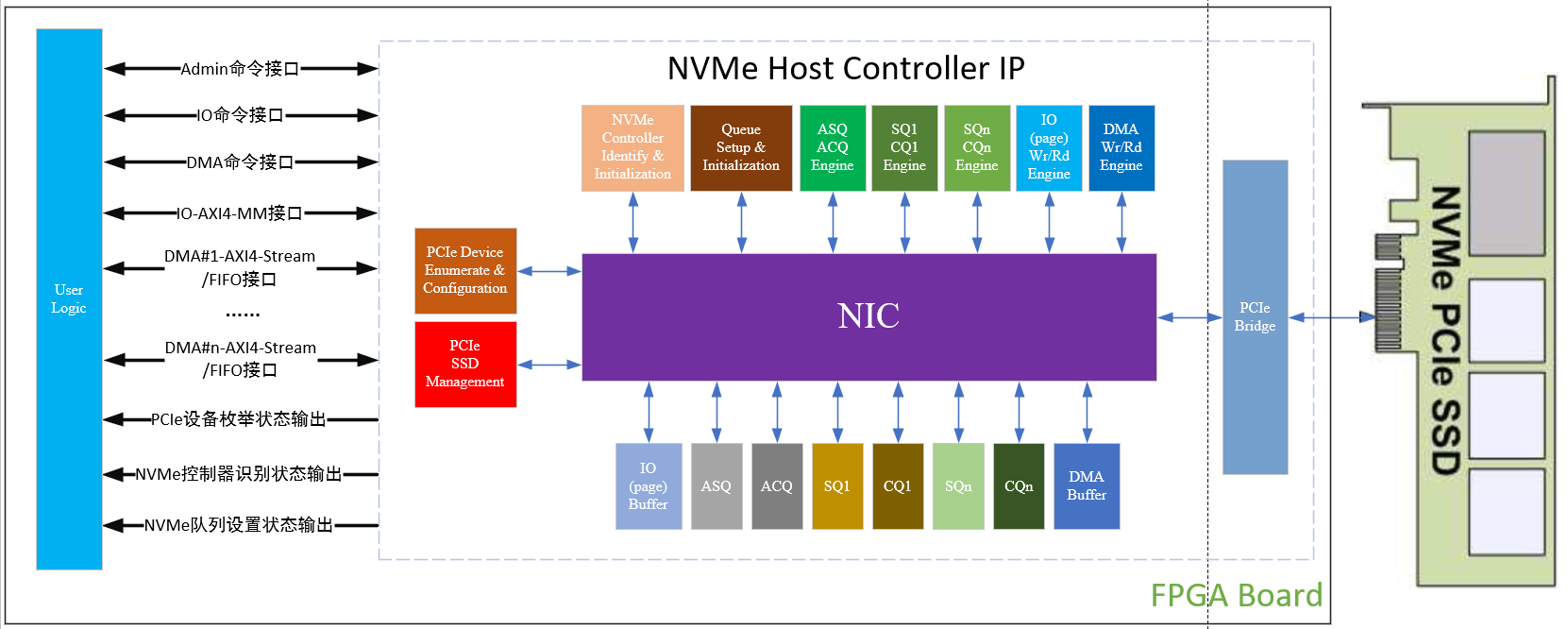

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

NVMe AXI4 Host Controller IP可以連接高速存儲PCIe SSD,無需CPU,自動加速處理所有的NVMe協(xié)議命令,具備獨立的數(shù)據(jù)寫入和讀取AXI4接口,不但適用

淺談Pango_Design_Suite工具的安裝

要不要安裝并口驅(qū)動,為了兼容性更好,筆者這里選擇安裝,而后即完成并口的外設(shè)接口的驅(qū)動安裝。

至此,Pango_Design_Suite工具安裝全部完成,然后我們可以直接打開Pango Design

發(fā)表于 05-30 00:43

SoC設(shè)計中總線協(xié)議AXI4與AXI3的主要區(qū)別詳解

AXI4和AXI3是高級擴展接口(Advanced eXtensible Interface)的兩個不同版本,它們都是用于SoC(System on Chip)設(shè)計中的總線協(xié)議,用于處理器和其它外設(shè)之間的高速數(shù)據(jù)傳輸。

FPGA通過AXI總線讀寫DDR3實現(xiàn)方式

AXI總線由一些核心組成,包括AXI主處理器接口(AXI4)、AXI處理器到協(xié)處理器接口(

發(fā)表于 04-18 11:41

?1295次閱讀

PCIe-AXI-Cont用戶手冊

Transaction layer的所有功能特性,不僅內(nèi)置DMA控制器,而且具備AXI4用戶接口,提供一個高性能,易于使用,可定制化的PCIe-AXI互連解決方案,同時適用于ASIC和FPGA。

發(fā)表于 02-22 09:15

?3次下載

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

NVMe Host Controller IP可以連接高速存儲PCIe SSD,無需CPU和外部存儲器,自動加速處理所有的NVMe協(xié)議命令,具備獨立的數(shù)據(jù)寫入AXI4-Stream/FIFO接口和數(shù)

如何使用Vivado Design Suite IP Integrator的調(diào)試AXI接口

如何使用Vivado Design Suite IP Integrator的調(diào)試AXI接口

評論