隨著數字電視技術的進一步成熟,在視頻服務器方面,利用支持軟件豐富、運算速度不斷提高、具有較高性能價格比的微機來代替昂貴的專用設備實現數字視頻碼流的復用具有一定的實際意義,但是一般的桌面操作系統定時不夠精確、處理大量并發任務效率不高以及突發傳送等問題影響了復用后碼流的質量,為了保證復用后的碼流可以均勻平滑地傳送到調制器,還考慮到微機的工作效率,就需要用FIFO來進行碼流的緩沖。如果FIFO的容量足夠大,微機就可以通過DMA方式一次發送大量的數據,最后再經過FIFO的緩沖,按照預設頻率均勻送出。

在其它許多實際應用中,也會利用到FIFO來完成數據流的緩沖,消除突發傳送帶來的數據抖動,達到平滑輸出的效果。FIFO的容量和速度直接影響到緩沖的效果,但是目前大容量FIFO價格昂貴,這就影響到了FIFO的進一步實際應用。本文介紹了一種利用外部SRAM和CPLD構成的廉價、高速、大容量先進先出緩沖器FIFO的設計方法。

一、系統的設計思路

為了用外部SRAM來實現FIFO,要解決以下問題:

區分同時到達的讀寫信號,并且產生間隔的對外部SRAM的讀寫信號

在SRAM順序尋址的基礎上實現數據的先進先出

全空、全滿、半空、半滿狀態的判定

盡量降低對器件速度的要求

二、設計方法

同步設計

在系統中地址產生、比較器結果輸出、FIFO各種狀態的輸出都采用同步觸發方式,全部按照系統時鐘統一進行,這能在很大程度上消除異步方式引起的邏輯狀態變化時間的不確定和毛刺的產生,但也沒必要在所有的地方都強求按同步設計,只要能符合時序要求,異步方式也可以,目的是盡量減少設計的復雜度和占用的資源。

原理圖輸入

設計在Altera公司的MAX+plus II V9.6軟件下編譯仿真。在系統的整體設計中采用原理圖的方式,可以方便地進行時序控制和仿真。

三、具體信號的產生及時序分析

信號分析的具體條件

以下的設計都是在CPLD為EPM7128SQC100-6,SRAM為IDT71128-12的條件下進行,對FIFO的最高要求為雙向同時讀寫,時鐘RCLK和WCLK為10MHz,脈沖寬度為50ns,系統時鐘CLK為50MHz,脈沖寬度為10ns。對于較低速度的讀寫,50MHz的系統時鐘也可以適應,如果外部要求降低,也可按照與RCLK、WCLK的等比例換用較低的系統時鐘。外部數據是在上升沿有效,FIFO的輸出也是上升沿有效。

基本信號的產生以及時序圖

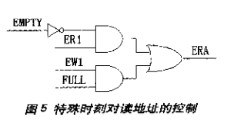

系統采用獨立的系統時鐘CLK。為區分同時到達的外部讀寫信號,內部產生的讀寫信號分別用系統時鐘的上升沿和下降沿觸發,同時讓產生的內部讀寫信號互斥,以得到間隔的對外部SRAM的讀寫信號;考慮到實際的需要以及器件和內部時鐘的速度,按照四個脈沖寬度的方式產生讀寫信號,以保證在最小10個脈沖時間內各有一次有效讀寫。

外部讀寫時鐘RCLK、WCLK先經過各自的使能控制信號REN、WEN進入CPLD;為保證讀寫互斥,外部讀寫異步鎖存之后,讀信號鎖存后面的第一個上升沿,寫信號鎖存后面的第一個下降沿,并且用各自的前三個脈沖控制對方鎖存第一個脈沖。

通過對各種情況的分析,基本讀寫脈沖OE和MW之間的最小間隔是一個脈沖,在有連續兩個外部讀或寫的情況下所產生的兩個OE或MW之間的最小間隔是兩個脈沖。

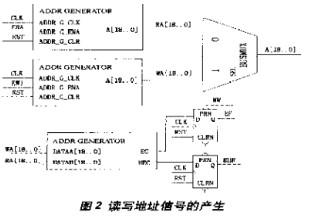

讀寫地址信號

讀寫各有一個地址指針,每讀出一個數讀地址加一,讀指針就指向下一個最早寫入的數,經過SRAM陣列的最高地址后,又從起始地址開始,這樣就可以達到先進先出的效果;只有有效的讀寫脈沖才能觸發地址計數器;為使整個系統的動作時間一致,采用同步設計,讀寫都統一選擇上升沿觸發計數器變化;地址改變先于后面的/WE、/OE脈沖的產生。

地址發生器采用計數器宏單元。FIFO容量的大小由計數器決定,簡單地增加計數器的位數和SRAM的數量,就可以擴大FIFO的容量。讀寫地址產生之后,經過一個總線復用器后輸出作為對外部SRAM讀寫的地址線;總線復用器的選擇由MW信號控制,只有在MW有效的時候才輸出為寫地址,其它時間都是讀地址。

讀寫地址在由計數器產生經過總線復用時,會產生靜態冒險;對于讀寫地址比較器,因為它鎖存的時刻距離地址變化后兩個脈沖,而且比較器輸入的地址不經過總線復用,這就可以保證在比較器鎖存的時刻地址比較結果已經穩定而且不受靜態冒險的影響;對于到SRAM的讀寫地址,在讀寫控制脈沖/OE、/WE有效前還有兩個脈沖的時間穩定,不會因為地址不穩定產生錯誤操作。

讀寫地址相等時比較器輸出相等標志EF,FIFO半滿,即除去最高位以外的地址都相等的情況輸出半滿標志EHF。

FIFO狀態信號

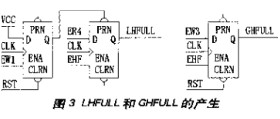

1、小于半滿LHFULL

在上電或復位之后,LHFULL立刻有效。利用另一個觸發器上電或者復位的清零,置位LHFULL觸發器,使其有效,但在第一個寫之后這個觸發器就不再對LHFULL的變化有影響。在讀寫地址比較器輸出半滿的時候再來一個讀,就判定為小于半滿LHFULL。從大于半滿到小于半滿,需要經過兩個連續的讀,第一個讀使比較器得到半滿結果,第二個讀使LHFULL有效。當經過一個寫從小于半滿到半滿時,在讀寫地址比較器輸出半滿使LHFULL觸發器狀態可以變化后的下一個上升沿清除LHFULL觸發器。觸發器的使能端選為EHF,保證狀態信號只在半滿的時候才發生變化。

2、大于半滿GHFULL

半滿的時候再來一個寫,GHFULL置位為高有效。GHFULL的設計原理同LHFULL,且不需要上電復位置位的處理。

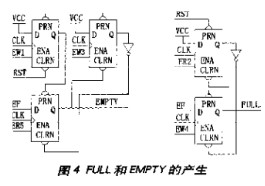

3、全滿FULL

當比較器輸出結果為讀寫地址相等時,如果此時執行的操作是寫,即在一個寫之后讀寫地址才相等,就判定為全滿,置FULL為有效。在全滿狀態下,如果有一個讀,FULL就被清零。

1、 全空EMPTY

在上電或復位之后,EMPTY立刻有效。利用另一個觸發器上電或者復位的清零,置位EMPTY觸發器,使其有效,但在第一個寫之后這個觸發器就不再對EMPTY的變化有影響。當比較器輸出結果為讀寫地址相等時,如果此時執行的操作是讀,即在一個讀之后讀寫地址相等,就判定為全空,置EMPTY有效。全空狀態下,如果有一個寫,EMPTY就被清零。

復位信號

只要RST信號為低就會產生有效的復位,讀寫的地址計數器都被清零,全滿、大于半滿狀態清除,全空和小于半滿置位,FIFO鎖存輸出為零。

與外部SRAM的連接及對SRAM的讀寫定時分析

CPLD與SRAM之間除去讀寫復用的地址和數據線以外,還需要有輸出使能信號/OE,讀寫信號/WE,片選信號/CS。地址線、數據線、/OE和/WE如前所述;片選信號由地址高位譯碼產生,在這里是把最高位取反,得到兩個片選信號。

讀寫信號的時序符合設計采用的IDT71128-12 SRAM的定時要求。

寫操作:

寫周期最小12ns,地址有效到結束寫最小10ns,片選到寫結束最小10ns,寫脈沖最小10ns,數據有效到寫結束最小7ns。地址在/WE之前建立,在/WE結束之后變化;數據保持到/WE無效再變化;在地址變化時,/WE、/CS不能都有效;在有效的寫時,/CS、/WE為低;

讀操作:

地址尋址時間最大12ns,讀周期最小12ns,片選尋址時間最大12ns,輸出使能到數據輸出有效最大6ns。在讀周期/WE為高,/OE為低,讀周期結束時地址和數據應該保持不變。

寫地址與MW脈沖的上升沿同時變化,在兩個脈沖之后,寫地址能夠穩定,這時/WE才有效,并且由于連續兩個讀寫脈沖之間最少有一個脈沖的間隔,而且MW比EW4要有延遲,同時總線選擇也是由MW決定,就保證了寫地址在/WE前有效并能保持到/WE結束;寫數據的三態緩沖由EW4打開,可以保持到/WE結束。

讀地址在上一個寫結束之后有效,由于讀地址變化比OE脈沖晚一個脈沖,/OE在OE結束時開始,保證了/OE開始的時候讀地址已穩定和讀周期時間符合要求;寫數據已由EW4關閉,由于讀寫之間的。

-

cpld

+關注

關注

32文章

1257瀏覽量

169600 -

緩沖器

+關注

關注

6文章

1930瀏覽量

45612 -

操作系統

+關注

關注

37文章

6889瀏覽量

123662

發布評論請先 登錄

相關推薦

利用外部SRAM和CPLD構成先進先出緩沖器FIFO的設計

利用外部SRAM和CPLD構成先進先出緩沖器FIFO的設計

評論