Lattice ispLEVER開發工具中關于ispMACH4000系列CPLD的一些常用constraint選項要點如下:

1. Dt_synthesisEDA

Yes: 允許fitter使用宏單元中的T觸發器來節省乘積項(PT )資源。建議選Yes。

2. Xor_synthesis

Yes: 允許fitter使用宏單元中的硬XOR門來節省乘積項(PT )資源。

當寄存器的輸入包含異步輸入引腳信號時,由于目前ispLEVER版本優化時考慮不夠全面,應避免使用Yes選項。否則,最好選Yes。

3. Nodes_collapsing_mode

Fmax: 該選項以速度性能為目標來優化邏輯。

Area: 該選項以最佳資源利用率為目標來優化邏輯。

Speed: 該選項以速度性能為目標且兼顧資源利用率來優化邏輯。

一般情況下,如果沒有性能要求時,而宏單元占用較多時,可考慮Area選項,尤其當Utilize Clock Enable選為No時。如果性能要求為首選時,可先考慮Fmax選項。而Speed選項在性能上接近Fmax選項,但資源利用率比Fmax選項好。以上選擇方法適合大多數情況,但具體設計對這三種選項都作嘗試,仍不失為可取的設計流程。

4. Max_pterm_collapse

該選項是指每個宏單元使用的最大乘積項數目。

一般情況下,選缺省值。如宏單元數未超過器件最大值,但fit失敗,可適當降低該值,或與Max_fanin結合考慮。

5. Max_fanin

該選項是指每個宏單元的最多扇入數目。

一般情況下,選缺省值。如宏單元數未超過器件最大值,但fit失敗(如ispLEVER提示某GLB輸入數超過36),可適當降低該值,如選16,或與Max_pterm_collapse結合考慮。

6. Max_fanin_limit

要針對Fmax優化模式。

若由于關鍵路徑的信號邏輯過于復雜使其扇入數目過多而引起fit失敗,可適當降低該值,如選20。

7. Max_pterm_limitEDA

要針對Fmax優化模式。

若由于關鍵路徑的信號邏輯過于復雜使其乘積項過多而引起fit失敗,可適當降低該值,如選20。

Max_pterm_limit和Max_fanin對布通率的影響如下:若引腳鎖定且設計所用的occupied macrocell數與器件的最大值有一定余量的情況下fit 失敗,可適當降低Collapsing Max. Product Term和Collapsing Max. Input的值,以便于通過fit。也就是說,若fit沒通過,可逐漸(分別)降低該兩項值(只要macrocell數沒超出器件允許值),來方便fit的布局和布線。例如,對ispMACH4000器件,一般來說,Collapsing Max. Product Term取16左右而Collapsing Max. Input取20左右時,有助于fit通過。但它有可能以犧牲性能為代價。

8. Clock_enable_optimization

一般選擇Keep_all來節省資源(即較少的Product Term和Macro Cell),但有時會對速度有一定影響。

9. Auto_buffering_for_high_glb_fanin

當出現GLB的扇入數目過高,fitter會嘗試自動加buffer來降低其扇入數,但這會增加延遲。

若引腳鎖定時fit失敗,尤其是許多輸出信號邏輯很復雜,可考慮選On。

10. Auto_buffering_for_low_bonded_io

要針對使用輸入寄存器的場合(尤其使用256MC/64IO)。

若設計中使用輸入寄存器,并且將輸入寄存器鎖定到固定GLB,或輸入寄存器較多且引腳鎖定,從而導致fit失敗,可選擇On,但這會增加延遲。

-

cpld

+關注

關注

32文章

1257瀏覽量

169613 -

寄存器

+關注

關注

31文章

5363瀏覽量

121083 -

邏輯

+關注

關注

2文章

833瀏覽量

29506

發布評論請先 登錄

相關推薦

超低功耗可編程系統器件PSD4000系列

MDO4000系列混合域分析儀應用基本功能總結

請問Impact JTAG工具是否支持ispMach4000V?

零功耗超快速CPLD器件ispMACH4000Z及其應用

ispMACH4000Z CPLD在消費類電子產品中的應用

零功耗超快速CPLD器件ispMACH4000Z及其應用

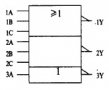

CMOS4000系列芯片手冊

關于ispMACH4000系列CPLD的功能介紹

關于ispMACH4000系列CPLD的功能介紹

評論