本文在說明全數字鎖相環的基礎上,提出了一種利用FPGA設計一階全數字鎖相環的方法,并給出了關鍵部件的RTL可綜合代碼,并結合本設計的一些仿真波形詳細描述了數字鎖相環的工作過程,最后對一些有關的問題進行了討論。

引言

鎖相環(PLL)技術在眾多領域得到了廣泛的應用。如信號處理,調制解調,時鐘同步,倍頻,頻率綜合等都應用到了鎖相環技術。傳統的鎖相環由模擬電路實現,而全數字鎖相環(DPLL)與傳統的模擬電路實現的PLL相比,具有精度高且不受溫度和電壓影響,環路帶寬和中心頻率編程可調,易于構建高階鎖相環等優點,并且應用在數字系統中時,不需A/D及D/A轉換。隨著通訊技術、集成電路技術的飛速發展和系統芯片(SoC)的深入研究,DPLL必然會在其中得到更為廣泛的應用。

這里介紹一種采用VERILOG硬件描述語言設計DPLL的方案。

DPLL結構及工作原理

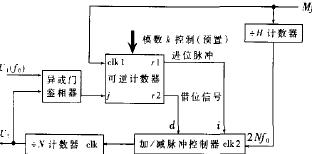

主要由鑒相器、K變模可逆計數器、脈沖加減電路和除N計數器四部分構成。K變模計數器和脈沖加減電路的時鐘分別為Mfc和2Nfc。這里fc是環路中心頻率,一般情況下M和N都是2的整數冪。本設計中兩個時鐘使用相同的系統時鐘信號。

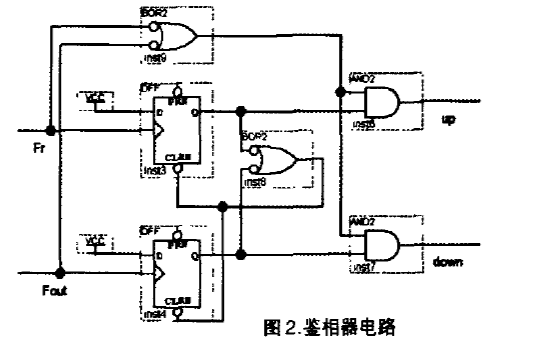

鑒相器

常用的鑒相器有兩種類型:異或門(XOR)鑒相器和邊沿控制鑒相器(ECPD),本設計中采用異或門(XOR)鑒相器。異或門鑒相器比較輸入信號Fin相位和輸出信號Fout相位之間的相位差Фe=Фin-Фout,并輸出誤差信號Se作為K變模可逆計數器的計數方向信號。環路鎖定時,Se為一占空比50%的方波,此時的絕對相為差為90°。因此異或門鑒相器相位差極限為±90°。

K變模可逆計數器

K變模可逆計數器消除了鑒相器輸出的相位差信號Se中的高頻成分,保證環路的性能穩定。K變模可逆計數器根據相差信號Se來進行加減運算。當Se為低電平時,計數器進行加運算,如果相加的結果達到預設的模值,則輸出一個進位脈沖信號CARRY給脈沖加減電路;當Se為高電平時,計數器進行減運算,如果結果為零,則輸出一個借位脈沖信號BORROW給脈沖加減電路。

脈沖加減電路

脈沖加減電路實現了對輸入信號頻率和相位的跟蹤和調整,最終使輸出信號鎖定在輸入信號的頻率和信號上。

除N計數器

除N計數器對脈沖加減電路的輸出IDOUT再進行N分頻,得到整個環路的輸出信號Fout。同時,因為fc=IDCLOCK/2N,因此通過改變分頻值N可以得到不同的環路中心頻率fc。

DPLL部件的設計實現

了解了DPLL的工作原理,我們就可以據此對DPLL的各部件進行設計。DPLL的四個主要部件中,異或門鑒相器和除N計數器的設計比較簡單:異或門鑒相器就是一個異或門;除N計數器則是一個簡單的N分頻器。下面主要介紹K變模可逆計數器和脈沖加減電路的設計實現。

K變模可逆計數器的設計實現

K變模可逆計數器模塊中使用了一個可逆計數器Count,當鑒相器的輸出信號dnup為低時,進行加法運算,達到預設模值則輸出進位脈沖CARRY;為高時,進行減法運算,為零時,輸出借位脈沖BORROW。Count的模值Ktop由輸入信號Kmode預設,一般為2的整數冪,這里模值的變化范圍是23-29。模值的大小決定了DPLL的跟蹤步長,模值越大,跟蹤步長越小,鎖定時的相位誤差越小,但捕獲時間越長;模值越小,跟蹤步長越大,鎖定時的相位誤差越大,但捕獲時間越短。

K變模可逆計數器的VERILOG設計代碼如下(其中作了部分注釋,用斜體表示):

module KCounter(Kclock,reset,dnup,enable, Kmode,carry,borrow);

input Kclock; /*系統時鐘信號*/

input reset; /*全局復位信號*/

input dnup; /*鑒相器輸出的加減控制信號*/

input enable; /*可逆計數器計數允許信號*/

input [2:0]Kmode; /*計數器模值設置信號*/

output carry; /*進位脈沖輸出信號*/

output borrow; /*借位脈沖輸出信號*/

reg [8:0]Count; /*可逆計數器*/

reg [8:0]Ktop; /*預設模值寄存器*/

/*根據計數器模值設置信號Kmode來設置預設模值寄存器的值*/

always @(Kmode)

begin

case(Kmode)

3'b001:Ktop<=7;

3'b010:Ktop<=15;

3'b011:Ktop<=31;

3'b100:Ktop<=63;

3'b101:Ktop<=127;

3'b110:Ktop<=255;

3'b111:Ktop<=511;

default:Ktop<=15;

endcase

end

/*根據鑒相器輸出的加減控制信號dnup進行可逆計數器的加減運算*/

always @(posedge Kclock or posedge reset)

begin

if(reset)

Count<=0;

else if(enable)

begin

if(!dnup)

begin

if(Count==Ktop)

Count<=0;

else

Count<=Count+1;

end

else

begin

if(Count==0)

Count<=Ktop;

else

Count<=Count-1;

end

end

end

/*輸出進位脈沖carry和借位脈沖borrow*/

assign carry=enable&(!dnup) &(Count==Ktop);

assign borrow=enable&dnup& (Count==0);

endmodule

脈沖加減電路的設計實現

脈沖加減電路完成環路的頻率和相位調整,可以稱之為數控振蕩器。當沒有進位/借位脈沖信號時,它把外部參考時鐘進行二分頻;當有進位脈沖信號CARRY時,則在輸出的二分頻信號中插入半個脈沖,以提高輸出信號的頻率;當有借位脈沖信號BORROW時,則在輸出的二分頻信號中減去半個脈沖,以降低輸出信號的頻率。VERILOG設計代碼如下:

module IDCounter(IDclock,reset,inc,dec,IDout);

input IDclock; /*系統時鐘信號*/

input reset; /*全局復位信號*/

input inc; /*脈沖加入信號*/

input dec; /*脈沖扣除信號*/

output IDout; /*調整后的輸出信號*/

wire Q1, Qn1, Q2, Qn2, Q3, Qn3;

wire Q4, Qn4, Q5, Qn5, Q6, Qn6;

wire Q7, Qn7, Q8, Qn8, Q9, Qn9;

wire D7, D8;

FFD FFD1(IDclock, reset, inc, Q1, Qn1);

FFD FFD2(IDclock, reset, dec, Q2, Qn2);

FFD FFD3(IDclock, reset, Q1, Q3, Qn3);

FFD FFD4(IDclock, reset, Q2, Q4, Qn4);

FFD FFD5(IDclock, reset, Q3, Q5,Qn5);

FFD FFD6(IDclock, reset, Q4, Q6,Qn6);

assign D7=((Q9 & Qn1 & Q3) | (Q9 & Q5 & Qn3));

assign D8=((Qn9 & Qn2 & Q4) | (Qn9 & Q6 & Qn4));

FFD FFD7(IDclock, reset, D7, Q7, Qn7 );

FFD FFD8(IDclock, reset, D8, Q8, Qn8);

JK FFJK(IDclock, reset, Qn7, Qn8, Q9, Qn9);

assign IDout = (!Idclock)|Q9;

endmodule

其中,FFD為D觸發器,JK為JK觸發器。

當環路的四個主要部件全部設計完畢,我們就可以將他們連接成為一個完整的DPLL,進行仿真、綜合、驗證功能的正確性。

DPLL的FPGA實現

本設計中的一階DPLL使用XILINX公司的FOUNDATION4.1軟件進行設計綜合,采用XILINX的SPARTAN2系列的XC2S15 FPGA器件實現,并使用Modelsim5.5d軟件進行了仿真。結果表明:本設計中DPLL時鐘可達到120MHz,性能較高;而僅使用了87個LUT和26個觸發器,占用資源很少。下面給出詳細描述DPLL的工作過程。

(1) 當環路失鎖時,異或門鑒相器比較輸入信號(DATAIN)和輸出信號(CLOCKOUT)之間的相位差異,并產生K變模可逆計數器的計數方向控制信號(DNUP);

(2) K變模可逆計數器根據計數方向控制信號(DNUP)調整計數值,DNUP為高進行減計數,并當計數值到達0時,輸出借位脈沖信號(BORROW);為低進行加計數,并當計數值達到預設的K模值時,輸出進位脈沖信號(CARRY);

(3) 脈沖加減電路則根據進位脈沖信號(CARRY)和借位脈沖信號(BORROW)在電路輸出信號(IDOUT)中進行脈沖的增加和扣除操作,來調整輸出信號的頻率;

(4) 重復上面的調整過程,當環路進入鎖定狀態時,異或門鑒相器的輸出DNUP為一占空比50%的方波,而K變模可逆計數器則周期性地產生進位脈沖輸出CARRY和借位脈沖輸出BORROW,導致脈沖加減電路的輸出IDOUT周期性的加入和扣除半個脈沖.

-

FPGA

+關注

關注

1640文章

21903瀏覽量

611456 -

鎖相環

+關注

關注

35文章

591瀏覽量

88288 -

pll

+關注

關注

6文章

838瀏覽量

135871 -

數字鎖相環

+關注

關注

3文章

34瀏覽量

13572

發布評論請先 登錄

相關推薦

評論