1 引言

FPGA的出現大大縮短了集成電路設計的周期,使產品上市的時間大大縮短,并減少了設計成本。FPGA的應用越來越廣泛,并且其市場份額也越來越大。但是逐漸擴大的芯片規模和更加復雜的芯片結構,給測試帶來了越來越大的困難,測試成本大大增加,如何降低測試成本是很多商家和研究者共同面對的一個問題。有關FPGA測試的研究有很多。

FPGA主要由可編程邏輯資源,可編程連線資源,可編程輸入輸出資源組成。其中連線資源占芯片面積的60%以上,并且隨著器件規模增大,連線也越來越復雜,其出現故障的可能性很大,所以連線資源測試在FPGA測試中扮演了一個很重要的角色。芯片測試包括故障檢測、故障診斷和故障冗余。故障檢測只檢測芯片中有沒有故障,如果芯片中有故障就把此芯片扔掉;故障診斷不僅要檢測芯片中是否有故障,還要確定故障的位置和類型;而故障冗余是指,對于有故障的芯片采取一定的方法使得芯片可以繼續使用,而不至于浪費。可以看到,故障檢測是故障診斷的基礎,而故障冗余又以故障診斷為前提,在本文的設計中,故障檢測及故障診斷都可以支持,只要設計好需要的測試配置就可以了。

對于連線資源測試,出現了很多種方法,大致分為三類:(1)非內建自測試方法(Non—BIST),利用專有的測試儀器對芯片進行配置并加測試向量對芯片進行測試;(2)利用芯片內部可編程邏輯資源對連線資源進行測試,這是內建自測試方法(BIST),在芯片內部通過配置可編程邏輯資源自動產生測試向量,并且對測試結果進行判斷。以上兩種方法都是利用FPGA的可編程特性對芯片進行測試的;(3)利用可測試設計方便芯片進行測試,通過一定的硬件消耗,在芯片內部加上一定的輔助電路,使得測試比較方便、快速。本文提出的方法屬于第三類方法。

與ASIC測試不同,FPGA測試需要將測試需要的配置下載到芯片中,然后加測試向量對芯片進行測試,其測試時間主要由編程下載的時間來決定,所以編程下載時間決定了測試的成本,很多研究者通過減少測試配置數目來減少測試時間,從而降低測試成本。

本文的出發點不是通過減少測試配置數目來減少測試時問,而是從另外一個角度對測試開關盒連線資源時間的減少進行了研究。通過一定的硬件消耗大大減少了編程下載的時間,降低了測試成本。

2 基于SRAM的FPGA結構簡介

FPGA通常有三個基本的組成部分,即可編程邏輯單元((Sonfigurable Logic Block,以下簡稱CLB)、可編程輸入輸出單元(Input and Output Block,以下簡稱IOB)及可編程連線資源。通常CLB包含組合邏輯部分和時序邏輯部分,組合邏輯一般包括查詢表(Look—up Table)和相關的多路選擇器(Multiplexer)。而時序邏輯部分包含觸發器(DFF)和一些相關的多路選擇器。IOB則提供了FPGA內部和外部的一個接口,連線資源則提供CLB與IOB之間以及各CLB之間的通訊。

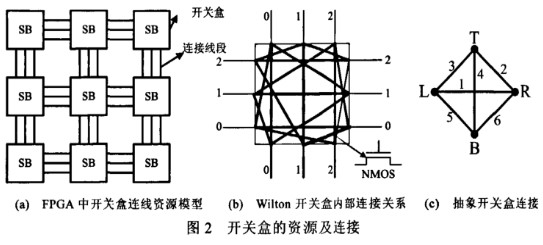

FPGA芯片的基本結構如圖1其原因所示,現在的FPGA芯片結構越來越復雜,但都包含這些基本的組成部分。開關盒(Switch Box,以下簡稱SB)將水平和豎直連線資源進行切換。連接盒(Connection Box,以下簡稱CB)連接CLB的輸入輸出到連線資源中。在FPGA芯片中,由于連線資源比較復雜,所以測試花費時間會很長。其中把開關盒抽出來可以構造開關盒資源圖,其中包括開關盒內部的可編程開關以及開關盒之間的連接線段,如圖2(a)所示。

FPGA開關盒資源模型包括m×m個SB以及相鄰的SB之間連接開關盒的k條連接線段,其中SB內部的連接關系如圖2(b)所示。其中粗線代表一個NMOS管作為傳輸管,用來控制線段的連接,傳輸管的開和閉由編程信息來控制,編程信息存儲在SRAM單元中。SB內部有很多傳輸管,其中兩條線段之間有傳輸管相連的,稱為可連接線段,沒有傳輸管的,稱為不可連接線段。圖2(c)是抽象的開關盒連接關系,其中四個方向分別為T,B,L,R,黑點表示此方向的連接線段的集合,每條連接線段可以另外三條連接線段連接,這三條連接線段分別位于其他三個方向,其中的數字表示傳輸管的編號。比如3,表示左邊的連接線段連接上邊的連接線段。

在FPGA連線資源中,主要包含連接線段,傳輸管和CB中的連線資源。連接盒一般和邏輯資源放在一起進行測試,本文著重于開關盒連線資源的測試。

3 測試所需要的配置

3.1 測試采用的故障模型

1)線段開路故障,線段在制造過程中中間斷開,不能正常傳輸信號,輸出端的狀態固定;

2)線段的固定O故障,不管輸入信號是0還是l,線段總固定在0狀態;

3)線段的固定l故障,不管輸入信號是0還是1,線段總固定在1狀態;

4)傳輸管的固定0故障,也就是常開故障,SRAM編程信息不能改變此開關的狀態;

5)傳輸管的固定l故障,也就是常閉故障,SRAM編程信息不能改變此開關的狀態;

6)線段的橋接故障,兩條線段之間短路,當分別在橋接的兩條金屬線上加相反的信號時,因為橋接兩線的輸出信號是相同的。

3.2 測試所需配置

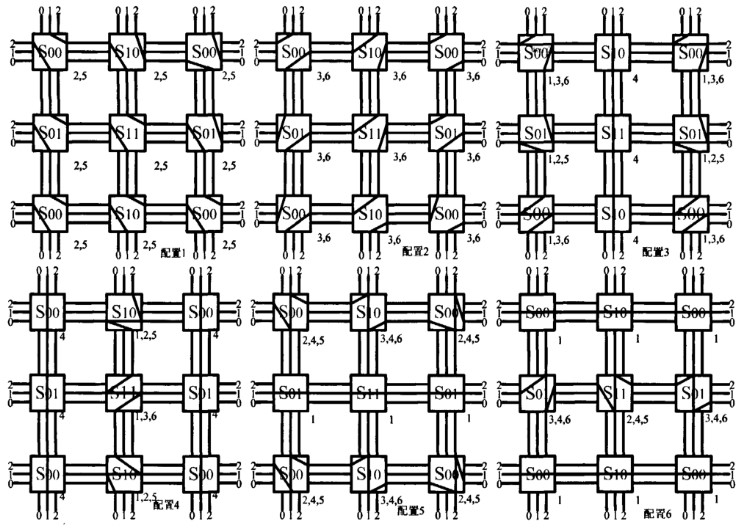

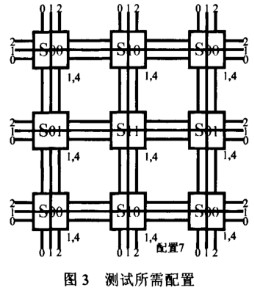

在測試之前,需要將配置信息下載到FPGA芯片中,然后施加測試矢量進行測試。本文以[3]中的配置為例說明此可測性設計,在此采用Wilton開關盒結構,配置原理與[3]一樣。測試配置如圖3所示。

上述的7種配置中同一個SB內編號相同的開關的狀態都是一樣的。配置中SB旁邊的數字表示SB內需要閉合的傳輸管的編號。圖中SB的編號Smn,其中:S00:處于奇行奇列的SB;S01:處于偶行奇列的SB;S10:處于奇行偶列的SB;S11:處于偶行偶列的SB。編號相同的SB在同一個測試配置中狀態是完全一樣的。如果對故障進行診斷,需要配置1到配置6。

1)配置l和配置2能夠診斷任何單個線段開路故障、線段固定故障和線段橋接故障;

2)配置l、2、3、4、5和配置6能夠診斷任何編號為3、6的單個傳輸管固定O故障;

3)配置1、2、3、4、5和配置6能夠診斷任何編號為2、5的單個傳輸管固定0故障;

4)配置3、4、5和配置6能夠診斷任何編號為4、1的單個傳輸管固定0故障;

5)配置l(或配置2)、配置3和配置4能夠診斷任何編號為l的單個傳輸管固定1故障;

6)配置1(或配置2)、配置3和配置4能夠診斷任何編號為4的單個傳輸管固定1故障;

7)配置3、4、5和配置6能夠診斷編號為2、3、5、6的單個傳輸管固定1故障。

如果僅僅是進行故障檢測,配置1、2和配置7就夠了。

4 移位寄存器鏈測試方法

由于FPGA規模越來越大,編程SRAM單元數量巨大,下載測試配置的時間就非常大。在測試中,需將配置下載到芯片中,然后加測試矢量對連線資源進行測試,但是在下載的過程中,也同時將邏輯資源的編程數據下載到了芯片中,這種下載對測試連線資源是沒有用的,所以這部分時間對連線資源測試來說是多余的。

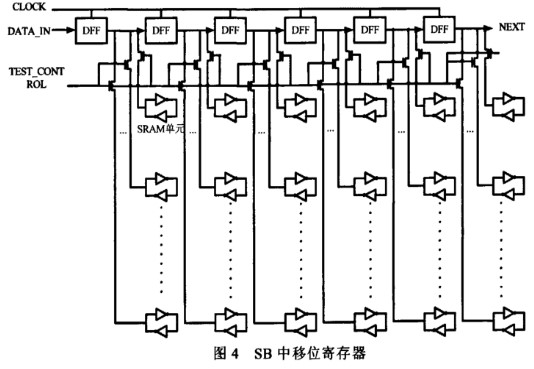

從圖2的開關盒連接關系和圖3中的測試配置可以看出,在一個開關盒內部編號相同的開關狀態是一樣的,所以在這種情況下就可以在開關盒內部增加6個觸發器,每個觸發器的輸出端連接到相同編號的所有傳輸管上,并且將所有的觸發器連接成多條移位寄存器鏈,這樣在配置的時候就可以將事先設計好的配置數據通過移位寄存器鏈下載相對應的開關盒內SRAM單元中,每個觸發器可以并行配置與其相連的SRAM單元,時間又可以節省很多。如圖4所示。各信號意義如下:

1)DATA IN:將設計好的編程數據通過移位寄存器移位到相對應的位置上;

2)DATA 0UT:移位鏈的輸出端;

3)TEST CONTROL:控制芯片為測試狀態或正常工作狀態。當其為1時,所有的測試控制NMOS管都閉合,將觸發器的輸出寫到相應的SRAM單元中;而當其為0時,所有的測試控制NMOS管都斷開,芯片處于正常工作狀態,測試電路和工作電路完全斷開,不會影響芯片的正常工作;

4)NEXT:連接到另外一個開關盒的DATA IN,將所有的觸發器連接成多條移位寄存器鏈;

5)CLOCK:時鐘控制端,控制數據的移位。其他的一些輸入控制端沒有列出。

測試方法:比如要實現圖3中測試配置3,因為在這個配置中,開關盒S00需要將編號為1、3、6的傳輸管閉合,所以此開關盒寄存器的配置為101001,開關盒S10,S11需要將編號為4的傳輸管閉合,其需要的配置為000100,而開關盒Sol將閉合傳輸管l、2、5,所以其配置為110010,所以對于配置3中的9個開關盒來說,需要的配置序列為:101001,000100,10100l;1 100lO,000100,110010;101001,000100,101001。

在測試的時候分別將6種配置的測試序列分別通過下載端口下載到芯片中,實現測試需要的配置對開關盒進行測試。

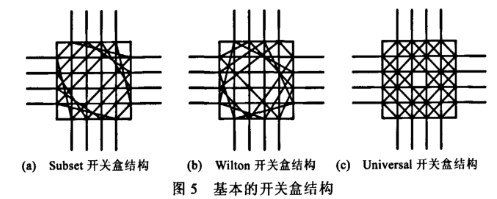

三種常用的SB結構如圖5所示。

這三種結構中,同樣一個方向的一個連接線段可以和其他三個方向的一個線段相連接,只是連接的線段編號不同,不過對應的配置還是一樣的。以上的設計同樣可以應用于這三種開關盒結構。

如果是不規則的SB結構,可以通過設計需要的測試配置來決定需要增加的觸發器數目,在測試配置中,盡可能使SB內的狀態相同的傳輸管多一些。一個基本的原則就是,在一個SB內部所有可以配置成同樣狀態的開關都可以利用一個觸發器來進行下載。

如何測試芯片內部增加的電路呢?因為移位鏈有一個輸出端DATA OUT,可以通過此輸出端來驗證移位鏈的正確性。對于傳輸管可以配合開關盒的測試來對其進行測試。如果下載以后功能正確則傳輸管沒有常開故障。下載一定功能電路以后,將TEST CONTROL信號置0狀態,即將所有的傳輸管斷開,然后下載一個編程數據和之前相反的位流文件,如果功能未改變說明傳輸管沒有常閉故障。

5 結果

以下從三個方面來說明此可測性設計的特點:

1)測試時間比較

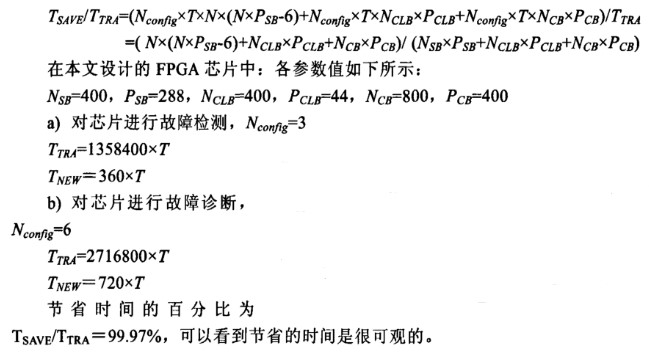

首先定義幾個參數,假定芯片的規模是N×N個邏輯單元,即有N行和N列邏輯單元。

NSB=N2:芯片中開關盒的個數 PS8:一個開關盒內部編程開關的數目

NCLB:芯片中CLB的個數 PCLB:一個CLB內部的編程開關的數目

NCB:芯片中CB的個數 PCB:一個CB內部的編程開關數目

T:編程下載的時鐘周期 Nconfig:測試需要的配置數目

利用傳統的測試方法測試SB互連資源時,需要將測試設計的配置數據下載到芯片中,此配置的編程數據包含了芯片內部所有編程SRAM的編程信息,所以在下載的時候同樣將測試用不到的CLB,CB內部的編程信息也下載進去了,但是這部分的下載對測試SB是沒有用的,所以時間就浪費了。傳統的測試方法需要的時間為:

![]()

利用本文提出的可測性設計方法,測試數據僅僅對SB內部的SRAM單元進行配置,而且是并行的,這樣就大大減小了測試SB連線資源配置需要的時間,在設計中可以實現N條移位鏈,利用這種方法測試需要的時間TNEW=6xNxNconfigxT

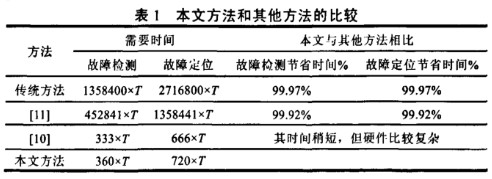

對于上述芯片的條件,測試時問比較如表1所示。

2)硬件的消耗*估

假設設計中使用的DFF內有30個MOS管,所以在設計中每個SB消耗的MOS管數目為6x30+PSB,而SB中邏輯資源包含的MOS管數目為PSBx6+NBUF,其中PSBx5是SRAM單元含有的MOS管數目,PSB是SB內傳輸管的數目,NBUF是SB Buffer中包含的MOS管數目。而在FPGA芯片中一般SB中邏輯資源占芯片面積的28%,所以硬件消耗的面積百分比:0.28x(6x30+PSB)/(PSBx6+NBUF)。

在本文設計的FPGA芯片中,其中只有一種開關盒。每個開關盒內部Buffer含有的MOS管數目為912個,所以如果在芯片中加入可測性移位鏈所消耗的面積百分比:是0.28x(6x30+216)/(216x6+912)=5.27%,消耗的面積可以接受。

由以上可以看出,文獻方法在測試的過程中需要利用傳統的方法下載測試少數種子配置,需要時問較多,可以看到本文提出的方法遠遠比文獻改進很多,消耗的硬件僅稍有增加。對于文獻采用的方法,需要的測試時問與本文方法可相比較,但它的硬件及內部控制比較復雜,并且測試需要相應的一些外部設備來判斷是否為測試需要的配置。而本文提出的方法則比較簡單,而且測試需要的時間和硬件面積的增加達到了一個比較好的平衡。

3)對芯片的影響

此可測性設計不會對芯片的正常工作產生影響,因為在芯片正常工作的時候,測試電路完全與芯片內部電路分開。所以對于芯片使用者來說不存在性能方面的問題。

6 結論

本文提出在FPGA芯片內插入多條移位寄存器鏈的方法,可使測試開關盒連線資源的時問比傳統的測試方法和已有的一種方法時間上減少了99%以上,大大降低了測試的時間,降低了測試成本,并且消耗的硬件面積比大約在5%左右,在可接受的范圍內。

-

FPGA

+關注

關注

1638文章

21861瀏覽量

610193 -

芯片

+關注

關注

459文章

51757瀏覽量

431427 -

觸發器

+關注

關注

14文章

2027瀏覽量

61638

發布評論請先 登錄

相關推薦

評論