高清晰度數(shù)字電視(HDTV)技術(shù)是當(dāng)今世界上最先進(jìn)的圖像壓縮編碼技術(shù)和數(shù)字通信技術(shù)的結(jié)合。它代表一個(gè)國的科技綜合實(shí)力,蘊(yùn)藏著巨大的市場潛力。數(shù)字電視地面廣播編碼正交頻分復(fù)用(CMOFDM)傳輸系統(tǒng)以其較強(qiáng)的抗多徑干擾性能、易于實(shí)現(xiàn)移動(dòng)接收等優(yōu)點(diǎn)在HDTV的研究中占有很重要的地位。而 COFDM系統(tǒng)中編、解碼技術(shù)是影響系統(tǒng)性能的一個(gè)重要因素。本文正是基于一種最大似然譯碼——Viterbi(VB)譯碼算法思想,從FPGA實(shí)現(xiàn)的角度探討在COFDM系統(tǒng)中內(nèi)碼(收縮卷積碼)的解碼。

1 設(shè)計(jì)算法簡述

在HDTV 地面廣播COFDM系統(tǒng)中,所用內(nèi)碼為收縮卷積碼,除1/2主碼率外,還有2/3。3/4、5/6、7/8碼率的卷積編碼。在實(shí)際的傳輸信道中,噪聲一般是加性高斯白噪聲(AWGN),輸入AWGN信道的是二進(jìn)制信號(hào)序列。為了充分利用信道輸出信號(hào)的信息,提高傳輸系統(tǒng)譯碼的可靠性,首先把信道的輸出信號(hào)量化,將Q電平量化序列輸入Viterbi譯碼器,因此本文采用的VB譯碼算法為軟判決譯碼算法。

1.1 主碼率1/2的卷積碼編碼

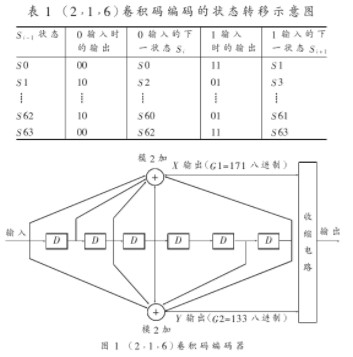

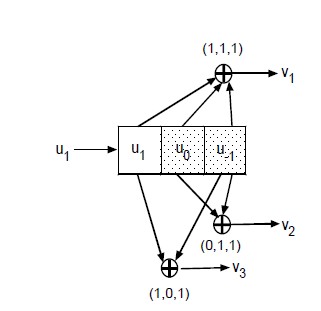

目前,在國際衛(wèi)星通信和很多通信系統(tǒng)中,(2,1,6)碼是首選的使用VB譯碼的標(biāo)準(zhǔn)卷積碼。由于該碼能使誤碼率達(dá)到最小,且能克服相位誤差,所以在 HDTV地面廣播COFDM傳輸系統(tǒng)中,內(nèi)碼采用(2,1,6)碼,它的子生成元為(171,133),均為八進(jìn)制。對應(yīng)的生成多項(xiàng)式G(D)=[1+D +D2+D3+D6,1+D2+D3+D5+D6],df=10。其編碼器的實(shí)現(xiàn)框圖如圖1。

由于(2,1,6)碼有62個(gè)狀態(tài),為直觀直見,采用列表的方法來表述它的籬笆圖,如表1所示。

1.2 收縮卷積碼的實(shí)現(xiàn)

為了實(shí)現(xiàn)多碼率傳輸,在提高碼率的情況下不致使譯碼器的復(fù)雜性增加,在本設(shè)計(jì)中對(2,1,6)碼進(jìn)行增信刪余(Puncctured)。如圖1所示,在經(jīng)上述編碼后,對輸出碼字中的特定位置予以刪除。這樣右以產(chǎn)生碼率為2/3、3/4、5/6、7/8的較高碼率的卷積碼。

1.3 維特比譯碼算法簡述

Viterbi (VB)譯碼算法是一種最大似然譯碼算法。在收端的譯碼過程中,根據(jù)對接收碼元處理方式的不同,分為硬判決和軟判決譯碼。在同一譯碼算法下,雖然硬判決譯碼較軟判決譯碼簡單而易于實(shí)現(xiàn),但在性能上要損失2~3dB。因此本文的FPGA實(shí)現(xiàn)是基于軟判決來討論的。具體算法如下:

(1)從某一時(shí)間單位j=m開始,對進(jìn)入每一狀態(tài)的所有長為j段分支的部分路徑,計(jì)算部分路徑度量。對64態(tài)的每個(gè)狀態(tài),挑選并儲(chǔ)存一條有最大度量的部分路徑及部分度量值作為留選路徑。

(2)j增加1,把此時(shí)刻進(jìn)入每一狀態(tài)的所有分支度量與同這些分支相加的前一時(shí)刻的留選路徑的度量相加,得到此時(shí)刻進(jìn)入每一狀態(tài)的留選路徑,加以存儲(chǔ)并刪去其它所有路徑。

(3)為了FPGA設(shè)計(jì)中達(dá)到較高的時(shí)鐘速度,本文在判決和輸出路徑寄存器的信息時(shí),把所有64個(gè)路徑寄存器的第一段信息元取出,按大數(shù)判決準(zhǔn)則輸出第一段信息元。

2 維特比譯碼的FPGA實(shí)現(xiàn)

本文是在Altera公司推出的環(huán)境中,采用AHDL語言和原理圖仿真結(jié)合的方法來完成VB譯碼器的FPGA實(shí)現(xiàn)。

2.1 譯碼器的整體實(shí)現(xiàn)方案

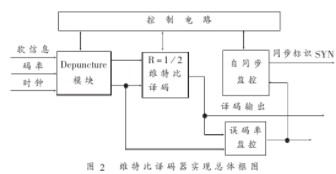

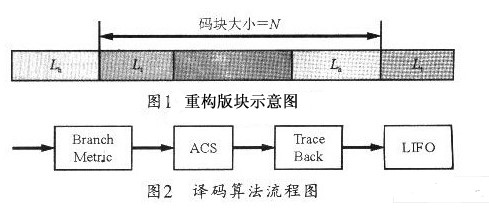

譯碼器的整個(gè)方案如圖2所示。發(fā)端的數(shù)據(jù)徑由信道傳輸過來,經(jīng)過同步和信道估計(jì),根據(jù)CSI信息對數(shù)據(jù)進(jìn)行維特比量化,將量化后的信息解內(nèi)交織后送入維特比解碼單元。

接收到前端的碼字后,首先須在發(fā)端的刪除位置上填充特定的虛假碼元,這一功能由Depuncture單元來完成。并由該單元產(chǎn)生量度計(jì)算禁止脈沖,送入主譯碼器,使譯碼器在譯碼時(shí)禁止對這些碼元作量度計(jì)算。

主譯碼器的譯碼輸出送到誤碼率監(jiān)控單元,通過對誤碼率的統(tǒng)計(jì)來判定數(shù)據(jù)是否為同步接收,同時(shí)將該信息送入自同步監(jiān)控單元,以供調(diào)整同步使用。當(dāng)整個(gè)譯碼系統(tǒng)同步后,將輸出一同步標(biāo)識(shí),表示系統(tǒng)已經(jīng)同步,同時(shí)通過同步單元維持同步態(tài)。

2.2 譯碼器分模塊的實(shí)現(xiàn)

2.2.1 R=“1”/2的維特比譯碼模塊

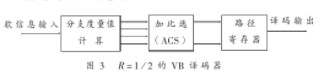

根據(jù)上述VB算法,對于一個(gè)軟判決譯碼器,應(yīng)具備以下幾部分:

(1)度量值寄存器:用來存儲(chǔ)各路徑的度量值。其前級(jí)應(yīng)有一狀態(tài)發(fā)生器,產(chǎn)生64個(gè)狀態(tài)和分支值。

(2)累加器、比較器和判決器。分別用來進(jìn)行軟距離的累加,比較各路徑度量值的大小并選擇輸出信息元的值。

(3)路徑寄存器:用來存儲(chǔ)幸存路徑。

模塊設(shè)計(jì)如圖3示。

分支度量值計(jì)算部分,首先根據(jù)接收的軟判決信息計(jì)算出每一時(shí)刻各分支度量值,在Depuncture模塊輸出禁止脈沖的位置不能進(jìn)行度量值運(yùn)算。將該結(jié)果送入加比選電路,由表1所得的各狀態(tài)間轉(zhuǎn)移時(shí)的輸出分別累加分支度量,并利用比較和選擇電路得到留選路徑,把此信息送入路徑寄存器。當(dāng)路徑寄存器中64個(gè)狀態(tài)的路徑度量相等時(shí),經(jīng)過大數(shù)判決電路輸出譯碼信息,送入下級(jí)的誤碼監(jiān)控和自同步電路。

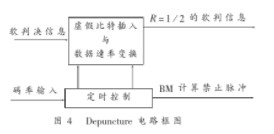

2.2.2 Depuncture電路

在發(fā)端經(jīng)編碼和刪除后的數(shù)據(jù)個(gè)有大于1/2速率的數(shù)據(jù)率。為了不增加譯碼器的難度,采用如圖4所示結(jié)構(gòu)的Depuncture電路,把數(shù)據(jù)速率變回1/2,并在約定的位置插入虛假碼元。通過定時(shí)控制電路來確定插入虛假比特的時(shí)刻,同時(shí)產(chǎn)生禁止計(jì)算脈沖,與生成的并行數(shù)據(jù)一起送入下級(jí)。

2.2.3 自同步電路

在傳輸數(shù)據(jù)的過程中,以2/3碼率為例,它的傳輸序列格式為“X1Y1Y2”,即刪除了“X2”位置的碼元。在接收到的軟判決信息序列中,首先必須確定 “X1”位置的數(shù)據(jù),否則就無法確定插入虛假碼元的位置。而“X1”這一起始信息系統(tǒng)無法傳送,在本設(shè)計(jì)中自同步電路就是來完成捕獲“X1”這一功能的。如圖2后半部分所示,譯碼器先假定任一位置為“X1”,通過譯碼結(jié)果結(jié)合誤碼監(jiān)控來判斷是否同步,并把這一信息反饋給Depuncture電路,同步標(biāo)識(shí) SYN為高則表明電路同步,前級(jí)就會(huì)維持該同步;否則,前級(jí)電路將會(huì)繼續(xù)捕獲,直至電路同步。

3 譯碼器的性能

本文是在軟件仿真的基礎(chǔ)上,結(jié)合硬件實(shí)現(xiàn)的可行性和COFDM傳輸系統(tǒng)中的高數(shù)據(jù)率的實(shí)際情況,權(quán)衡資源占有和速度的矛盾進(jìn)行的一種優(yōu)化設(shè)計(jì)。

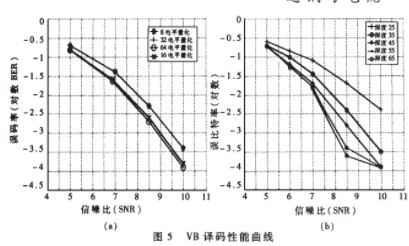

3.1 譯碼性能的軟件仿真

軟判決譯碼器的輸入信息是經(jīng)軟判決量化后的數(shù)據(jù)。但量化的電平數(shù)與碼元的可信度有直接的關(guān)系,量化電平越多,則越能精確地接近似然函數(shù),越能準(zhǔn)確反映接收碼元的可信度,從而使譯碼器的譯碼性能更接近最大似然譯碼。但隨著量化電平數(shù)目的增多,譯碼的復(fù)雜性也很快增長,實(shí)現(xiàn)的難度也隨之加大。圖5(a)用 MTLAB仿真得出了量化電平數(shù)對譯碼性能的影響。從波形可以看出,在16電平以上(32、64電平)量化時(shí),誤碼與信噪比的性能曲線很接近,而相對于后兩種量化來講,16電平的FPGA電路實(shí)現(xiàn)要方便得多。因此本設(shè)計(jì)采用4比特量化。

在FPGA實(shí)現(xiàn)譯碼的過程中,譯碼深度是另外一個(gè)重要的決定譯碼性能的參數(shù)。圖5(b)是仿真得到的在采用16電平量化時(shí),對應(yīng)不同深度下誤碼率與信噪比的關(guān)系。可以看出,當(dāng)譯碼深度大于55時(shí),SNR基本不再增加。BER=10 -3時(shí),深度為55的譯碼較45有0.65dB的增益。但從資源的占有程度來講,前者卻要多用640個(gè)邏輯單元。本設(shè)計(jì)采用的譯碼深度為45。

3.2 VB譯碼器的電路性能

基于上述分析,通過大量的電路和軟件仿真,用FPGA方法完成了用于HDTV COFDM傳輸系統(tǒng)中的VB譯碼器的設(shè)計(jì)。通過用Tektronix TLA 700邏輯分析儀(數(shù)據(jù)深度為512K字節(jié))調(diào)試,將采集到的每組可達(dá)520K字節(jié)的數(shù)據(jù)用軟件仿真進(jìn)行驗(yàn)證,確保在無擾信道情況下誤差率為零,并在測試過程中驗(yàn)證了該譯碼電路具有的以下性能。

(1)適用于高速率系統(tǒng),電路最高工作時(shí)鐘可達(dá)70MHz,整個(gè)電路占用邏輯單元為7620個(gè)。同時(shí)不占RAM和ROM單元,為同一片內(nèi)的其它電路模塊節(jié)省了寶貴的共享內(nèi)存資源。

(2)主碼率為1/2,同時(shí)在不增加電路復(fù)雜性的情況下,可以對2/3,3/4,5/6,6/7,7/8等多種碼率的數(shù)據(jù)進(jìn)行譯碼。

(3)可自動(dòng)實(shí)現(xiàn)譯碼同步和BER監(jiān)控。

(4)采用并行電路設(shè)計(jì),使電路在高時(shí)鐘情況下可以穩(wěn)定工作。

(5)采用FPGA技術(shù),易于修改電路內(nèi)部參數(shù),軟判決可以兼容硬判決。通過內(nèi)部參數(shù)的變化可以滿足不同約束長度(7、9)譯碼的要求。

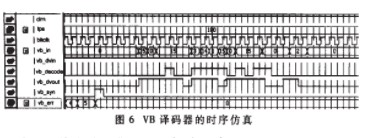

圖6 給出了在FPGA電路的時(shí)序仿真波形。其中TPS為系統(tǒng)通過傳輸參數(shù)信令提供的碼率信息。共有1/2、2/3、3/4、5/6、7/8等多種碼率信息。電路工作時(shí)鐘bitclk根據(jù)COFDM傳輸系統(tǒng)的要求為60MHz。Vb_in為4-bit量化后的軟判決信息,譯碼輸出串行比特泫,并標(biāo)注有數(shù)據(jù)有效和是否同步的標(biāo)志。Vb_err用來監(jiān)控誤碼,向電路發(fā)出提示信息,使電路始終工作在同步態(tài)。

本文的FPGA實(shí)現(xiàn)是基于Altera公司Quartus和Maxplus II電路仿真環(huán)境和該公司APEX TM EP20K600EBC652-1XES系列芯片來完成的。應(yīng)用于高精晰度數(shù)字電視COFDM傳輸系統(tǒng)的接收機(jī)頂盒的設(shè)計(jì)中,經(jīng)過性能測試,達(dá)到了系統(tǒng)指標(biāo)要求。同時(shí),該設(shè)計(jì)也為HDTV機(jī)頂盒的ASIC設(shè)計(jì)奠定了良好的基礎(chǔ)。

-

FPGA

+關(guān)注

關(guān)注

1638文章

21877瀏覽量

610623 -

數(shù)字電視

+關(guān)注

關(guān)注

3文章

323瀏覽量

45585 -

衛(wèi)星通信

+關(guān)注

關(guān)注

12文章

739瀏覽量

39074

發(fā)布評論請先 登錄

相關(guān)推薦

什么是卷積碼? 什么是卷積碼的約束長度?

大佬們,問一下用FPGA實(shí)現(xiàn)卷積碼編解碼的難度,畢設(shè)選了這個(gè)

基于CPLD的卷積碼編解碼器的設(shè)計(jì)

卷積碼的Viterbi高速譯碼方案

卷積碼的Viterbi高速譯碼方案

基于OCDMA的新型卷積碼譯碼方案

卷積碼/Viterbi譯碼,卷積碼/Viterbi譯碼是什么

卷積碼,卷積碼是什么意思

卷積碼,什么是卷積碼

LTE中Tail-biting卷積碼的譯碼器設(shè)計(jì)

基于FPGA的卷積碼譯碼器的方案

在FPGA上實(shí)現(xiàn)咬尾卷積碼的最優(yōu)算法設(shè)計(jì)

評論