引言

電磁干擾問題通常由于電路中表現不明顯的耦合路徑弄得很復雜,其明確而有效地解決方法一般都依賴于工程師的經驗或建立在經典模型上的數模仿真。令工程師們高興的是,如果所有的非接觸電磁干擾都能夠用傳統的集總元件建模,而這種模型可以與轉換電路圖表相結合來描繪全部傳導干擾和耦合干擾。這樣分析和預測就變得比較容易了。

集總元件電路模型適合分析和預測頻段在0~30 MHz的電磁干擾。在許多先前的研究和引出用于分析的所謂簡單模型過程中,了解重要的路徑通常至關重要。但是,在可能存在微小的耦合路徑的情況下,這些參數都很難獲得。為此,本文利用一種可用于分析所有容易產生非接觸電磁干擾的普通集總電路模型,來準確地分析平面型PCB EMI集成濾波器。由于該模型更接近真實情況,因此更能如實反應平面型PCB EMI集成濾波器的濾波性能。

傳統的分立元器件在低頻狀態下,往往作為理想器件(即當作純電阻、純電感、純電容)來考慮。但在較高頻率下,器件特性將遠遠偏離其理想特性,因此,就必須考慮高頻分布參數對器件特性的影響。EMI電源濾波器中的主要元器件是電感和電容,為此,本文主要討論電感和電容的高頻分布參數對其濾波性能的影響。

因為EMI濾波器主要用于濾除高頻噪聲和高頻干擾信號,而由于電容器電感器的等效寄生參數將嚴重影響電源濾波器的高頻性能,因此,提高EMI電源濾波器的高頻性能就應該重點提高EMI濾波器的高損耗,減小共模電感線圈的等效并聯電容,同時減小電容器的等效串聯電感。為了達到上述目的,本文提出了EMI電源濾波器的平面磁集成結構。

1 EMI電源濾波器的平面磁集成結構

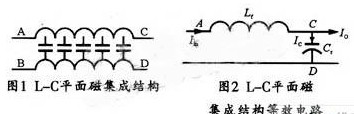

為了實現EMI電源濾波器的平面磁集成結構,這里引入了如圖1所示的L-C平面磁集成結構。

圖1中的這個結構是通過在平面絕緣板的兩面直接嵌入兩繞組導體而形成的,它通過控制繞組的連接點,使A、D為輸入點,C、D為輸出點。從而可等效得到如圖2所示的低通濾波器。

1.1 集成CM(共模)濾波器的實現

在共模勵磁下,EMI濾波器可以等效為兩個并聯的低通濾波器。因此,集成CM濾波器可以通過如圖3所示的兩個集成L-C繞組線圈來實現,兩個集成L-C繞組線圈都被連接成為低通濾波器形式,它們之間有很強的磁耦合。

1.2 集成DM(差模)濾波器的實現

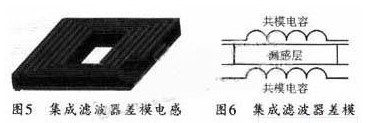

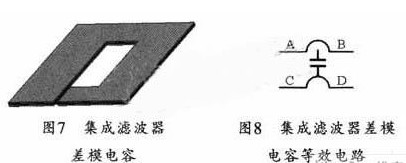

差模濾波器的等效電路是一個崩型低通濾波器,其濾波電感值很小。大約在10~20 μH范圍內,兩個濾波電容值較大,其值在0.1~1 μF范圍內。與分立EMI濾波器相同的是,在集成EMI濾波器中,差模電感也是利用集成CM扼流圈的漏感來實現的。在控制漏感值方面,平面CM扼流圈具有更多的靈活性,它可以在兩個繞組線圈中間插入一層額外的磁性材料。因此不需要改變CM電感器的匝數,這樣,漏感值就可以通過調整磁性材料的磁導率和有效面積來進行改變。這就給DM和CM電感器的解耦提供了一個機會。圖5所示是集成濾波器差模電感模型,圖6所示是集成濾波器差模電感的等效電路示意圖。

DM電容器可以用另一個連接成電容器的集成L-C繞組線圈來實現。它只有一匝或不到一匝,圖7和圖8所示分別是其差模電容及其等效電路。

圖9和10分別是平面型PCB EMI集成濾波器的二維結構和三維結構,該濾波器的所有參數都是通過該模型仿真得出的。

2 濾波器選材考慮

電源濾波器對高頻EMI信號的抑制比低頻EMI信號的消除容易得多,通常利用共模扼流圈的漏電感L所形成的差模電感就能消除0.3~30 MHz的傳導干擾電平。設計和選用濾波電感器一定要根據電路的實際需要而定。一般0.01~0.1 MHz范圍是差模干擾起主導作用.0.1~1 MHz范圍內則是差模與共模干擾聯合作用,而1~30 MHz范圍主要是共模干擾起作用。因此,對濾波電感的磁性能要求完全不同。對共模電感要選用相對磁導率較高的材料,一般相對磁導率要達到15000左右;而差模則可選用相對磁導率低一點的,一般10~100左右。由于共模電容的地是接在機殼上,為了安全,共模電容不能太大,同時要選用介電常數高一點的,以增強電容的耐壓能力。表1所列為不同物質的材料參數。

3 等效并聯電容的分析

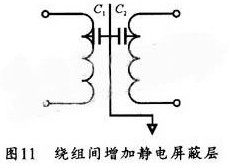

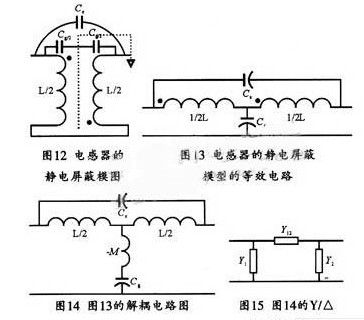

由于這種L-C平面磁集成結構的兩繞組靠得很近,因此,電網中的各種噪聲往往會通過它們之間的分布電容耦合進電路。解決這一問題的最好辦法是在初級和次級兩繞組間增加一個如圖11所示的靜電屏蔽層,其中C1和C2分別為初次級繞組與靜電屏蔽層之間的分布電容。

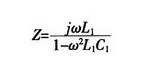

考慮到一個實際電感帶有的等效并聯寄生電容,其等效阻抗為:

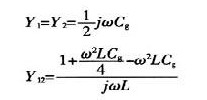

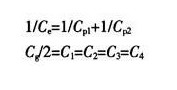

如果式(1)的分母中增加一項ω2L2C2(并且滿足ω2L2C2=ω2L1C1),那么有Z=jωL1,這樣就會變為理想的電感。基于這個想法,可以把一個電感器平分為兩部分,并且將其中點連接電容接地。其模型及等效電路分別如圖12和13所示。而將圖13分別進行解耦和Y/△變換,其得到的等效電路分別如圖14和15所示。且其變換參數為:

若令Gg=4Ce,Z12=1/Y12=jωL,這時電感將成為一個理想電感,繞組間的寄生耦合電容將減為零,可達到我們所期望的目標。附加電容Cg可以通過外加電容來實現,也可以利用繞組與地之間的寄生電容來實現。

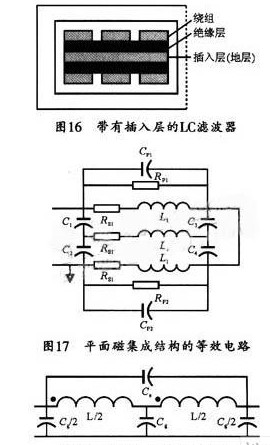

對于平面L-C磁集成結構,為得到期望的Gg,可在兩繞組間加入地層,其平面結構如圖16所示。設計時可采用:PlanaE43/10/28-3F和PLT43/28/4-3F3,繞組采用兩層,每層3匝。繞組寬度為2mm,絕緣層厚度為0.07 mm。其等效電路如圖17所示,若忽略繞組損耗和磁芯損耗,其中的L1、Cp1、Rp1t和Rs1分別為電感器第一半的電感和寄生參數;L2、Cp2、Rp2和Rs2分別為電感器另一半的參數;L3和Rs3為地層電感和電阻。忽略地層電阻時,其簡化電路如圖18所示。且有:

如果能滿足Cg=4Ce,那么,線圈繞組間的寄生電容就可以減少至零。

4 仿真驗證

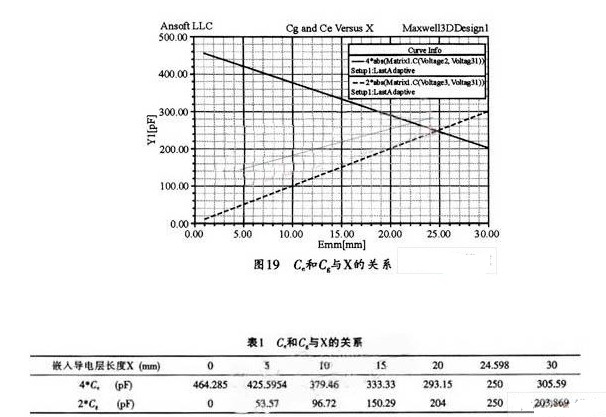

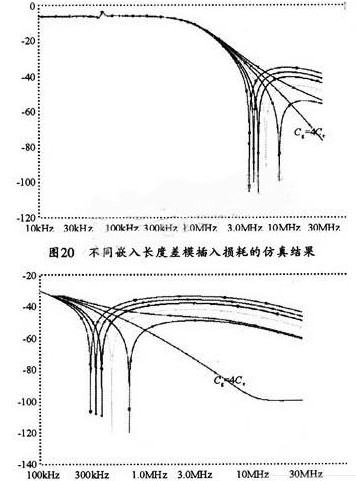

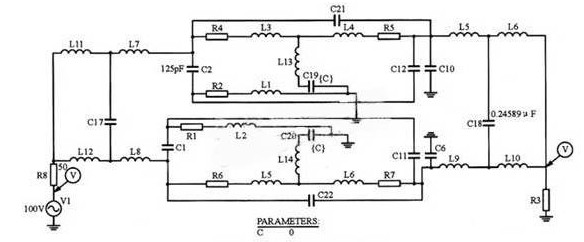

為了驗證插入導電層是否能改善濾波器的高頻性能,同時為了驗證Ce與Cg的關系,可尋找理想的嵌入導電層長Xo之后以X為變量,得出的仿真結果如圖19所示,然后再建立差模與共模仿真電路,并根據表1改變電容值Ce與Cg,所得出的差模插入損耗仿真結果如圖20所示,而其共模插入損耗仿真結果如圖21所示,圖22為其共模插入損耗的仿真電路。

根據仿真結果可以看出,隨著X不斷增大,諧振點頻率不斷增大,在X=24.89 mm時,差模插入損耗表示出理想的狀態。這時恰好Cg=4Ce。

5 結束語

仿真結果表明,嵌入導電層的濾波器可以去除EPC的影響,而且高頻性能良好。濾波器的插入損耗在30 MHz以上都能達到-60 dB,并且有進一步減小的趨勢。

-

濾波器

+關注

關注

161文章

7845瀏覽量

178394 -

emi

+關注

關注

53文章

3593瀏覽量

127824 -

電磁

+關注

關注

15文章

1137瀏覽量

51871

發布評論請先 登錄

相關推薦

平面磁集成EMI濾波器的非接觸電磁干擾對濾波性能的影響

平面磁集成EMI濾波器的非接觸電磁干擾對濾波性能的影響

評論