引言

直接數字頻率合成技術(Direct Digital FrequencySynthesis ,DDS)是從相位概念出發直接合成所需波形的一種新的頻率合成技術。DDS 技術具有相對帶寬寬、頻率轉換時間短、頻率分辨率高等優點,廣泛用于高精度頻率合成和任意信號發生。本文采用單片機控制DDS芯片,設計實現了一種高精度多波形的信號源。

1 DDS原理

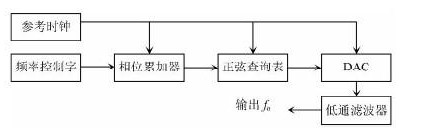

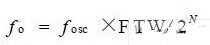

DDS的基本結構包括:相位累加器、正弦查詢表、數模轉換器(DAC)及低通濾波器等。DDS 原理如圖1所示。

圖1 中信號輸出頻率和參考時鐘頻率的關系表達式為:

其中:fo為輸出頻率, fosc為參考時鐘頻率,FTW為頻率控制字,N為頻率控制字的位數。由于N是一個固定值,那么只要改變FTW的大小就能得到所需要的頻率值,而且頻率的分辨率由N值決定,當N 值越大則分辨率越高。由Nyquist 取樣定理可知,要恢復理想波形,在理想低通濾波器的條件下,輸出頻率必須小于時鐘參考頻率的用50% ,即fo<1/2fosc,若超過這個范圍,則一階鏡像頻率就會落在Nyquist 帶寬內。而實際的LPF都有一個過渡帶的問題,所以為了更好地去除一階鏡像帶來的雜散,一般將DDS 的輸出頻率限制在014fosc內。可見當AD9852 參考時鐘頻率為時,完全可以滿足輸出頻率為50 MHz的設計要求。

2 系統設計

2.1 硬件設計

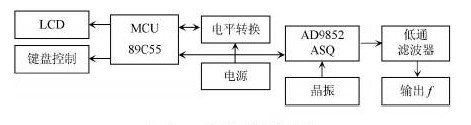

系統設計原理如圖2 所示。

該設計選用單片機作為控制核心,其與DDS 芯片AD9852之間采用并口通信方式。單片機P1口作為LCD 液晶顯示的數據總線,P0口用于AD9852地址總線和并口傳輸的數據總線,使用鎖存器74ALS573 實現P0口復用,74ALS573鎖存輸出的六位數值為AD9852 內部寄存器的地址。P2和P3口作為控制口用于鍵盤芯片和AD9852 的控制。

由于AD9852 使用CMOS 工藝, 供電電壓是而單片機使用的是TLL 電平,所以要在電路與CMOS 電路之間進行電平轉換。該系統選擇了作為5 V 邏輯電平到313 V 邏輯電平的轉換器件。所需要輸出的頻率可通過按鍵設定得到,進行的操作同時在液晶上進行顯示。AD9852 內部系統時鐘頻率由外部有源晶振倍頻得到。

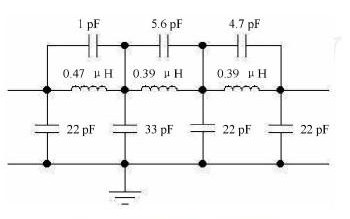

由于AD9852 的內部沒有低通濾波器,因此經過內部余弦DAC 輸出的掃頻信號不可避免地含有高頻噪聲,所以信號輸出端口需外接低通濾波器抑制高頻干擾。該設計采用七階橢園函數濾波器。七階橢圓濾波器電路圖如圖3 所示。

2.2 軟件設計

軟件設計主要分為菜單操作和頻率控制值計算兩部分。不同的按鍵代表著不同的數字和功能,除了正常的10個數字鍵0~9外,為了方便頻率值輸入,還設計了左右移動鍵、刪除鍵、Outp ut 確認輸出鍵等功能鍵。

相應的數值如頻率、相位、幅度輸入完成后按輸出鍵,即產生相應的信號輸出。

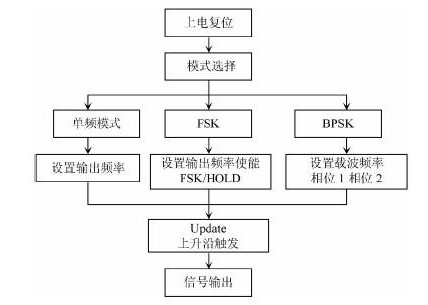

整體軟件設計流程圖如圖4 所示。

2.3 48b頻率控制字的處理

由于單片機C 語言中數據運算最多為32b ,如單精度Float 型、Long長整型,而Double雖是64b,但編譯時出錯故將介紹一種在單片機中計算頻率控制字的方法。

在該設計中取參考時鐘頻率fosc為300MHz ,在的原理中介紹了輸出頻率的計算方法為:

在計算頻率控制字時采用分割法,通過所需輸出頻率高低來分割,并引入了臨界頻率fL的概念。

首先將48b頻率控制字分割成16b+32b,使前面的16b都為0,則FTW=232時的fo為臨界頻率其值為當fo≤fL1時,頻率控制字計算公式為當fo>fL1時,通過把48b頻率控制字分成令最前面的8b和最后面的8b 等于0 ,引入臨界頻率fL2,可由算式(1)計算得到當fL1

3 結語

針對目前市場上的函數發生器存在的頻帶范圍窄、精度不高、準確度低、頻譜純度差等缺點,設計了一款高精度高頻數控函數信號發生器,該函數發生器具有頻帶范圍寬、精度高、頻譜純度好、頻率輸出穩定等優點。經測試頻率范圍可以達到50 MHz , 頻率分辨率為并可以產生正弦波、FSK與BPSK 波形。可應用于日常教學與科研工作中,在晶體濾波器測試、復雜通信系統測試、音頻系統測試、高性能視頻測試等領域有廣泛的應用前景。

-

濾波器

+關注

關注

161文章

7846瀏覽量

178411 -

DDS

+關注

關注

21文章

634瀏覽量

152734 -

數模轉換器

+關注

關注

14文章

1016瀏覽量

83252 -

信號發生器

+關注

關注

28文章

1478瀏覽量

108838

發布評論請先 登錄

相關推薦

采用頻率合成技術實現高精度高頻數控函數信號發生器的設計

采用頻率合成技術實現高精度高頻數控函數信號發生器的設計

評論