隨著嵌入式系統與外圍環境的響應越來越多,嵌入式系統是“控制、監視或者輔助裝置、機器和設備運行的裝置”(devices used to control, monitor, or assist the operation of equipment, machinery or plants)。從中可以看出嵌入式系統是軟件和硬件的綜合體,還可以涵蓋機械等附屬裝置。目前國內一個普遍被認同的定義是:以應用為中心、以計算機技術為基礎、軟件硬件可裁剪、適應應用系統對功能、可靠性、成本、體積、功耗嚴格要求的專用計算機系統。微控制器(Microcontroller Unit,即MCU)可從不同方面進行分類:根據數據總線寬度可分為8位、16位和32位機;根據存儲器結構可分為Harvard結構和Von Neumann結構;根據內嵌程序存儲器的類別可分為OTP、掩膜、EPROM/EEPROM和閃存Flash;根據指令結構又可分為CISC(Complex Instruction Set Computer)和RISC(Reduced Instruction Set Computer)微控制器。

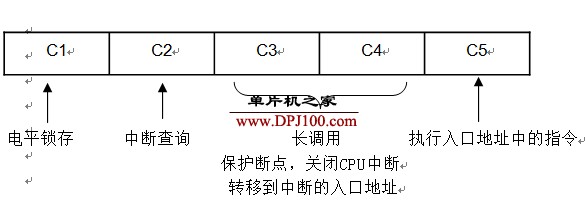

一般來說,CPU負責處理中斷和移動數據。在某些應用中,CPU的大多數時間都花費在這些活動上。要應對這些額外的計算負荷,就必須提高CPU時鐘速率,因而相應地增加了功耗。在極端情況下,還必須把設計從8/16位器件轉換成32位器件才能應付。

在多數情況下,一個外設上的信號除了要讓另一個外設知道它有事要做外,兩個外設間的聯絡卻需要大量中斷處理時間。CPU便會隨之中斷,并關斷馬達驅動電路的PWM輸出。這個過程需要耗費數十個時鐘周期,并需要另外的20~100個時鐘周期來恢復關聯。微控制器并沒真正被用于任何需要其處理能力的事情,只是從模擬比較器向PWM輸出傳遞了一個消息而已。

如果這些外設能夠無需中斷CPU而直接相互通信,每秒鐘就可輕易節省數百萬個時鐘周期。8位微控制器不再適用于8位應用的一個原因,就是應用涉及的數據處理和中斷處理太多,CPU的MIPS大都耗費在這些活動上。而外設和內存之間的傳輸數據更進一步地增加了MCU的負擔。一個350kps的數據傳輸就要耗費22~25個CPU MIPS。

解決這個問題的一個方法是采用一個帶8通道事件系統和直接內存訪問(DMA)的低功耗8/16位單周期RISC MCU,讓事件系統和DMA來為CPU分擔這些工作。DMA(Direct Memory Access,直接內存存取) 是所有現代電腦的重要特色,他允許不同速度的硬件裝置來溝通,而不需要依于 CPU 的大量 中斷 負載。否則,CPU 需要從 把每一片段的資料復制到 暫存器,然后把他們再次寫回到新的地方。在這個時間中,CPU 對于其他的工作來說就無法使用。 DMA 傳輸重要地將一個內存區從一個裝置復制到另外一個。當 CPU 初始化這個傳輸動作,傳輸動作本身是由 DMA 控制器 來實行和完成。典型的例子就是移動一個外部內存的區塊到芯片內部更快的內存區。像是這樣的操作并沒有讓處理器工作拖延,反而可以被重新排程去處理其他的工作。DMA 傳輸對于高效能 嵌入式系統 算法和網絡是很重要的。

在實現DMA傳輸時,是由DMA控制器直接掌管總線,因此,存在著一個總線控制權轉移問題。即DMA傳輸前,CPU要把總線控制權交給DMA控制器,而在結束DMA傳輸后,DMA控制器應立即把總線控制權再交回給CPU。

事件系統通過CPU數據總線和DMA控制器之外的一個專用網絡傳遞外設信號。有了事件系統,當一個外設出現了狀態變化,就會自動觸發其它外設上的相應動作。在前述馬達案例中,微控制器中的模擬比較器、定時器/計數器,I/O引腳或ADC可以在過流狀況的兩個時鐘周期內,直接關斷馬達驅動電路的PWM輸出,不需占用任何中斷,也不耗費任何CPU時鐘資源,就可以為馬達提供更好的保護。

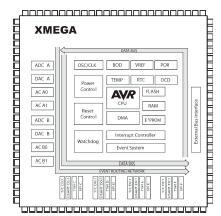

圖1,帶有事件系統總線的XMEGA微控制器:帶有事件系統和DMA的MCU通過CPU數據總線和DMA之外的一個專用網絡傳遞外設信號。這樣做的好處是外設間信號通信變成可預見和無延遲,并減少了CPU周期時間和釋放了中斷資源。

圖1,帶有事件系統總線的XMEGA微控制器。

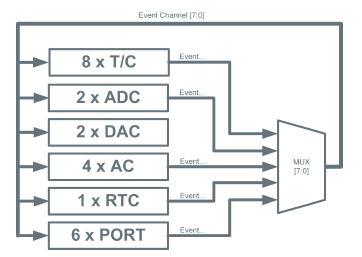

可以觸發事件系統的外設事件包括:定時器/計數器比較匹配或溢出,模擬比較器觸發,引腳狀態變化,ADC完成或比較,以及實時計數器溢出。在其它外設中被觸發的事件包括:ADC或 DAC轉換,輸入捕獲以記錄通信時間戳或ADC測量時間戳,外部頻率或脈寬測量,產生定時器/計數器時鐘信號,開始一個DMA交易,或改變一個引腳輸出。

采用事件系統能夠消除多個和/或頻繁的中斷觸發造成的瓶頸,而且無需軟件開銷,關鍵任務可獨立于CPU完成,而且也能大大降低功耗。一個沒有事件系統的傳統8位MCU要耗費16 MIPS才能完成響應馬達過流信號關斷PWM的動作。在16 MHz,1 MIPS/MHz,以及0.6 mA/MHz的工作條件下,微控制器需要消耗8.6 mA才能完成這項任務。而一個帶有事件系統的同等MCU則不消耗MIPS,而且也不會增加功耗。

圖2,XMEGA微控制器的事件系統:有了事件系統,一個外設上出現狀態變化就會自動觸發其它外設上的相應動作,且不 占用任何中斷,也不耗費任何CPU時鐘資源。可同時處理多達8個外設間事件,以及4個速率為64Mps的數據傳輸,而CPU處于睡眠模式,電流消耗僅10mA。

圖2,XMEGA微控制器的事件系統。

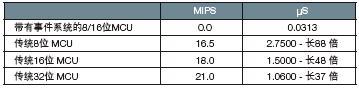

消除中斷后,處理響應延遲可獲減少,而且確保最多只要2個時鐘周期,或者說在32 MHz 時鐘頻率下只需62.5 ns的時間;而最快響應時間可達到31.2 ns。實際上,在8/16位MCU上采用事件系統,響應時間較無事件系統的傳統32位MCU 縮短了37倍。

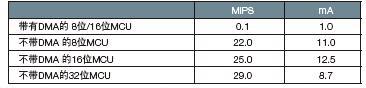

傳輸數據是另一個耗費時鐘周期和增加功耗的活動。由于CPU本身每次只能傳輸1個位,因此用CPU傳輸數據會帶來巨大處理開銷很大。8位微控制器必須執行22 MIPS,消耗14mA電流才能完成速率350Kbps的數據傳輸。

只要在器件上增加一個外設DMA控制器,就可基本上解除CPU的所有這些工作負荷。當CPU數據總線空閑時,DMA控制器便會用它來完成內存和外設間的數據傳輸,無需使用CPU資源。連接外設寄存器的內部總線是分開的,因而DMA控制器和CPU可以同時進行總線訪問。

跟處理能力為22 MIPS、功耗為11mA但不帶DMA的8位MCU比較,使用DMA控制器傳輸350 Kbps數據,MIPS消耗可減少99%;電流消耗則低于1mA。

DMA控制器可以直接將數據從一個外設寄存器移到內部或外部SRAM,也可在SRAM的不同地址間,甚至不同外設寄存器之間移動數據。4個DMA通道有著各自的優先級、、目的地、觸發方式、尋址模式,以及傳輸塊大小。由于RISC CPU中簡單的線性內存地址空間以及DMA控制器的自動增/減和重新加載的特點,DMA一次可傳送1到16M字節。

若事件系統與DMA控制器配合使用,就可按如下方式完成模數和數模轉換:任何I/O引腳上的狀態變化或任何定時器/計數器出現溢出,就會觸發ADC轉換,無需任何CPU開銷。ADC轉換結果通過一個DMA通道傳送到SRAM。同時,第二個定時器/計數器會觸發一個高速DAC轉換,并用第二個DMA通道傳輸相應的數據。事件系統會讓模擬比較器觸發輸入捕捉,以100%精度記錄時間戳,觸發自動捕獲,記錄通信交易的起始時間戳,或在第二個ADC上掃描ADC轉換。4個事件通道仍是可使用的,它們可用于PWM輸出的故障保護,控制一個高壓驅動級、定時器/計數器的級聯,以及兩個通信通道,所有動作均在同時進行,而CPU則處于睡眠狀態。

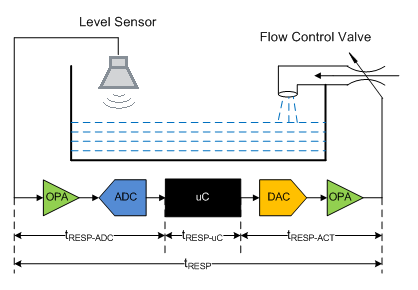

圖3,XMEGA的事件處理:若事件系統與DMA控制器配合使用,就可按如下方式完成模數和數模轉換:任何I/O引腳上的狀態變化或任何定時器/計數器出現溢出,就會觸發ADC轉換,無需任何CPU開銷。ADC轉換結果通過一個DMA通道傳送到SRAM。

圖3,XMEGA的事件處理

在微控制器中增加事件系統和DMA對功耗有很大改善。在某些應用中,這樣做可使MCU在大多數時間都處于睡眠模式,功率消耗僅80 uA/MHz,而所有的外設卻仍繼續工作。對一個有8個同時事件和4個350 Kbps數據傳輸的應用而言,一個帶有事件系統和DMA的8/16位MCU,每秒將有3160萬個周期處于睡眠模式,而總電流消耗僅4mA。任何不帶事件系統和DMA的8/16位MCU則會消耗52 至 60 mA的電流。而一個32位MCU則會消耗34.8 mA的電流,幾乎是帶有事件系統和DMA處理器的10倍功耗。

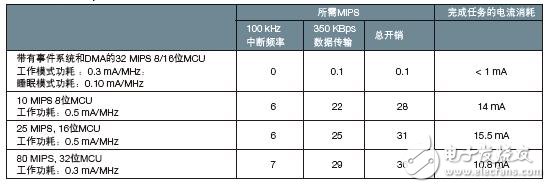

有/無事件系統和DMA之MCU的處理周期和功耗比較見表3。

表1,有/無事件系統之MCU的處理周期和響應時間比較

表2,有/無DMA的MCU傳輸350 KBps數據時的典型MIPS和功耗

表3,傳輸350Kbps 數據的中斷、MIPS和功耗比較

-

嵌入式

+關注

關注

5091文章

19176瀏覽量

307202 -

存儲器

+關注

關注

38文章

7528瀏覽量

164253 -

cpu

+關注

關注

68文章

10901瀏覽量

212813 -

低功耗

+關注

關注

10文章

2418瀏覽量

103865

發布評論請先 登錄

相關推薦

討論SAR DAC響應時間和幾種實現設計

產品響應時間

SAR ADC響應時間實現迅速響應、快速控制的方法

紫外火焰探測器響應時間測試系統的研究

ADIS16365 慣性傳感器,具有更快響應時間和更低功耗

什么是液晶電視的響應時間

光敏電阻響應時間研究

什么是單片機的中斷響應時間

實現響應時間和低功耗的事件系統的研究分析

實現響應時間和低功耗的事件系統的研究分析

評論