引言

同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器(SDRAM),在同一個(gè)CPU時(shí)鐘周期內(nèi)即可完成數(shù)據(jù)的訪問(wèn)和刷新,其數(shù)據(jù)傳輸速度遠(yuǎn)遠(yuǎn)大于傳統(tǒng)的數(shù)據(jù)存儲(chǔ)器(DRAM),被廣泛的應(yīng)用于高速數(shù)據(jù)傳輸系統(tǒng)中。基于FPGA的SDRAM控制器,以其可靠性高、可移植性強(qiáng)、易于集成的特點(diǎn),已逐漸取代了以往的專用控制器芯片而成為主流解決方案。然而,SDRAM復(fù)雜的控制邏輯和要求嚴(yán)格的時(shí)序,成為開(kāi)發(fā)過(guò)程中困擾設(shè)計(jì)人員主要因素,進(jìn)而降低了開(kāi)發(fā)速度,而且大多數(shù)的基于FPGA的SDRAM控制器都是針對(duì)特定的SDRAM芯片進(jìn)行設(shè)計(jì),無(wú)法實(shí)現(xiàn)控制器的通用性。本文介紹一種通用SDRAM控制器的FPGA模塊化解決方案。

SDRAM及其控制過(guò)程

SDRAM控制邏輯復(fù)雜,命令種類(lèi)多樣,需要周期性刷新操作、行列管理的等多重操作。

SDRAM首先要進(jìn)行初始化操作。在上電后等待100ns,至少執(zhí)行1條空操作,然后對(duì)所有頁(yè)執(zhí)行預(yù)充電操作,接著向各頁(yè)發(fā)出兩條刷新操作指令,最后執(zhí)行SDRAM工作模式的設(shè)定LMR命令用來(lái)配置SDRAM工作模式寄存器。SDRAM工作寄存器可以根據(jù)具體應(yīng)用的需要進(jìn)行設(shè)置。

初始后的SDRAM在得到了RAS、CAS、WE的值后開(kāi)始執(zhí)行相應(yīng)的命令。在對(duì)SDRAM進(jìn)行讀、寫(xiě)過(guò)程中,必須要先進(jìn)行頁(yè)激活ACT操作,保證存儲(chǔ)單元是打開(kāi)的,以便從中讀取地址或者寫(xiě)入地址,然后通過(guò)預(yù)充電PHC命令實(shí)現(xiàn)來(lái)關(guān)閉存儲(chǔ)單元。在進(jìn)行寫(xiě)操作時(shí),內(nèi)部的列地址和數(shù)據(jù)都會(huì)被寄存,而進(jìn)行讀操作時(shí),內(nèi)部地址被寄存,數(shù)據(jù)的存儲(chǔ)則發(fā)生在CAS 延遲時(shí)間(通常為1~3個(gè)時(shí)鐘周期)后。最后,操作終止:當(dāng)SDRAM順次的進(jìn)行讀、寫(xiě)操作后,當(dāng)?shù)竭_(dá)到突發(fā)長(zhǎng)度或者突發(fā)終止指令BT出現(xiàn)時(shí),SDRAM將終止其操作。

模塊化的SDRAM控制器設(shè)計(jì)

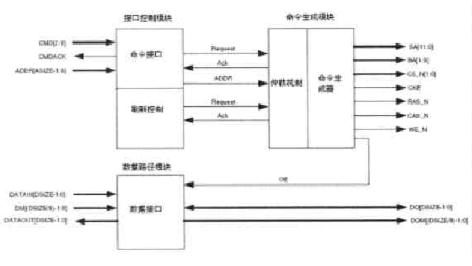

在SDRAM控制器的FPGA實(shí)現(xiàn)方案中,采用了FPGA的自底向上的模塊化設(shè)計(jì)思想,首先分析頂層模塊的功能,再將其功能分類(lèi)細(xì)化,分配到不同的子模塊去實(shí)現(xiàn),然后自底向上的先逐步完成各個(gè)子模塊的設(shè)計(jì),最后將子模塊相互連接生成頂層模塊。經(jīng)過(guò)分析,SDRAM控制器應(yīng)實(shí)現(xiàn)的功能有:為SDRAM提供刷新控制以保持SDRAM中的數(shù)據(jù);對(duì)主機(jī)的命令進(jìn)行仲裁,將下一步要執(zhí)行的命令翻譯成可與SDRAM連接的信號(hào);為SDRAM的讀、寫(xiě)生成數(shù)據(jù)路徑。因此,根據(jù)SDRAM的指令操作特點(diǎn)將SDRAM控制器劃分為接口控制模塊、命令生成模塊和數(shù)據(jù)路徑模塊三個(gè)主要模塊(圖1)。

圖1 SDRAM控制器的FPGA模塊化設(shè)計(jì)方案

下面,對(duì)其接口信號(hào)進(jìn)行介紹,需要注意的是,為了實(shí)現(xiàn)該控制器的通用性,ADDR、DATAIN、DATAOUT、DQ、DOM信號(hào)設(shè)計(jì)成可根據(jù)SDRAM的容量改變的形式。

與主機(jī)接口信號(hào):CLK(系統(tǒng)時(shí)鐘);RESET(系統(tǒng)復(fù)位);CMD[2:0](譯碼指令);CMDACK(指令應(yīng)答信號(hào));ADDR[ASIZE-1:0](地址線);DATAIN/DATAOU[DSIZE-1:0](輸入、輸出數(shù)據(jù)總線);DM[(DSIZE/8)-1:0](數(shù)據(jù)掩碼)。

與SDRAM接口信號(hào):SA(地址線);BA(頁(yè)地址);CS_N(片選信號(hào));CKE(時(shí)鐘使能信號(hào));RAS、CAS、WE(命令控制信號(hào));DQM[(DSIZE/8)-1:0](SDRAM數(shù)據(jù)掩碼);DQ[DSIZE-1:0](雙向數(shù)據(jù)線)。

各個(gè)模塊的設(shè)計(jì)與實(shí)現(xiàn)

接口控制模塊

接口控制模塊主要實(shí)現(xiàn)的功能是將CMD[2:0]翻譯成接口指令和對(duì)刷新計(jì)數(shù)器的控制指令。接口模塊在工作過(guò)程中首先通過(guò)要通過(guò)狀態(tài)機(jī)來(lái)完成對(duì)CMD[2:0]的翻譯。在VHDL程序中聲明一個(gè)用戶自定義類(lèi)型states,根據(jù)CMD[2:0]輸入來(lái)決定狀態(tài)的轉(zhuǎn)移,完成對(duì)CMD[2:0]的解碼,部分代碼如下:

type states is(nop,reada,writea,refresh,

precharge,load_mode);

signal state : states ;

………………

case cmd is

when “011” =》 state《=refresh;

when “111” =》 state《=nop;

………………

另外,SDRAM需要周期性刷新操作以保持?jǐn)?shù)據(jù)。在模塊的程序設(shè)計(jì)中,刷新周期的控制通過(guò)一個(gè)計(jì)數(shù)器來(lái)完成,到達(dá)規(guī)定的計(jì)數(shù)周期數(shù)時(shí),接口模塊通過(guò)REF_REQ信號(hào)向SDRAM發(fā)出刷新請(qǐng)求。直到SDRAM完成刷新操作,發(fā)出REF_ACK刷新應(yīng)答信號(hào),計(jì)數(shù)器才重新賦值,開(kāi)始下一次的計(jì)數(shù)。

命令生成模塊

命令生成模塊實(shí)現(xiàn)對(duì)輸入的SDRAM指令請(qǐng)求進(jìn)行仲裁判斷的功能,并將仲裁后要執(zhí)行的指令解碼成SDRAM需要的RAS、CAS等信號(hào),從而實(shí)現(xiàn)指令對(duì)SDRAM的控制。仲裁機(jī)制是SDRAM控制器設(shè)計(jì)不可或缺的一個(gè)環(huán)節(jié)。仲裁機(jī)制實(shí)現(xiàn)要遵循如下規(guī)則:

*SDRAM在每一刻只有一個(gè)指令在執(zhí)行;

*先到的指令先執(zhí)行,如果刷新請(qǐng)求到來(lái)時(shí),其它命令正在執(zhí)行中,要等到當(dāng)前命令執(zhí)行完成后,才能執(zhí)行刷新指令;

*其它指令和刷新請(qǐng)求同時(shí)到來(lái)時(shí)刷新操作先執(zhí)行。

經(jīng)過(guò)仲裁判斷后,指令將傳入命令生成器。命令生成器不僅要把指令解碼成SDRAM需要的RAS、CAS等信號(hào),同時(shí)還要對(duì)命令執(zhí)行的時(shí)間進(jìn)行控制。下面的例程僅供參考。

if (do_state=refresh or do_state=reada or

do_state=writea

or do_state=precharge or

do_state=load_mode)then

command_delay(7 downto

0)《=“11111111”;

------移位寄存器初值

command_done《=‘1’;

………………

else

command_done《=command_delay(0);

移位操作

command_delay(6 downto 0)《=

command_delay(7 downto 1);

command_delay(7)《=‘0’;

end if;

下面介紹輸入的指令為writea和reada指令時(shí)模塊所進(jìn)行的操作。當(dāng)SDRAM的writea和reada指令到來(lái)時(shí),將引發(fā)一系列指令的執(zhí)行,和其它指令相比需要更多的附加時(shí)間。所以,在這種情況下需要聲明第二個(gè)移位寄存器rw_shift來(lái)完成這兩個(gè)指令的附加時(shí)間的實(shí)現(xiàn)。rw_shift的工作原理和第一個(gè)移位寄存器command_delay是一樣的,需根據(jù)讀、寫(xiě)的時(shí)間決定rw_shift的位數(shù)。

最后一個(gè)移位寄存器oe_shift用來(lái)為數(shù)據(jù)通道生成數(shù)據(jù)輸入、輸出使能信號(hào)oe。對(duì)于非頁(yè)模式的讀寫(xiě)來(lái)說(shuō),oe保持有效的時(shí)間取決于突發(fā)長(zhǎng)度,需要注意的是,讀操作時(shí),oe有效的起始時(shí)間取決于CAS延時(shí)時(shí)間,而對(duì)于寫(xiě)操作,則在寫(xiě)指令開(kāi)始時(shí)oe就是有效的。

數(shù)據(jù)路徑模塊

數(shù)據(jù)路徑模塊的作用是在writea和reada命令期間生成數(shù)據(jù)的路徑。在用VHDL語(yǔ)言程序中,用簡(jiǎn)單的賦值語(yǔ)句就可以實(shí)現(xiàn)數(shù)據(jù)路徑模塊。

通用性的實(shí)現(xiàn)

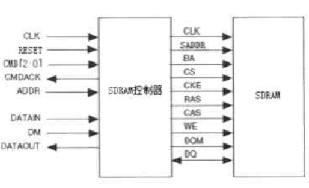

根據(jù)SDRAM控制器的FPGA模塊化設(shè)計(jì)方案生成的FPGA控制器易于修改和擴(kuò)展,具有可通用的特性。在具體的應(yīng)用中,針對(duì)不同的SDRAM,并不需要更改SDRAM控制器結(jié)構(gòu),只要根據(jù)datasheet中的SDRAM的容量將地址線數(shù)和數(shù)據(jù)的位數(shù)做相應(yīng)修改,再依據(jù)SDRAM的時(shí)序和讀、寫(xiě)速度更改接口控制模塊中的時(shí)間信號(hào)的周期,如刷新周期、命令生成模塊中移位寄存器的位數(shù)和初值等,這樣就可以對(duì)不同的SDRAM進(jìn)行控制。最后,生成的SDRAM控制器頂層模塊如圖2所示。為了證明該控制器設(shè)計(jì)方案的可行性和通用性,在Altera公司的Cyclone系列FPGA——EP1C6Q240C8中生成SDRAM控制器,根據(jù)數(shù)據(jù)手冊(cè)中SDRAM的參數(shù)對(duì)控制器各模塊的VHDL語(yǔ)言程序做相應(yīng)的改動(dòng),實(shí)現(xiàn)了對(duì)三星公司的8MByte SDRAM K4S641632E和2MByte SDRAM K4S161622D的控制,均達(dá)到了100MHz的讀、寫(xiě)速度。

圖2 SDRAM控制器接口

結(jié)語(yǔ)

本方案采用的模塊化思想為SDRAM控制器的開(kāi)發(fā)提供了一種層次分明、易于擴(kuò)展的設(shè)計(jì)思路。實(shí)驗(yàn)結(jié)果表明,該控制器設(shè)計(jì)緊湊,維護(hù)升級(jí)方便,易于實(shí)現(xiàn)對(duì)SDRAM的通用化控制,這無(wú)疑將極大的提高SDRAM應(yīng)用的開(kāi)發(fā)速度。

責(zé)任編輯:gt

-

控制器

+關(guān)注

關(guān)注

112文章

16433瀏覽量

178950 -

SDRAM

+關(guān)注

關(guān)注

7文章

430瀏覽量

55307 -

FPG

+關(guān)注

關(guān)注

1文章

54瀏覽量

80010

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SDRAM控制器實(shí)現(xiàn)FPGA模塊化和通用性的設(shè)計(jì)方案

如何使用Verilog實(shí)現(xiàn)基于FPGA的SDRAM控制器?

SDRAM控制器的設(shè)備與VHDL實(shí)現(xiàn)

使用Verilog實(shí)現(xiàn)基于FPGA的SDRAM控制器

基于FPGA的FIFO設(shè)計(jì)和應(yīng)用

SDRAM控制器的設(shè)計(jì)

FPGA讀寫(xiě)SDRAM的實(shí)例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計(jì)論文

DDR SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)

基于SDRAM控制器軟核的Verilog設(shè)計(jì)

基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)簡(jiǎn)介

基于FPGA的SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)簡(jiǎn)介

基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)

基于SDRAM控制器實(shí)現(xiàn)FPGA模塊化和通用性的解決方案設(shè)計(jì)

基于SDRAM控制器實(shí)現(xiàn)FPGA模塊化和通用性的解決方案設(shè)計(jì)

評(píng)論