TigerSHARC系列處理器是ADI公司推出的高性能數字信號處理器,包含ADSP TS101、ADSP TS201、ADSP TS202、ADSP TS203。TigerSHARC系列處理器的link 口為處理器提供了快速、獨立的通信機制。link口的特點是點對點通信、協議比較簡單、數據率較高,因而可以通過link口實現多片處理器構成處理器系統。

TS101的link口和TS20X系列處理器的link口有所不同。TS101的link口采用8位雙向數據線和三根控制線構成,采用TS101 link協議可實現雙工通信;而TS20X系列處理器的link口采用LVDS技術(4 bit收、4 bit發),實現全雙工通信。

盡管TS101的link口和TS20X的link口在物理和協議方面都不一樣,但在應用上都可以實現數據的通信以及處理器的加載功能。

1 信號處理系統結構

典型的采用TigerSHARC處理器的信號處理板連接方式為:板(簇)內采用CLUSTER總線實現處理器連接,板間采用link口實現處理器連接。

采用FPGA實現與TigerSHARC處理器link口的連接可提高信號處理系統與其他系統連接的靈活性。FPGA通過link口與信號處理系統連接,簡化了信號處理板卡的設計;同時由于FPGA靈活性及豐富的接口資源,可以很方便實現與其他系統的連接。

采用FPGA加載信號處理系統,只需修改與FPGA連接的Flash中的程序就可以實現配置信號處理器系統中各處理器的程序。在加載完后,FPGA還可以作為信號處理系統的接口板,使系統設計更加簡單、高效。

本文介紹一種基于FPGA通過link口加載由TS101構成的信號處理系統的方法。

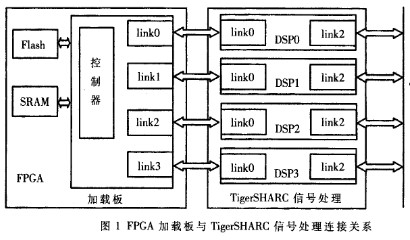

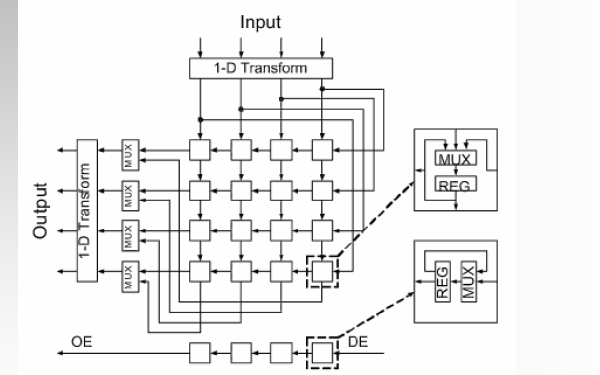

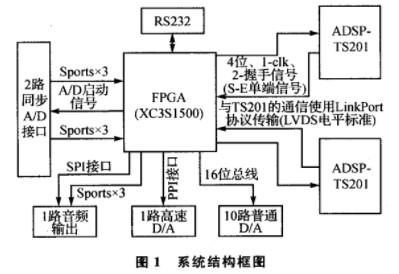

FPGA加載板和TigerSHARC信號處理系統連接關系如圖1所示。

加載板采用EP2S60芯片作為處理器,外接128 MB Flash和36 MB SRAM。Flash用于存儲處理器的加載程序,SRAM作為緩存。FPGA的4個link分別與TigerSHARC信號處理板上4個DSP的link0相連,信號處理板上4個DSP的link2分別與下一個信號處理器的4個DSP的link0相連。采用這種方法連接多塊信號處理板構成一個信號處理系統。

TigerSHARC處理器每個link口都可以作為加載的端口,只需在Kernel程序中將LINK號改成對應的link口。

2 加載文件結構

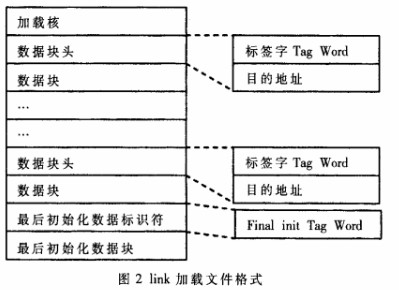

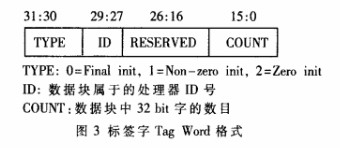

TigerSHARC處理器link口加載文件結構如圖2所示。加載文件由加載核、若干Zero init或Non-zero init加載數據塊及Final init數據塊構成。加載核沒有數據塊頭信息,Zero init 和Non-zero init數據塊頭都有1個標簽字和1個目的地址,Final init數據塊只有1個標簽字。標簽字各數據位的意義如圖3所示。由于link口的連接特點,link加載核不支持多處理器加載,因而link加載方式中不使用ID。標簽字的TYPE和COUNT指示了該塊數據的類型和長度。TigerSHARC加載文件以32 bit word為單位構成(本文的word即指32 bit word)。

3 加載狀態機的設計與實現

由于Flash的讀寫周期較長,設計中采用系統時鐘16分頻作為FPGA中Flash控制器的時鐘。直接從Flash中讀取數據無法保證DSP加載核(BOOT Loader Kernel)對程序數據的數據率要求,因而在設計中先將Flash中的數據轉存到與FPGA相連的SRAM中。SRAM讀出數據為32 bit,讀寫SRAM的數據率可以大大超過link口的吞吐率。FPGA中開辟2塊RAM作為乒、乓RAM緩存從SRAM中讀取數據,以保證FPGA發送link的數據保持在就緒狀態,DSP加載核在任何時候取數,FPGA link都能提供有效數據。

FPGA發送到link模塊的信號為TxWrite、TxData、TxBP。加載狀態機根據TxBP信號來判斷link口緩沖當前狀態是忙還是空閑,只要為空閑狀態就往link緩沖中寫數據,從而保證了DSP加載核總能獲取有效數據。

3.1 加載狀態機的設計

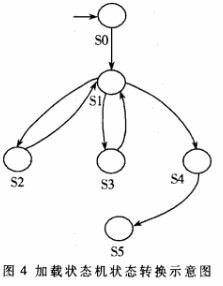

FPGA中加載有限狀態機狀態轉換示意圖如圖4所示。

狀態說明:

S0:BootLoader Kernel State;S1:數據塊類型判斷;S2:Non-zer init State;S3:Zero init State;S4:Final init State;S5:結束。

當需要加載時復位加載狀態機,在復位時設置計數器值。復位后,狀態機就進入了S0狀態。

S0狀態為發送DSP Boot Loader Kernel給需要加載的DSP,長度為256 words。在該狀態下,link口需要發送DSP Boot Loader Kernel給需要加載的DSP,數據發送完后(數據塊計數器count_packet為0),狀態轉入S1。

S1狀態為上一數據塊結束,下一數據塊將要開始發送的一個中間過渡狀態。在該狀態下判斷下一數據塊的類型,并計算下一數據塊的長度。根據標簽字Tag Word的TYPE值轉換到S2、S3、S4中的某個狀態。

當S1狀態下TYPE為1時,狀態機轉入S2。DSP收到這塊數據后,進入Non-zero init模式。S2狀態只需發送該數據塊,不需要對數據進行Non-zero init處理。該模式下,link口需要發送的數據為該數據塊標簽字的COUNT值加上數據塊頭的長度即2 words。該數據塊發送完后(數據塊計數器count_packet為0),狀態轉入S1。

當S1狀態下TYPE為2時,狀態機轉入S3。DSP收到這塊數據后,進入Zero init State模式。該模式下加載程序數據塊只有數據塊頭,即標簽字和目的地址2 words,后面即為下一個數據塊頭。此時,狀態機只需發送這個數據塊頭,不需要進行Zero init處理。該數據塊發送完后(數據塊計數器count_packet為0),狀態轉入S1。

當S1狀態下TYPE為0時,狀態機轉入S4。相應地,DSP進入到Final init模式,完成加載核的自我覆蓋。此時狀態機要發送的有效數據長度為257 words,即1 word Final init標簽字和256 words加載核自我覆蓋程序。當發送完Final init加載數據,有效的加載程序已經發送完。需要注意的是,加載核在取link口數據是啟動DMA傳輸的,而link口至內/外部存儲器的DMA是以4字組方式傳輸,因而當程序不是4字對齊時,發送的加載程序長度須以4字補齊。加載狀態機會根據加載文件自動完成4字補齊,發送的長度為將程序4字補齊后的長度,以滿足link口DMA的時序要求。

當S4狀態下數據塊計數器count_packet為0時,狀態機轉入S5,加載1個DSP結束。

當狀態機轉入S5時,FPGA 的加載狀態機已實現了通過link口對DSP的加載過程。為了實現信號處理系統中所有板卡的加載,第一塊信號處理板要完成對第二塊信號處理板卡的加載。link板卡的級聯關系見圖1,FPGA加載完第一塊板的DSP后,等待DSP運行起來,而后通過link口發送第二塊板的加載程序給第一塊板。第一塊板收到第二塊板的加載程序后,可以實現對第二塊板的加載。采用同樣的方法就可以實現級聯的每塊板卡的每個DSP的加載功能。

3.2 Signal Tap采集加載過程

采用Signal Tap采集加載開始、中間狀態轉換和加載結束的結果分別如圖5“7所示。圖中各信號的意義如下:

boot_dsp0_en、boot_dsp1_en:分別是加載第一塊信號處理板DSP0、DSP1的使能信號。

txdata、txwrite_ba_int、txbp:分別是link模塊控制端輸入數據、寫控制信號、緩沖滿信號count_packet的數據塊計數器。

TAG_COUNT、TAG_TYPE:分別是標簽字的COUNT和TYPE值。

STATE_FSM:狀態機的當前狀態。

rst_state:狀態機復位控制信號。

l0_lxdata、l0_lxclkout、l0_lxclkin:分別是FPGA的link0端口接口數據、時鐘/應答輸出、時鐘/應答輸入。

圖中采樣時鐘為link模塊輸入時鐘,1個周期link口發送1 B數據。由于狀態機采用的是邊發送link數據邊解譯加載數據的方法,因而狀態機狀態轉換過程要滯后發送數據4個周期(1 word),通過在發送DSP Boot Loader Kernel這個狀態計數值多4個字而在Final Init過程計數值少4個字來實現對齊。

圖5為加載開始,STATE_FSM狀態為0,此時FPGA發送DSP Boot Loader Kernel給TigerSHARC DSP。加載開始時計數值為0x403 bytes,共發送0x404 bytes數據。如前所述,在發送DSP Boot Loader Kernel時比其實際長度0x400 bytes多4 bytes。

圖6為加載中間加載過程,STATE_FSM狀態依次為3、1、3、1、2。當STATE_FSM為第一個1時,TAG_TYPE為2、TAG_COUNT為3,標志下一個狀態為Zero init State。此狀態下FPGA需要發送2 words, 因而count_packet為0x6(count_packet為0占了2個周期)。當STATE_FSM為第二個1時,TAG_TYPE為1、TAG_COUNT為4,標志下一個狀態為Non-zero init State,此狀態下FPGA需要發送4 words數據和2 words數據塊頭,因而從此時count_packet為0x16(count_packet為0占了2個周期)。

如圖7所示,當STATE_FSM為4且計數值為0時,STATE_FSM轉為5、boot_dsp0_en從1變為0,此時加載DSP0結束。DSP0加載結束后FPGA產生一個狀態復位信號rst_state使狀態機復位,而后boot_dsp1_en從0變為1,開始加載DSP1。采用同樣的方法就可以實現加載DSP2、DSP3。

本文介紹了一種采用FPGA加載TigerSHARC DSP的方法。在FPGA中設計的FSM可根據加載文件的結構自動實現加載功能,通過TigerSHARC DSP link互聯關系可實現對整個信號處理系統的加載。此外,還介紹了加載狀態機的設計方法,并采用Signal Tap采集加載狀態機幾個典型的加載過程,驗證了加載狀態機的設計。

-

處理器

+關注

關注

68文章

19293瀏覽量

229939 -

FPGA

+關注

關注

1629文章

21744瀏覽量

603608 -

數字信號處理

+關注

關注

15文章

560瀏覽量

45864

發布評論請先 登錄

相關推薦

基于FPGA控制的多DSP并行處理系統

基于FPGA 的交流信號采集與處理系統

6U VME TigerSHARC201&FPGA信號處理機-LT-TS201-FPGAT

基于FPGA的振動信號采集處理系統設計并實際驗證

FPGA視頻教程之使用FPGA進行嵌入式信號處理系統設計視頻資料免費下載

EE-200: ADSP-TS20x TigerSHARC?處理器的啟動加載內核運行

基于FPGA通過link口加載TigerSHARC信號處理系統的設計

基于FPGA通過link口加載TigerSHARC信號處理系統的設計

評論