在數字信號處理(DSP)領域,需要處理的數據量很大,并且實時性要求很高。傳統的DSP設計方法主要有采用固定功能的DSP器件和采用DSP處理器兩種,由于它們靈活性差以及軟件算法在執行時的順序性,限制了它們在高速和實時系統中的應用。隨著深亞微米半導體制造工藝的不斷創新,百萬門可編程器件的不斷推出,為DSP提供了第3種有效的解決方案,即利用FPGA實現DSP運算硬件化。它能夠在集成度、速度和系統功能方面滿足DSP應用的需要。

然而在應用FPGA進行系統設計綜合過程中,選擇芯片的運行速度優化和資源利用優化常常是相互矛盾的,對速度指標要求高的設計優化常常要占用較大的芯片資源,而減小芯片面積的設計又需要以降低系統速度為代價。從FPGA發展趨勢和DSP運算要求看,系統速度指標的意義比面積指標更趨重要,需要我們進一步深入研究提高芯片的最高工作速度的設計策略。本文討論在基于FPGA的DSP系統設計中采用流水線技術,充分利用硬件內部的并行性,在FPGA有限資源芯片面積上提高單位時間里的數據處理能力即數據吞吐率(throughput),提高系統的工作速度的具體做法。

流水線技術基本原理和FPGA結構特征

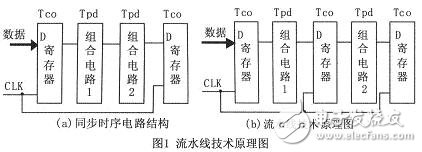

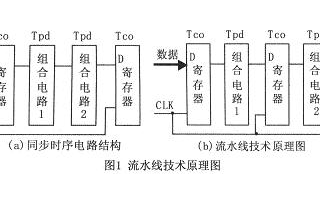

流水線是一種在時間上串行,在空間上并行的技術,其基本原理如圖1所示。將整個電路劃分為若干個流水線級,流水線每級之間設置寄存器鎖存上一級輸出的數據;每一級只完成數據處理的一部分;一個時鐘周期完成一級數據處理,然后在下一個時鐘到來時將處理后的數據傳遞給下一級;第一組數據進入流水線后,經過一個時鐘周期傳到第二級,同時第二組數據進入第一級,數據隊列依次前進。每組數據都要經過所有的流水級后才能得到最后的計算結果,但是對整個流水線而言,每個時鐘都能計算出一組結果,所以平均計算一組數據只需要一個時鐘周期的時間,這樣就大大提高了數據處理速度,電路在單位時間內處理的數據量就愈大,即電路的吞吐量就越大,保證整個系統以較高的頻率工作。

FPGA的結構特點很適合采用流水線設計,以Altera低成本系列Cyclone II為例,不僅有最多達68416個邏輯單元(LE),而且提供嵌入式存儲資源支持各種存儲應用和低成本DSP應用(如乘法器模塊、PLL)。每個LE均含有一個四輸入查找表LUT、一個可編程觸發器等。一般設計中,這個觸發器或者沒有用到,或者用來存儲布線資源。設計中可將一個算術操作分解成一些小規模的基本操作配置到LUT中,將進位和中間值存儲在寄存器中,在下一個時鐘內繼續運算。因此,在FPGA中采用流水線技術,只需要極少或者根本不需要額外的資源成本。特別是在需要進行大批量重復運算的場合,如數字信號處理中的卷積操作、FFT或FIR濾波器設計,采用流水線技術,可以大大提高系統運行速度。

1 FPGA中基本DSP運算的流水線設計與性能分析

加法器和乘法器是DSP中最基本的運算部件。在Quartus軟件平臺上設計加法器或乘法器可以采用原理圖法和VHDL語言兩種基本方法。考慮到參數可設置宏模塊(Library of Parameterrized Modtlles-LPM)經過嚴格測試和優化,可以發揮最佳性能,所以,我們采用原理圖設計方式,通過MegaWizard P1ug-In Manager工具引入1pm add sub和1pm mult兩種可設置流水線的LPM模塊,實現了不同位寬、不同流水線級數的加法器和乘法器設計,并選用CycloneII系列EP2C5Q208C7器件進行了綜合、布局布線、時序分析和仿真設計,以比較其性能的變化特征。

1.1 不同流水線級數的運算器性能比較

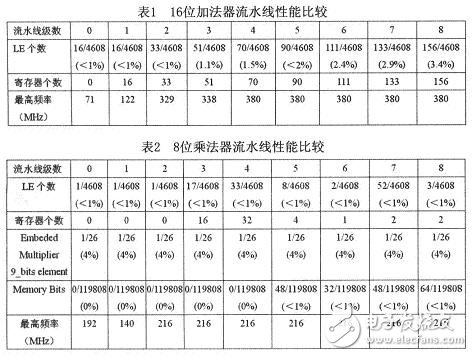

對16位加法器和8位乘法器分別選用不同的流水線級數進行設計,比較結果如表1、2所示。

由比較結果可見:

(1)采用流水線技術普遍比不用流水線工作速度顯著提高,體現流水線技術在高速DSP運算上的優勢。

(2)采用流水線技術在資源耗用(邏輯單元與寄存器個數、存儲器位數)上有所增加。

(3)采用不同的流水線級數在速度指標和資源耗用率上有所不同,流水線級數增加,速度指標不一定增加,但資源耗用大大增加,所以應注意速度和資源耗用指標的權衡。如對16位加法器,如不用M4K(專用存儲器資源),以采用2級流水線最佳;如選用M4K,則取6級流水最佳。8位乘法器則以2級或6級流水最佳。對于其他DSP運算,在設計時必須通過反復比較、設計,選擇符合系統性能要求的流水線級數。

1.2 不同位寬運算器相同流水線級數的性能比較

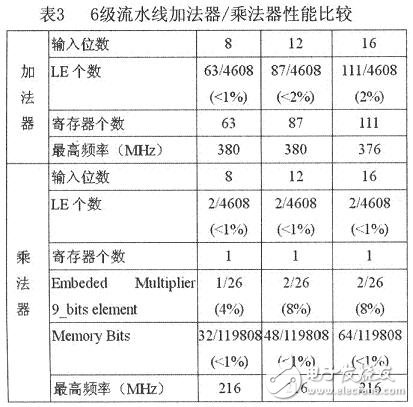

對采用6級流水的加法器和乘法器的數據位寬加以改變,通過綜合仿真,分析其性能指標的變化,見表3。

由比較結果可見:采用同樣的流水線級數時,工作速度基本相同,但耗用資源隨輸入位數的增加而急劇增加,加法器主要是邏輯單元LE個數的增加;乘法器則是存儲器位和嵌入式乘法器個數的增加。因此,對于不同的運算器電路,應根據需要選用不同型號的FPGA器件以滿足對不同資源的需要。如,僅作加法運算時,可以選用邏輯單元豐富的FPGA器件女HACEX系列、FLEX等系列;乘加運算則需要選擇內嵌乘法器模塊和存儲器模塊的Cyclone、CycloneII等系列。

2 基于FPGA實現DSP流水線設計中應注意的其他問題

2.1 流水線設計方法的選擇

流水線設計可分為原理圖和VHDL兩種基本方法。

如前所述,用原理圖輸入法設計時,為提高設計效率,應充分利用帶有LPM_PIPELINE的LPM模塊,并利用QuartusII(提供了40多種LPM函數)編譯器給出的LPM PIPELINE最佳數值(即最佳流水線級數),設定最佳LPM_PIPEINE值。

在無合適的I PM模塊可用時,需要用VHDL作為設計輸入。

流水線技術的實質就是在適當的地方加入寄存器,將前面的運算結果或輸入數據暫存,并在下一個時鐘到來時,將寄存值作為后一級運算的輸入。因此在用VHDL描述流水線時,只需對不含流水線的運算器描述代碼作適當改寫,施加必要的設計約束即可實現。一般通過在進程中加入WAIT語句或IF_THEN語句來測試敏感信號邊沿,實現寄存器或鎖存器。

如使用WAIT語句,常用的描述形式為:

PROCESS

BEGIN

wait until clk’event and clk=’1’; (上升沿觸發)

reg《=x;

END PROCESS;

其中的x是指輸入到所加流水線寄存器reg中的數據。

使用IF_THEN語句,常用描述方式為:

IF(clk’event and clk=’1’) THEN…

另外,用VHDL設計輸入時也可以利用Altera所提供的LPM函數,但必須在設計實體前使LPM庫可現,即加入以下語句:

LIBRARY lpm;

USE lpm.lpm_components.ALL;

2.2 流水線的首次延時和寄存器的觸發時間

對圖1所示系統進行延時分析,圖中組合邏輯的延遲包括兩級,合理設計的流水線結構中,其延遲時間應大致相等,設為2Tpd,插入每級寄存器組的觸發時間為Tco。因此,從輸入到輸出總的等待時延為:TDl=2(Tpd+Tco),稱為流水線設計的首次延時(First Latency)。對于連續的運算,由于加上寄存器組后,每級計算后的中間結果都能暫時保存,下一個時鐘到來時,可以直接參與下一級邏輯運算,無需等待從系統的輸入端傳來數據。因此,第二個結果及以后的運算結果的獲得只需要一個時鐘周期,等待的時延為:TD2=Tpd+TCO。

可見,流水線設計的首次延時與流水線正常延時相比要長得多。所以在選擇是否采用流水線技術時,要分析DSP運算的頻率。當需要進行連續運算(即流水線一直是滿負荷)時,采用流水線可以大大提高數據吞吐率;但如果只是偶爾需要加、乘運算,由于首次延時大于非流水線方式下的pin to pin延時,流水線應用效果變差,而且還犧牲了額外的芯片資源,所以不推薦使用流水線。在FPGA/CPLD中,器件的延時Tpd要比寄存器的觸發時間TCO長得多,一般分析流水線吞吐延時可以忽略TCO。但是在高速運算場合或流水線技術較多時(如視頻信號處理或無線通信中的數據處理),TCO與Tpd相比已不可忽略,必須仔細選擇流水線的級數,防止TCO的影響造成流水線的瓶頸。

2.3 嵌入式存儲器塊資源的充分利用

在FPGA器件中,嵌入式存儲器塊(Embedded Memory)是為支持各種存儲器應用和DSP應用提供的專門資源。如Altera公司FLEX10K系列器件提供了3個嵌入式陣列塊EAB,每個EAB提供可靈活設置的2048位RAM,Cyclone系列提供了數十個M4K資源,每個M4K提供4608位RAM,可單獨使用,也可組合使用。使用EAB或M4K構建運算器如乘法器,實質是構成乘法查找表,其運算速度比采用LPM的乘法器速度更快,只是由于資源有限,只能實現小型乘法器。如能把基于嵌入式陣列塊的小型乘法器和流水線技術相結合,則能夠實現運算量和速度的進一步提高。

2.4 控制流水線和數據流水線的劃分

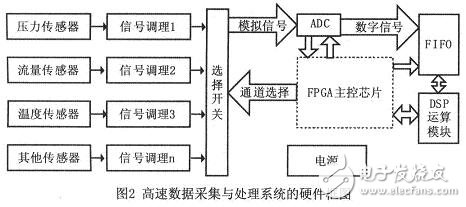

由于數字信號處理系統復雜性的不斷提高,在利用流水線技術實現DSP運算設計時,還有一個需要考慮的問題就是控制流水線和數據流水線的劃分問題。如在高速數據采集與處理系統中,采樣數據的處理主要涉及DSP運算,可以歸入數據流水線。各輸入通道傳感器與信號調理電路的選通控制、模數轉換、數據緩沖與傳送、數據運算控制則需要主控芯片完成,如圖2所示。高速主控芯片可以選用FPGA器件,采用流水線技術,將數據采集與處理過程中的通道選擇、模數轉換、數據緩沖與發送、數據運算四部分的控制過程設計為四級流水線進程,以減少數據采集與處理的平均作業時間,實現高速率的數據采集。主控芯片的流水線技術可以歸入控制流水線范疇。

3 結論

通過實驗對比,驗證了利用流水線技術可以實現基于FPGA器件的高速DSP運算。在具體運算器設計中要通過綜合過程,比較和優選流水線級數以滿足速度和資源優化的需要。DSP系統在進行流水線設計時要根據運算頻率明確用否流水線,合理劃分控制流水線和數據流水線,還要注意合理選用原理圖和VHDL描述,充分利用帶有LPM_PIPELINE的LPM和EAB(M4K)等資源,最大限度提高系統數據吞吐率和設計效率。

-

處理器

+關注

關注

68文章

19658瀏覽量

232468 -

dsp

+關注

關注

555文章

8111瀏覽量

353822 -

FPGA

+關注

關注

1639文章

21887瀏覽量

610860

發布評論請先 登錄

相關推薦

基于FPGA的DSP系統設計中的流水線技術主要應用在哪些方面?

FPGA中的流水線設計

流水線型ADC MAX1200 及其與DSP 的接口

FPGA重要設計思想及工程應用之流水線設

基于FPGA的高速高階流水線工作FFT設計

高速高階FPGA流水線工作FFT設計

DSP設計中的流水線數據相關問題解析

基于FPGA的DSP運算技術實現流水線應用系統的設計

通過FPGA器件的DSP高速運算可實現流水線技術在系統中的應用

通過FPGA器件的DSP高速運算可實現流水線技術在系統中的應用

評論