基于P89C51RD2和FPGA的信號延時模塊主要用在傳輸時鐘信號、數字同步信號等對信號延遲有高要求的點對點傳輸系統中,它可對多路信號進行單獨的適當延時調整。造成信號的延遲原因有:不同的傳輸線路、信號處理時間不同以及器件速度存在差異等。無論何種原因,延時模塊可以對輸入的已存在有延時積累的信號進行不同精度、不同范圍的延時量調節,使信號到達終端后相對延遲時間符合要求。由于利用了可編程器件FPGA和增強型單片機,延時模塊不僅能較好地實現其功能,而且實現了系統的模塊化和微型化,利于模塊在系統中的使用和模塊的二次開發。

系統結構及硬件設計

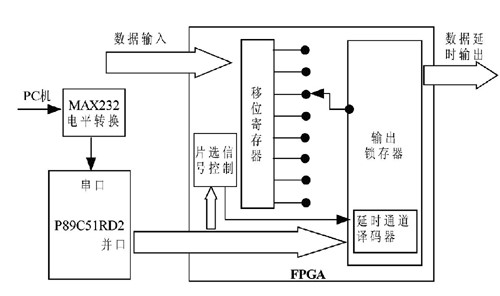

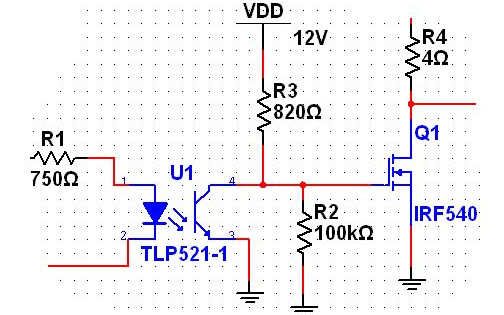

系統結構框圖如圖1。其硬件結構比較簡單,主要由單片機P89C51RD、RS-232/TTL接口電路MAX232和可編程邏輯器件FPGA三部分組成。單片機P89C51RD2是上位PC機和FPGA的連接紐帶,它通過并口發送數據給FPGA,另一邊通過RS-232/TTL接口芯片與PC機進行串行通訊;PC機主要功能是實現延時調整的可視化操作;FPGA是延時調整處理的硬件實現,單片機將PC送過來的延時調整參數輸入FPGA,FPGA在單片機的控制下對信號進行延遲處理,最后送入相應傳輸通道。某些系統使用現場存在較強的電磁干擾,模塊的設計考慮信號隔離問題,故對串行接口進行了電氣隔離,強化了PC機和模塊通訊的安全系數。

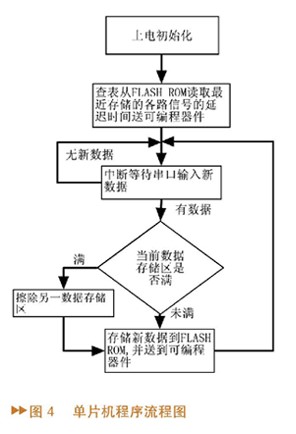

延時模塊正常上電后,單片機P89C51RD2首先從數據存儲區讀出最近一次存儲的延遲時間、信號通道等參數,并轉發到FPGA數據接口。FPGA根據接收到的參數,首先篩選出目標地址以便切換到對應的信號通道,然后再根據時間對該通道進行預定的延時,恢復先前調整好的延時信號。在模塊運行期間,P89C51RD2實時監測、接收來自上位PC機發送的新延時數據。如果需要對某一路信號的延時量進行調節,通過PC機的串口發新數據,P89C51RD2中斷收到新數據后,將數據分成兩路處理:一路進入到單片機的數據存儲區,待下次上電讀取使用;另一路則轉發至由FPGA控制的延時控制,實現信號的延遲時間調整。

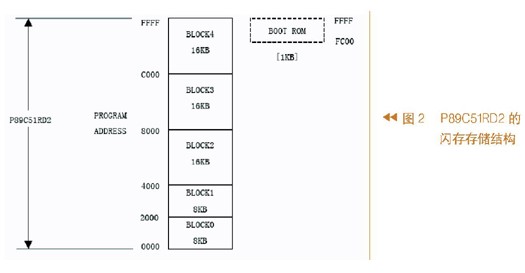

塊使用的P89C51RD2是PHILIPS公司內核基于8 位80C51單片機的派生產品,它們在完全保留80C51 指令系統和硬件結構的大框架外,還具有多方面的功能加強、擴展、翻新和創新,其中在應用中編程(IAP:In-Application Programming)是最顯著特點之一。在應用中可編程是指MCU可以在系統中獲取新代碼并對自己重新編程,即用程序來改變程序。P89C51RD2的IAP功能實現是通過PHILIPS 公司提供的BootROM 固件來完成的,它位于0FC00H?0FFFFH空間,與閃存空間重疊(見圖2)。固件中已經固化有擦除和編程等子程序,PHILIPS 公司提供了尋址該固件的方法,只要用戶程序簡單調用BootROM中帶適當參數的公共入口,即可實現所需要的操作。

P89C51RD2閃存結構見圖2,它具有如下特點:

1. 其閃存空間是分塊的64kB的閃存空間,共分5塊,由低到高分別為8kB(BLOCK0)、8kB(BLOCK1)、16kB(BLOCK2)、16kB(BLOCK3)以及16kB( BLOCK4);

2. 每一塊都可以單獨擦除;

3. 在程序中可以調用IAP功能對閃存中的每一字節進行單獨編程。

正是由于上述三個特點,在不外擴展存儲器情況下,將程序空間剩余下的閃存空間作為數據空間,把單片機接收中斷采集到的信號通道、延遲時間等參數存儲下來,實現掉電數據保存。

軟件設計

整個延時模塊的軟件包括了PC機發送參數程序,單片機接收并存儲參數程序和FPGA信號延時處理程序。

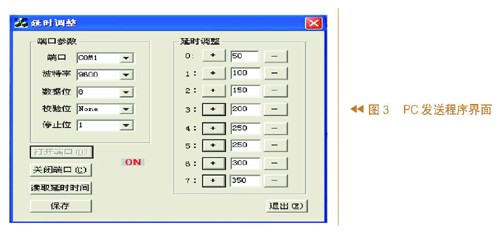

PC機發送參數程序是用戶將PC機的串口與模塊連接,通過PC機的發送程序界面,很容易對信號進行延時調整。發送程序采用VC作為編程語言,調用串口控件,設計方便且界面簡潔,界面如圖3所示。發送的每個數據幀8位,包括延遲時間和信號通道兩個參數,其中高三位是要調整的信號通道,后五位表示延遲的時間。發送程序中,對界面中的“+”或“?”進行一次操作,PC就通過串口向單片機連續發送8路信號延時參數,即只要調節了任一路信號的延時,PC機就會連續發送8個數據幀。

在P89C51RD2的64k閃存空間中,地址為0000H-7FFFH的32kB閃存空間作為程序空間,整個單片機程序編譯后為15k,所以32k的程序空間足夠大。余下的8000H?FFFFH的32kB 閃存空間留作數據存儲空間。兩塊數據存儲空間輪流使用,當數據量存滿其中一塊時通過程序跳轉到另一塊,在使用前先將該塊擦除。

各函數介紹如下:

main()——主程序;

InitUart(void)——串口初始化;

IapInit(void)——IAP功能初始化,使用IAP功能前必調用;

PowerOnRead(void)——上電讀取最近一次存儲的參數。模塊對上電時間要求不苛刻,最新數據的地址可通過查表方式尋找。每一個數據幀占一個數據存儲空間,由于單片機每次中斷都接收到8個數據幀,所以將每8個數據存儲空間劃分成一組,這樣只要查詢每組的頭一個地址就能快捷地完成查詢,大大節省了查詢時間。

EraseBlock (uint AddressRestore)——判斷當前數據存儲空間塊滿,并擦除;

RestoreData(void)——數據存儲在數據存儲空間;

FPGADataUp(uchar DataRec)——更新FPGA接口數據。

在程序中,要多次調用BootROM固件中的子程序。由于IAP子程序接口是匯編語言,為了編寫方便,同時使程序框架明了,編寫了一個IAPLIB.A51匯編語言接口函數庫和IAPLIB.H頭文件。在程序中加上IAP.H頭文件,調用固件程序時就不需在C51程序中嵌入匯編,而是像調用C語言函數一樣簡單,這大大簡化了編程。

FPGA設計

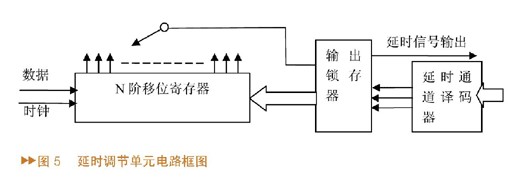

FPGA主要設計了DECODE延時通道譯碼器、CS片選信號控制器、N階SHIFTER移位寄存器。其中譯碼器用于完成對單片機并口送來的數據進行通道、時間參數的分離,用通道參數進行尋址和譯碼,這是一種簡單的譯碼邏輯和觸發電路。N階移位寄存器用于完成對信號進行N階的延時處理,是延時處理的核心單元。單路信號延時調節的基本框圖見圖5。

延時通道譯碼器將單片機并口送來的延時參數送入鎖存器,同時輸出控制電路將移位寄存器對應的延時階切換到輸出端。從不同的階引出信號即可獲得不同的延時量。控制時鐘和移位寄存器的階數決定了延時步進調節精度和延時調節范圍。如果定時模塊有N個信號通道,每個定時模塊集成N個完全相同的延時調節單元,就可實現獨立調節各個通道信號延時大小的功能。集成的延時調節單元越多,占用可編程芯片的資源就越多,這可以根據實際需要選擇可編程邏輯器件。

FPAG軟件的設計采用“自頂向下”、“軟硬兼施”的設計方法,主要的各單元設計采用VHDL語言描述完成,而整個多路信號的延時功能處理采用圖形輸入設計方法。軟件設計完成后,根據電路原理圖進行引腳鎖定,然后啟動編譯程序來編譯項目。編譯器將進行錯誤檢查、網表提取、邏輯綜合和器件適配,然后進行行為仿真、功能仿真和時序仿真。最后通過編程器方式將POF文件下載到EPROM中。加電后,FPGA將EPROM中數據讀入片內編程RAM中,完成配置,從而生成硬件電路。

模塊功能調試實現

模塊在調試中出現P89C51RD2有時上電程序運行不正常,讀取程序空間是空的。但是只要上電工作起來,就恢復正常。懷疑由于上電復位時序混亂,造成誤調用固件擦除芯片子程序。采用專用復位芯片替換電容電阻加二極管的復位電路,使問題得到了解決。同樣,在單片機正確送數情況下,FPGA上電出現不能正常恢復預設好的延時信號,信號總是零延遲(第一次上電,單片機數據存儲空間內沒有數據,信號就處于零延時狀態),但在工作狀態下,能夠很好地實現延時調節。懷疑這種情況是因存在復位問題而導致,但專用復位芯片不能解決問題。經多次檢查程序,發現硬件語言程序中觸發語句是電平觸發,改寫為脈沖上升觸發后問題得以解決。

結束語

采用單片機和FPGA設計的延時調節模塊,硬件結構簡單,設計集成度高。軟件方面,單片機程序將C語言和匯編語言很好地結合,FPGA充分發揮了硬件語言易改變電路結構和算法的優越性。提高FPGA中移位寄存器的時鐘頻率,同時相應增加移位寄存器程序輸出階數,可實現更高精度的延時步進調節和增大延時調節范圍。因此可以在不改變模塊硬件結構基礎的上,通過軟件升級來提高模塊的性能,從而擴大模塊的應用領域。

-

FPGA

+關注

關注

1630文章

21761瀏覽量

604448 -

單片機

+關注

關注

6039文章

44583瀏覽量

636600 -

寄存器

+關注

關注

31文章

5357瀏覽量

120720

發布評論請先 登錄

相關推薦

STM32單片機的延時原理和延時函數方法

基于單片機與FPGA可調延時模塊的設計

基于單片機+CPLD的多路精確延時控制系統設計

基于單片機與FPGA可調延時模塊的設計

實例解析FPGA和單片機的串行通信接口設計

單片機的PWM應用和延時調用程序的詳細資料概述

單片機延時是怎么實現的

華大單片機HC32L136+RTT踩坑(官方延時函數)

利用單片機和FPGA實現系統中可延時調節模塊的設計

利用單片機和FPGA實現系統中可延時調節模塊的設計

評論