在無線數據傳輸中,由于信道中的噪聲干擾,在接收端會引入一定的誤碼率(Bit Error Rate,BER)。高質量的數據業務要求較低的BER。為了達到較低的BER,經常采用信道編碼技術。卷積編碼和Viterbi譯碼是廣泛使用的信道編碼技術,具有一定的克服突發錯誤的能力,可以降低信道的誤碼率,帶來很高的編碼增益。信道編碼的引入在提供糾錯能力的同時,還擴展了信號的帶寬。為了保證頻帶的利用率,本文采用QPSK調制方式,使數據調制在中頻載波上,實現數據的可靠傳輸。

本文所述的中頻調制解調系統具有以下特點:

(1)所有算法(編碼、調制、解調和譯碼)都是在Xilinx公司的FPGA芯片中實現的,結構簡單,體積小,功耗低。

(2)具有很好的實時性。對于1Mbit/s以上的數據速率,譯碼延遲不超過0.1ms。

(3)模塊化的設計使得系統具有一定的兼容性,只需要修改少量程序,即可實現各種卷積編碼和不同的調制中頻。

(4)與浮點算法的仿真性能相比較,采用定點算法的系統性能損失不大,并能在較低的信噪比提供可靠的數據傳輸。

1 系統總結構及硬件設計

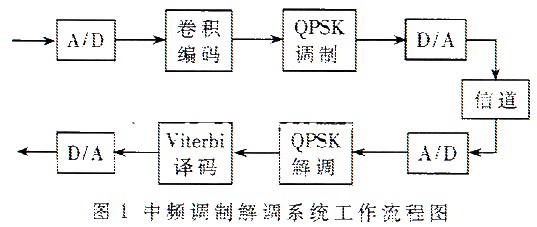

圖1是中頻調制解調系統的工作流程圖。在發端,數據通過A/D轉換器采樣后進入FPGA,在其中完成(2,1,7)卷積編碼和QPSK調制后通過D/A轉換器輸出。在收端,接收到的信號通過A/D轉換器采樣后進入FPGA,在其中完成QPSK解調和Viterbi譯碼后通過D/A轉換器輸出。

2 系統的FPGA實現

系統主要分為編譯碼和調制解調兩大部分,下面分別敘述這兩部分的原理及設計。

2.1 卷積編碼與Viterbi譯碼的FPGA實現

2.1.1 (2,1,7)卷積編碼

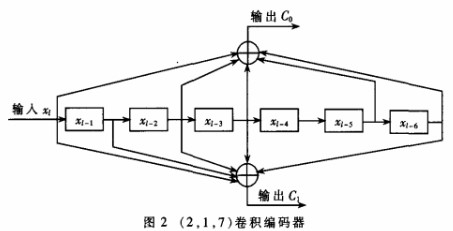

典型的(n,m,k)卷積碼編碼器是指輸入位數為m、輸出位數為n、約束長度為k的卷積碼編碼器,其編碼速率為m/n。一個(2,1,7)的卷積編碼器如圖2所示,可用六個移位寄存器實現。

2.1.2 Viterbi譯碼

Viterbi譯碼算法是Viterbi于1967年提出的一種概率譯碼算法。其主要思想就是最大似然譯碼。譯碼時,將接收序列與根據編碼產生的網格圖上面的所有路徑進行比較,求出其漢明距離或歐式距離,選出具有最小距離的路徑,那么這條路徑上的序列與發送序列相同的可能性最大。在AWGN信道中,當使用歐式距離時,Viterbi算法的性能最好。因此,這種算法是最優最大似然譯碼算法。Viterbi譯碼器分為硬判決譯碼器和軟判決譯碼器,軟判決譯碼器與硬判決譯碼器相比有2~3dB的增益,而譯碼器結構復雜度增加不大。

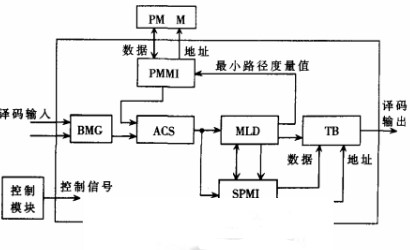

由Viterbi算法的基本原理可得典型的Viterbi譯碼器,如圖3所示。

分支路徑度量產生單元BMG(Branch Metric Generate)用于產生接收序列與狀態轉移分支上編碼輸出數據之間的距離。令長度為n的接收信號為R=(r1,…rn),與之相應的發送信號為C=(c1,…cn)。因為具有最小歐式距離的路徑也就是具有最大相關的路徑,所以定義分支路徑上的度量為:

由于此分支路徑度量沒有平方運算,所以可將狀態轉移分支上的編碼輸出數據存儲在查找表內,這樣只需進行加減和查表運算,大大減小了實現的復雜程度。以上計算公式中數值為連續值,而本設計采用的是軟判決譯碼器,故只需對輸入的接收信號進行均勻量化即可(量化比特數為q)。

加比選單元ACS(Add-Compare-Select)模塊包括若干個單個狀態加比選模塊ACSU,一個ACSU模塊執行一個狀態 的路徑度量升級。ACSU模塊的具體個數根據譯碼器的速率要求而定。對于低速的譯碼器,為了節約芯片的面積,可以使用較少的ACSU模塊進行時分復用;而在高速Viterbi譯碼器的設計中,則采用全并行的結構,ACSU模塊的個數等于網格圖上的狀態數N=2k-1。譯碼器開始工作時,給路徑度量設定一個初始化正值。在度量升級過程中,路徑度量的不斷累加會造成溢出。因為在度量升級時只是比較大小,所以在每次度量升級之后,所有的路徑度量值減去路徑度量值中的最小值,而不會影響路徑度量向的大小關系。同時,為了下次路徑度量升級不出現負值,需要對所有的度量值加上一個恒定常數。經過歸一化處理后的路徑度量,其最大值與最小值相差不超過2 q(k-1)。

所以,對于q比特而軟判決編碼長度為k的Viterbi譯碼器,其路徑度量長度為q+log2(k-1)比特。

MLD(Most-Likelihood-Decision)模塊用于在所有狀態的路徑度量中找出最大值,具有最大路徑度量的幸存路徑便是最大似然路徑。在時刻L時,MLD電路判決最大似然路徑,將其末端節點狀態送至TB模塊。同時為了保證下次的路徑度量升級不出現負值,還要找出最小值送到PMMI模塊,在其中進行歸一化處理。

PMMI模塊和SPMI模塊分別是ACS模塊與路徑度量存儲器PMM(Path Metric Memory)之間和幸存路存儲器SPM(Survivor Path Memory)與MLD模塊之間的接口模塊。同時,TB(TraceBack)模塊也通過SPMI模塊讀取幸存路徑存儲器信息。針對不同的存儲方式,SPMI和PMMI的復雜程度也不同。ACSU模塊的復用程度越高,其接口電路越復雜。

TB模塊從SPM中讀取當前時刻64條路徑的幸存信息,根據末端狀態可以找到相應的最大似然路徑在時刻t的幸存信息,從而找到t-1時刻最大似然路徑上的狀態。依此類推,直至找到最大似然路徑在t-L+1時刻的狀態,狀態的最高位即為譯碼輸出。

FPGA可以實現流水線操作,而各個模塊可以同時進行工作,所以需要控制模塊處理各個模塊間的時序關系。每個子模塊都有一個控制信號,使得輸入數據可以在各個模塊之間進行流水操作。

由于本方案是基于各個功能單元自上至下設計的,靈活性較大,稍加修改子模塊,便可以用于實現各種卷積碼的Viterbi譯碼器。

2.2 QPSK調制與解調的FPGA實現

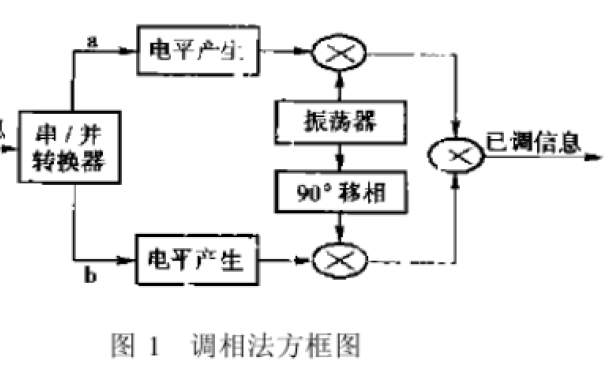

QPSK調制模塊由成形濾波和上變頻兩部分組成。成形濾波具有兩個功能,即限帶和抗碼間干擾。成形濾波采用查表的方式實現,四倍內插,升余弦滾降。形成后的數據與NCO產生的本地載波進行上變頻運算。

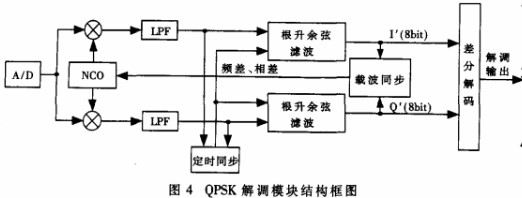

QPSK解調的結構框圖如圖4所示。解調模塊由下變頻、低通濾波、根升余弦濾波和載波同步幾部分組成。I、Q兩路的調制信號先經過本地載波NCO下變頻,再通過低通濾波器LPF得到基帶信號。基帶信號需要進行相應的根升余弦濾波。由于本地載波與發端載頻之間有一定的偏差,所以要根據解調后的信號估計頻差并修改要地載波NCO的參數,實現載波同步。數據經過根升余弦濾波后進行差分解碼,解調后頭這入譯碼器單元。

3 系統性能分析與結論

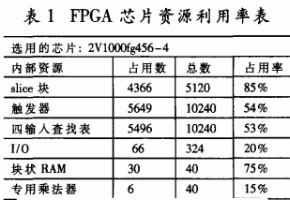

綜上所述,系統主要功能都是在FPGA內完成的。本文選擇Xilinx公司的100萬門FPGA芯片XC2V1000,在ISE 6.2i環境下進行編程開發。系統的資源占用情況如表1所示。

為了測試系統在噪聲下的誤碼率性能,在發端和收端之間引入噪聲源,在70MHz中頻上進行數據傳輸。使用誤碼率分析儀進行現場測試,獲得的測試誤碼率曲線如圖5所示。為了方便比較,圖中給出了未編碼傳輸系統的理想誤碼率曲線。由于定點實現、定時同步、載波同步等誤差因素,調制解調的實現損耗將近1dB;而viterbi譯碼的量化輸入和截短譯碼(本方案采用3比特量化和64步截短譯碼)帶來的實現損失約為1dB。(2,1,7)卷積碼的編碼增益約為5~6dB,所以測試誤碼率曲線與未編碼傳輸系統的理想誤碼率曲線之間的差距是3~4dB。換言之,本系統的實現增益為3~4dB。

綜上所述,本系統設計簡單、功耗低、性能良好,可在中頻范圍內進行高速數據的可靠傳輸。在不改變系統結構的情況下,稍加修改可廣泛應用于其它類型的編碼調制系統中。

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604307 -

芯片

+關注

關注

456文章

50950瀏覽量

424758 -

QPSK

+關注

關注

2文章

63瀏覽量

26587

發布評論請先 登錄

相關推薦

基于VHDL方式實現了QPSK數字調制解調電路的設計

基于FPGA 的QPSK 調制解調電路設計與實現Design

基于F PGA的QPS K調制解調電路設計與實現

π/4-QPSK調制方式及其與GSMK調制方式的比較

采用AD9789與FPGA相結合實現全數字QPSK射頻調制的方案

基于QPSK數字調制解調的FPGA實現

采用QPSK調制方式和卷積編碼實現中頻調制解調系統的FPGA功能

采用QPSK調制方式和卷積編碼實現中頻調制解調系統的FPGA功能

評論