1 引言

互補金屬氧化物半導體(CMOS)圖像傳感器具有功耗低,集成度高和易于控制等特點,其信噪比,光靈敏度和動態(tài)范圍等性能可與成熟的電荷耦合器件(CCD)圖像傳感器相媲美,因此,CMOS圖像傳感器為發(fā)展微型化、數(shù)字化和多功化成像器件開辟了新思路。高分辨率、高幀頻的CMOS圖像采集系統(tǒng)在高速運動分析、高速物體追蹤及高速變化過程罔像的獲取等領域應用廣泛。

2 高幀頻COMS相機電子學系統(tǒng)模塊

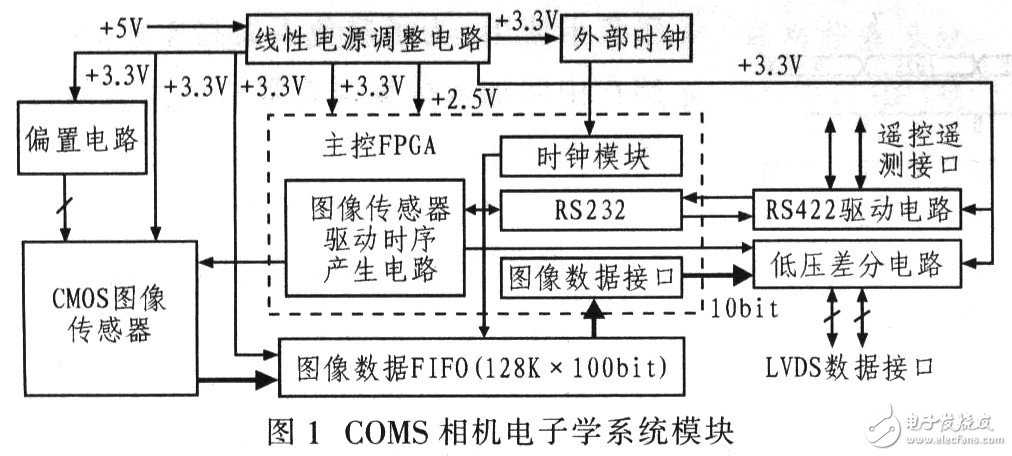

相機電子學系統(tǒng)包括CMOS圖像傳感器焦平面板和驅(qū)動控制板,原理結構如圖1所示。主要功能模塊包括:CMOS圖像傳感器、LD0電源調(diào)整電路及濾波電路、時序電路、時鐘電路、圖像數(shù)據(jù)接口電路、RS422驅(qū)動電路,以及低壓差分電路等。

2.1 焦平面板

經(jīng)濾波電路平臺輸出+5 V二次電源電壓,冉經(jīng)LD0電壓調(diào)整電路輸出+3.3V電壓。該電壓經(jīng)濾波后向圖像傳感器及偏置電路提供電源。

MT9M413內(nèi)部集成有10 bit A/D轉(zhuǎn)換器(簡稱ADC),可直接輸出3.3 V的數(shù)字信號。時序驅(qū)動板CPLD的端口電壓為+3.3 V,因此兩者之間可直接傳輸信號,無需電平轉(zhuǎn)換電路。MT9M413含有10個輸出通道,數(shù)據(jù)總線多達100條,因此采用微型板問連接器連接焦平面板和驅(qū)動控制板,以減小電路板體積和質(zhì)量。

2.2 驅(qū)動控制板

驅(qū)動控制板是相機控制系統(tǒng)的核心,其作用主要包括:產(chǎn)生MT9M413的丁作時序;FIF0讀寫控制;實現(xiàn)間接指令接口RS232(RS422電平);實現(xiàn)圖像輸出接口(LVDS電平)。驅(qū)動控制板的時序信號和控制信號通過FPGA實現(xiàn),綜合考慮速度、器件容量、工作溫度、功耗及抗輻射能力等因素,選用Actel公司的APA600型FPGA,該器件內(nèi)置2個鎖相環(huán),I/O電壓為+3.3V,內(nèi)核電壓為+2.5 V,屬于低功耗器件。

2.2.1 MT9M413圖像傳感器工作原理

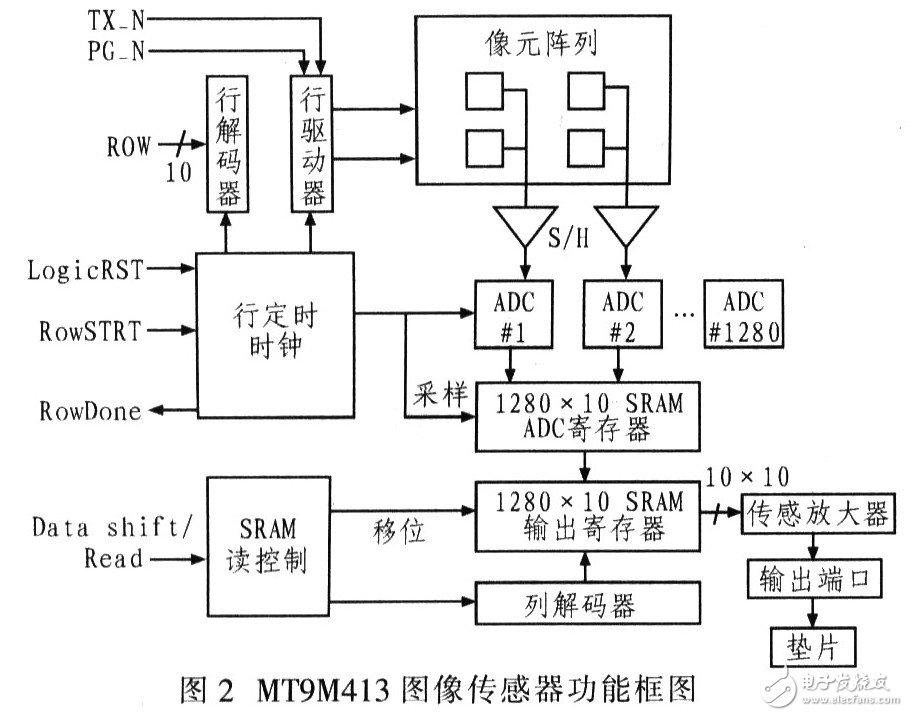

MT9M413是Micron公司的具有3.3V電源,1.31 M像素的CMOS數(shù)字圖像傳感器,其分辨率為l 280 H×1 024 V;主時鐘為66 MHz時,幀頻可達500f/s;動態(tài)范圍為59 dB;快門時間范圍為10μs~33 ms。片內(nèi)集成10 bit自標定、全數(shù)字接口的ADC。MT9M413功能框圖如圖2所示,其功能組件包括:像元陣列、行地址選擇邏輯、列放大器組、l 280個10位ADC模塊、ADC寄存器和讀出寄存器模塊。

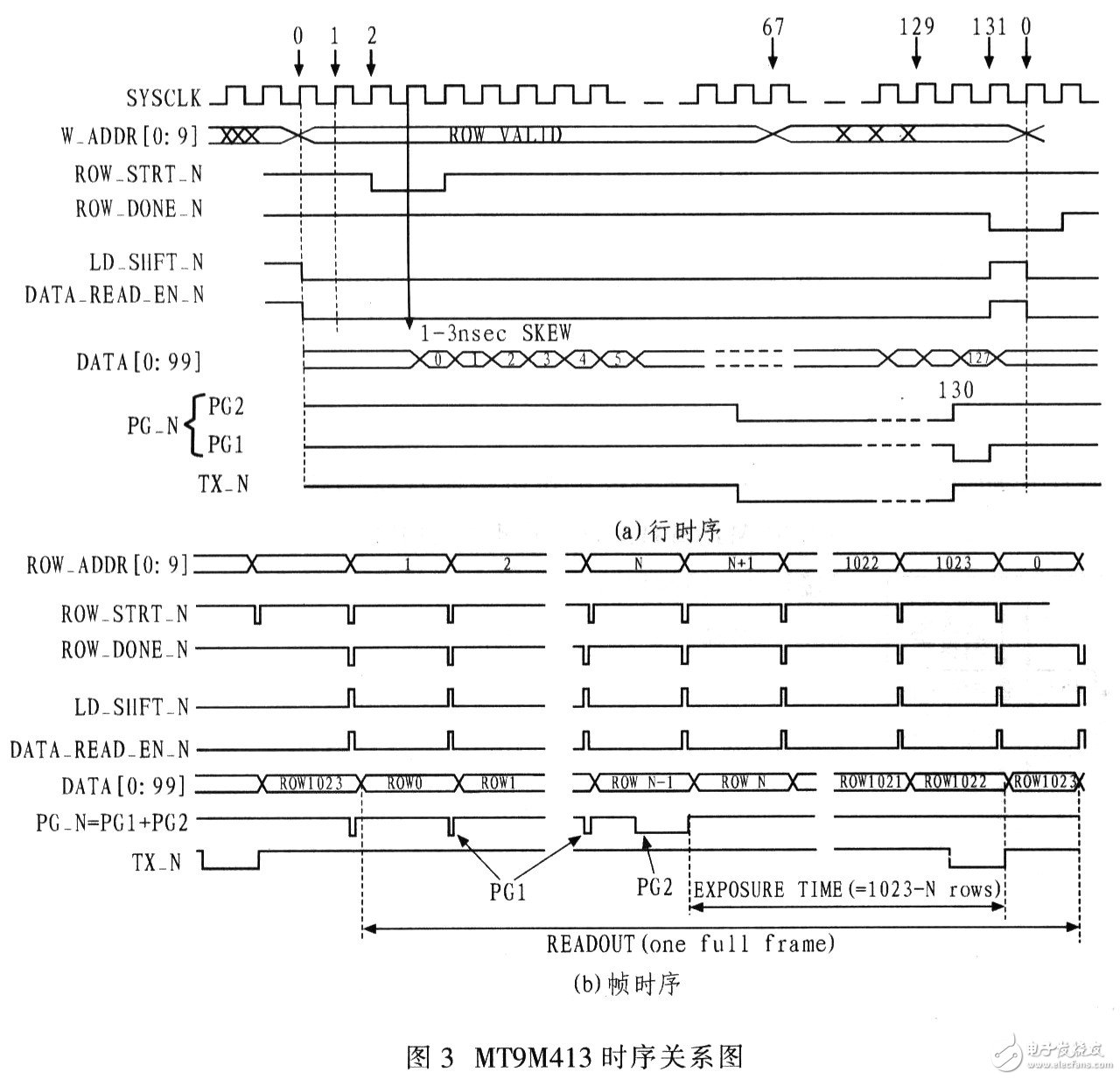

MT9M413的時序關系如圖3所示。10位ROW—ADDR行地址總線輸入選擇讀出的像素行,ROW_STRT_N信號開始從像素行讀模擬數(shù)據(jù),并數(shù)字化地存儲在ADC寄存器中,當這一系列工作完成后,器件輸出ROW_DONE_N信號。當DATA_READ_EN_N信號有效時,LD_SHFT_N信號低電平有效,從ADC寄存器開始向輸出寄存器轉(zhuǎn)移數(shù)字數(shù)據(jù),DATA_READ_EN_N信號使輸出寄存器使能。DATA_READ_EN_N置低保持兩個時鐘后。開始讀取新像素行和轉(zhuǎn)換循環(huán)。在新行轉(zhuǎn)換同時允許讀取先前轉(zhuǎn)換的數(shù)字信號,因此行周期是從ROW_STRT_N信號開始到。ROW_DONE_N信號返回,或在LD_SHFT_N和DATA_READ_EN_N信號有效周期加兩個時鐘的時間。PG_N(PGl+PG2)信號同時置位整個像素陣列的光探測器進行光積分;TX—N信號同時為整個陣列的每一個像素轉(zhuǎn)移光探測器的電荷到存儲器,結束光積分。必須注意的是,在連續(xù)模式下,PG—N和rrx—N脈沖必須持續(xù)64個SYSTCLK時鐘周期;在ROW—STRT_N為低電平時,ROW—ADDR地址總線才有效,且至少持續(xù)66個SYSCI.K時鐘周期。通過增加光積分階段的行轉(zhuǎn)移脈沖個數(shù)調(diào)整曝光時間。對MxN陣列的CMOS器件.Ⅳ個行轉(zhuǎn)移周期即可完成一幀圖像的所有行轉(zhuǎn)移。為了增大積分時間,可以增加行轉(zhuǎn)移的數(shù)量,使得行轉(zhuǎn)移脈沖個數(shù)大于Ⅳ,當然在第Ⅳ個轉(zhuǎn)移周期之外的信號無效。

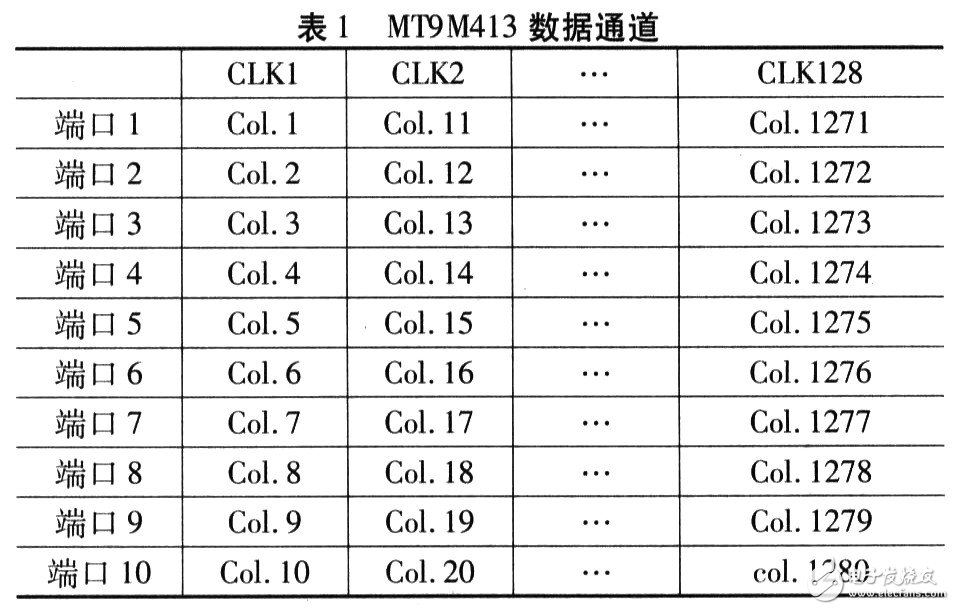

圖像信號從10個通道同步讀m,每個通道的位寬均為10 bit.每個通道所對應的像元編號如表1所示。

整幀圖像輸出需要128個時鐘周期。隨后將1。5通道合并成一路50 bit數(shù)據(jù):6~10通道合并成一路50 bit數(shù)據(jù),分別緩存在兩個數(shù)據(jù)FIF0中.每個FIFO的容量為128 KxS0bit.并將上述兩路信號傳輸給FPGA進行并.并轉(zhuǎn)換,最后輸m一路10 bit并行圖像數(shù)據(jù)。

2.2.2 FIFO讀寫控制

由于M’F9M413每個時鐘周期可同時輸出100位數(shù)據(jù),必須經(jīng)過FPGA并。并轉(zhuǎn)換。轉(zhuǎn)換成10位數(shù)據(jù)供LV:DS數(shù)據(jù)采集卡使用。為了避免丟失高速數(shù)據(jù),必須在中間加入數(shù)據(jù)緩存器。該系統(tǒng)設計選用兩片128 KxS0 bit的FIFO。它是一種高速、低功耗的先入先出型緩存器。

2.2.3 基于VHDL硬件電路的實現(xiàn)

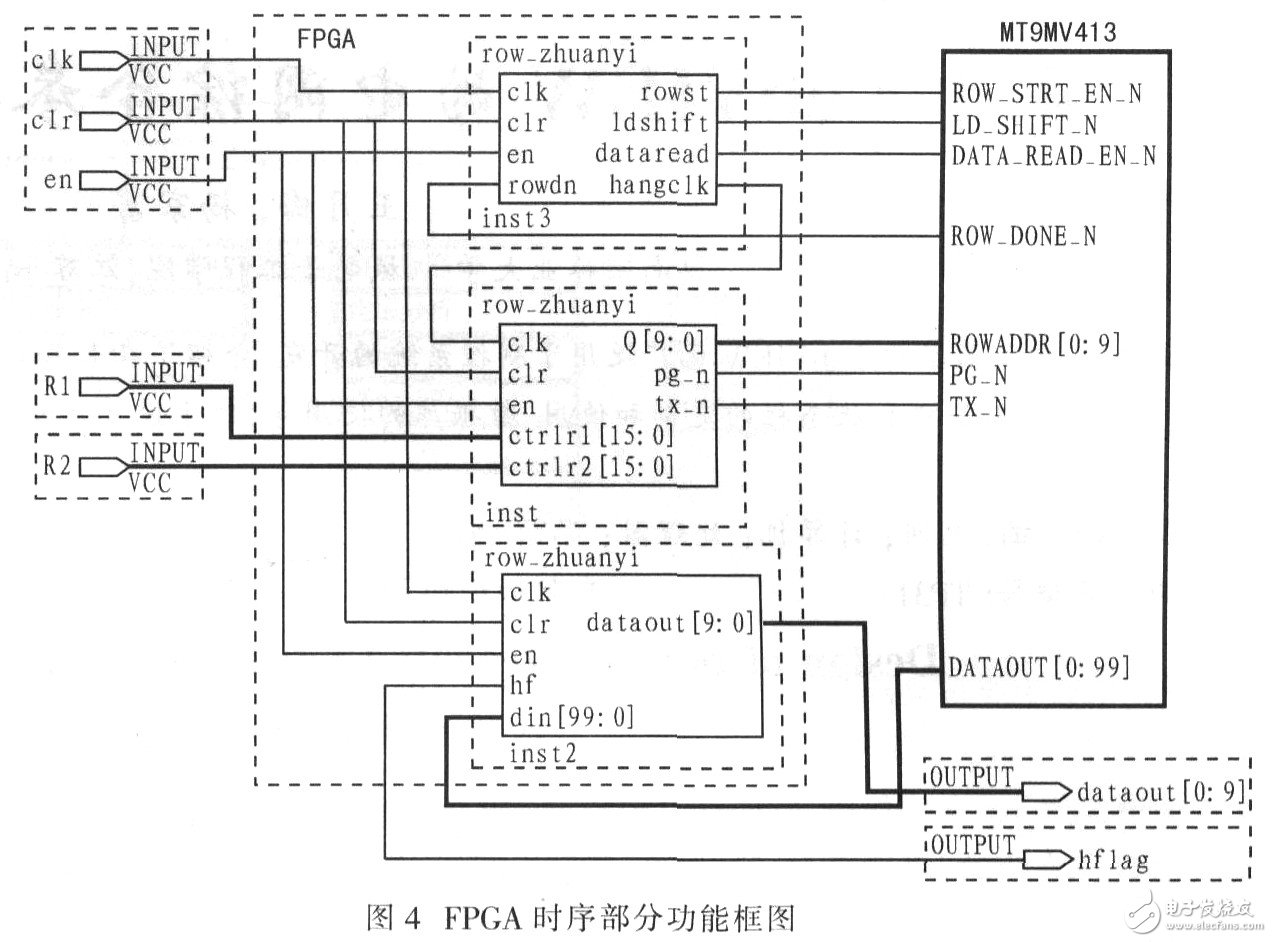

VHDL硬件描述語言支持自上而下的設計方法。根據(jù)自上而下的設計方法,確定輸入/輸出信號,同時根據(jù)時序劃分功能模塊,然后把所有的輸入/輸出信號分配到各個功能模塊中,每個功能模塊分別進行VHDL設計輸入、功能仿真、后仿真。在各個功能模塊實現(xiàn)各自功能后,例化到頂層設計中,完成頂層的VHDL設計輸入、功能仿真、綜合、后仿真。直至達到設計要求。部分VHDL硬件捕述如圖4所示,其中R1是幀計數(shù),R2是行計數(shù)。總曝光時間的計算公式如下:總曝光時間=Rl×行周期×l 024+(1 023一R2)×行周期。

3 結語

該系統(tǒng)沒計根據(jù)CMOS的時序要求.經(jīng)仿真調(diào)試能夠產(chǎn)生相應的驅(qū)動脈沖和偏置電壓,并通過遙控數(shù)據(jù)的注入,實現(xiàn)了曝光時間的可調(diào)控制。

-

芯片

+關注

關注

459文章

51836瀏覽量

432336 -

圖像傳感器

+關注

關注

68文章

1946瀏覽量

130167 -

vhdl

+關注

關注

30文章

819瀏覽量

129236

發(fā)布評論請先 登錄

相關推薦

基于FPGA的圖像邊緣檢測系統(tǒng)設計,用VHDL語言實現(xiàn)該怎么做?

如何使用VHDL硬件描述語言實現(xiàn)的十六路彩燈控制系統(tǒng)?

如何利用FPGA和VHDL語言實現(xiàn)PCM碼的解調(diào)?

MT9M413高幀頻CMOS圖像傳感器原理

用VHDL語言實現(xiàn)3分頻電路

用VHDL語言實現(xiàn)3分頻電路(占空比為2比1)

國外:VHDL數(shù)字電子學第9版-數(shù)字電子技術與VHDL實用方法

使用Quartus和VHDL語言實現(xiàn)的LPC時序的工程文件

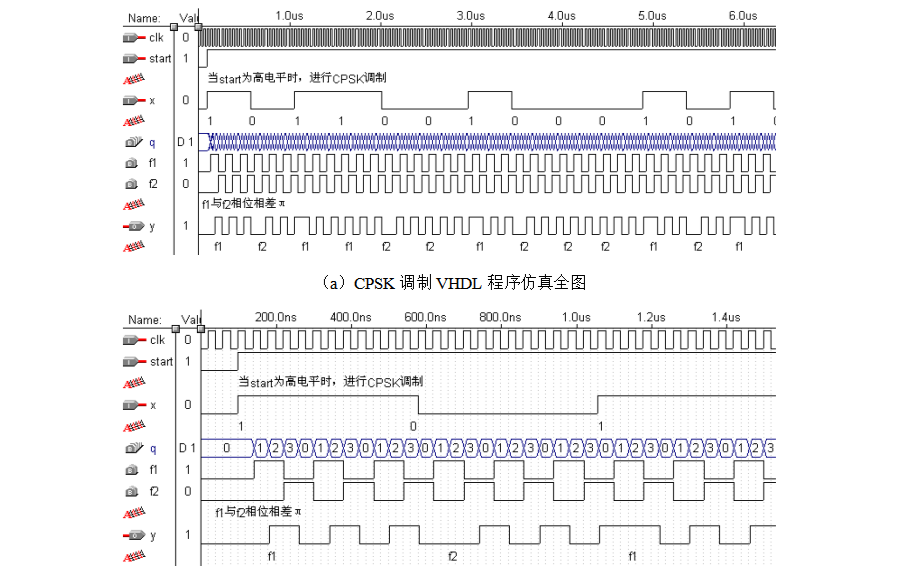

基于VHDL硬件描述語言實現(xiàn)CPSK調(diào)制的程序及仿真

基于VHDL語言實現(xiàn)遠程防盜報警設計

采用MT9M413芯片與VHDL語言實現(xiàn)高幀頻COMS相機電子學系統(tǒng)設計

采用MT9M413芯片與VHDL語言實現(xiàn)高幀頻COMS相機電子學系統(tǒng)設計

評論