在最原始的測試過程中,對集成電路(Integrated Circuit,IC)的測試是依靠有經(jīng)驗(yàn)的測試人員使用信號(hào)發(fā)生器、萬用表和示波器等儀器來進(jìn)行測試的。這種測試方法測試效率低,無法實(shí)現(xiàn)大規(guī)模大批量的測試。隨著集成電路的集成度和引腳數(shù)的不斷增加,工業(yè)生產(chǎn)上必須要使用新的適合大規(guī)模電路測試的測試方法。在這種情況下,集成電路的自動(dòng)測試儀開始不斷發(fā)展。

現(xiàn)在國內(nèi)的同類型產(chǎn)品中,一部分采用了單片機(jī)實(shí)現(xiàn),這部分儀器分析速度慢,難以用于大規(guī)模的測試系統(tǒng)之中,并且在管腳的擴(kuò)展性上受到嚴(yán)重的限制。另一部分使用了DSP芯片,雖然功能上較為完善,但造價(jià)不菲,實(shí)用性能有限。本文的設(shè)計(jì)是基于FPGA實(shí)現(xiàn)邏輯芯片的功能故障測試。由于FPGA芯片價(jià)格的不斷下降和低端芯片的不斷出現(xiàn),使用FPGA作為主控芯片可以更適合于市場,且有利于對性能進(jìn)行擴(kuò)展。實(shí)驗(yàn)表明,該系統(tǒng)設(shè)計(jì)合理,能對被測芯片進(jìn)行準(zhǔn)確的功能測試。

1.邏輯芯片功能測試的基本理論簡介

功能測試也稱為合格-不合格測試,它決定了生產(chǎn)出來的元件是否能正常工作。一個(gè)典型的測試過程如下:將預(yù)先定義的測試模板加載到測試設(shè)備中,它給被測元件提供激勵(lì)和收集相應(yīng)的響應(yīng);需要一個(gè)探針板或測試板將測試設(shè)備的輸入、輸出與管芯或封裝后芯片的相應(yīng)管腳連接起來。測試模板指的是施加的波形、電壓電平、時(shí)鐘頻率和預(yù)期響應(yīng)在測試程序中的定義。

元件裝入測試設(shè)備,測試設(shè)備執(zhí)行測試程序,將輸入模板序列應(yīng)用于被測元件,比較得到的和預(yù)期的響應(yīng)。如果觀察到不同,則表示元件出錯(cuò),即該元件功能測試不合格。

2.測試系統(tǒng)設(shè)計(jì)

該測試系統(tǒng)由下位機(jī)硬件電路和上位機(jī)測試軟件兩大部分構(gòu)成。系統(tǒng)采用功能模塊化設(shè)計(jì),控制靈活,操作簡單,而且采用ROM存儲(chǔ)測試向量表庫,方便以后的芯片型號(hào)添加和擴(kuò)展,有很好的實(shí)際應(yīng)用性。

2.1 硬件設(shè)計(jì)

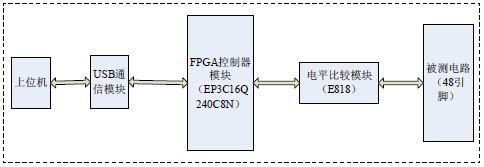

系統(tǒng)硬件主要由FPGA控制器模塊、串口通信模塊、電平比較模塊和測試平臺(tái)模塊構(gòu)成,其結(jié)構(gòu)如圖1所示。

圖1 系統(tǒng)硬件結(jié)構(gòu)圖

控制器模塊選用Altera的FPGA芯片EP3C16Q240C8N,配置芯片選用EPCS4.控制器由使用VerilogHDL硬件語言實(shí)現(xiàn)了包括串口接收模塊、數(shù)據(jù)轉(zhuǎn)換與測試保護(hù)模塊和串口發(fā)送模塊三個(gè)部分的功能設(shè)計(jì)。串口接收模塊完成與串口芯片MAX3232進(jìn)行通信,接收由上位機(jī)發(fā)送來的測試指令;數(shù)據(jù)轉(zhuǎn)換與測試保護(hù)模塊產(chǎn)生實(shí)現(xiàn)一個(gè)類似于D觸發(fā)器的保護(hù)器,對測試端的被測芯片輸出腳進(jìn)行雙保護(hù),保證其在測試后的回測值不受初值影響;串口發(fā)送模塊將測試后得到的數(shù)據(jù)組合為一個(gè)回測寄存器,并按照串口通信協(xié)議將回測數(shù)據(jù)發(fā)送回上位機(jī)。

串口通信模塊選用MAX3232芯片,現(xiàn)串口的全雙工數(shù)據(jù)傳輸。

E818電平比較電路為邏輯功能測試的核心硬件部分。E818是SEMTECH公司專門針對ATE邏輯功能測試而開發(fā)的窗口比較器芯片,它解決了被測對象DUT芯片的雙向輸入數(shù)據(jù)電平要求。

2.2 軟件設(shè)計(jì)

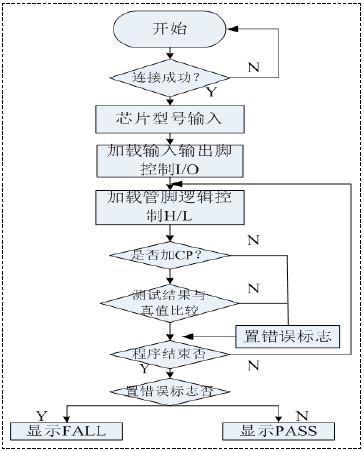

系統(tǒng)軟件上位機(jī)軟件是使用VC++6.0來編寫的。上位機(jī)調(diào)用Access中的測試數(shù)據(jù),經(jīng)串口發(fā)送出后,系統(tǒng)硬件就會(huì)運(yùn)行測試程序。測試結(jié)束后硬件系統(tǒng)會(huì)將測試得到的返回?cái)?shù)據(jù)發(fā)送回上位機(jī)軟件。這時(shí),上位機(jī)軟件接收到返回?cái)?shù)據(jù)后需要對返回?cái)?shù)據(jù)與標(biāo)準(zhǔn)無故障值進(jìn)行對比,以確定此次測試是否正確通過。所以上位機(jī)軟件的功能分為:數(shù)據(jù)庫的調(diào)用,測試矢量的接收和發(fā)送和回測信號(hào)的對比三大部分。系統(tǒng)軟件流程圖如圖2所示。

圖2 系統(tǒng)軟件流程圖

3.系統(tǒng)測試驗(yàn)證

3.1 常規(guī)測試

以芯片74LS08為例,測試流程如下:

(1)使用Microsoft Office Access2003軟件建立測試數(shù)據(jù)庫,并在數(shù)據(jù)庫中建立幾款不同被測芯片的測試數(shù)據(jù)。

(2)在芯片型號(hào)檢索對話框中輸入“74LS08”型號(hào)后,點(diǎn)擊“確定”按鈕即可完成芯片檢索的流程。

(3)自動(dòng)測試模式下,系統(tǒng)將調(diào)用數(shù)據(jù)庫中被測芯片的完整測試數(shù)據(jù),并且完成整個(gè)測試集的循環(huán)測試。

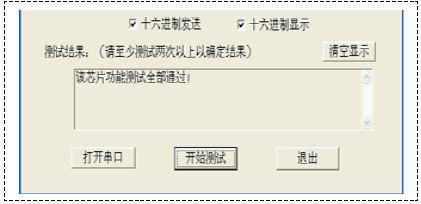

(4)打開系統(tǒng)的串口后,用戶需要將被測芯片放入測試插槽中,然后鎖死插槽以確定被測芯片的引腳與插槽接觸良好。這時(shí)只需要點(diǎn)擊“開始測試”,系統(tǒng)就會(huì)自動(dòng)進(jìn)行循環(huán)測試。在系統(tǒng)插槽中放入74LS08芯片后的測試結(jié)果顯示“該芯片功能測試全部通過”,其顯示如圖3所示。

圖3 常規(guī)測試結(jié)果

3.2 故障測試

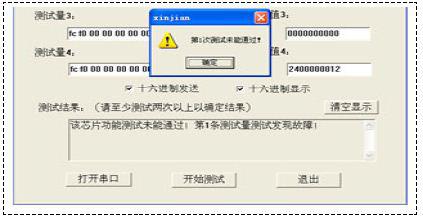

本文以74LS00芯片模擬74LS08芯片的故障片來進(jìn)行一次故障測試,以驗(yàn)證測試系統(tǒng)對故障的識(shí)別。由74LS00芯片和74LS08芯片兩款芯片的引腳數(shù)與引腳分布方式是一樣的。但是在功能上,74LS00芯片為雙輸入四與非門,而74LS08芯片為雙輸入四與門。這就意味著,當(dāng)兩者的輸入值相同時(shí),芯片功能正確情況下的輸出值應(yīng)該正好相反。這樣的輸入輸出關(guān)系可以用來模擬74LS08芯片的全故障情況。這時(shí),用戶需要把74LS00芯片鎖入測試插槽,點(diǎn)擊“開始測試”后的界面如圖4所示。

圖4 故障測試結(jié)果

此時(shí),如果被測芯片依然為74LS00芯片,而從上位機(jī)的數(shù)據(jù)庫中重新調(diào)入74LS00芯片的測試信息進(jìn)行測試,其測試結(jié)果則顯示為“該芯片功能測試全部通過”.其顯示界面如圖3所示。由此可以驗(yàn)證,測試系統(tǒng)對芯片功能故障的判斷十分準(zhǔn)確,并且測試系統(tǒng)可以準(zhǔn)確的識(shí)別存在故障的測試矢量位置,以便于用戶進(jìn)行進(jìn)一步的分析。

4.結(jié)論

本文用FPGA進(jìn)行了一個(gè)芯片功能測試系統(tǒng),并對其功能進(jìn)行了驗(yàn)證,實(shí)驗(yàn)結(jié)果表明該系統(tǒng)測試方法簡單,測試過程迅速,測試結(jié)果準(zhǔn)確。該系統(tǒng)為芯片功能測試提供了一個(gè)很好的解決方案,具有重要的應(yīng)用價(jià)值。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21783瀏覽量

605030 -

集成電路

+關(guān)注

關(guān)注

5391文章

11603瀏覽量

362706 -

萬用表

+關(guān)注

關(guān)注

88文章

2081瀏覽量

128041 -

示波器

+關(guān)注

關(guān)注

113文章

6278瀏覽量

185592

發(fā)布評論請先 登錄

相關(guān)推薦

基于BIST利用ORCA結(jié)構(gòu)測試FPGA邏輯單元的方法

基于FPGA芯片的最小系統(tǒng)設(shè)計(jì)【最新FPGA畢業(yè)設(shè)計(jì)論文】

FPGA的芯片設(shè)計(jì)步驟

高頻RFID芯片的FPGA原型驗(yàn)證平臺(tái)設(shè)計(jì)及驗(yàn)證

如何利用FPGA實(shí)現(xiàn)邏輯芯片的功能故障測試

如何利用FPGA芯片進(jìn)行簡化的PCI接口邏輯設(shè)計(jì)?

利用微處理器實(shí)現(xiàn)ASIC芯片設(shè)計(jì)的功能驗(yàn)證

虛擬FPGA邏輯驗(yàn)證分析儀的設(shè)計(jì)

片上網(wǎng)絡(luò)核心芯片的驗(yàn)證

關(guān)于無源高頻電子標(biāo)簽芯片功能驗(yàn)證的FPGA原型驗(yàn)證平臺(tái)設(shè)計(jì)

Achronix宣布:已完成SpeedcoreTM eFPGA量產(chǎn)驗(yàn)證芯片的全芯片驗(yàn)證

基于雙接口NFC芯片的FPGA驗(yàn)證系統(tǒng)

利用FPGA芯片進(jìn)行邏輯芯片功能測試系統(tǒng)的設(shè)計(jì)與驗(yàn)證

利用FPGA芯片進(jìn)行邏輯芯片功能測試系統(tǒng)的設(shè)計(jì)與驗(yàn)證

評論