引言

隨著社會發展,工業控制及人們日常生活越來越追求精密控制,為滿足這種需求,微控制器得到了快速發展。微控制器(Micro Control Unit,MCU)又稱單片微型控制計算機或單片機。隨著大規模集成電路(LargeScale Integration,LSI)發展,MCU將原本分散的中央處理器(Central Processor Unit,CPU)、隨機存儲器(Ran-dom Access Memory,RAM)、只讀存儲器(Read OnlyMemory,ROM)、輸入/輸出接口(In/Out Ports,I/O)等集中于一塊單晶芯片內,形成一種芯片級計算系統。MCU主要用于控制,MCU構成的系統有實時、快速的外部響應,能迅速采集到大量數據,做出邏輯判斷與推理后實現對被控制對象的參數調整與控制。但是隨著對控制的要求增大,傳統MCU也越來越顯得捉襟見肘。為此使用專用應用集成電路(Application Specific IntegratedCircuit,ASIC)器件在片內實現與傳統MCU相兼容的核心,選用合適的片內總線來連接外設,構成一個兼容傳統MCU平臺,這種方法必會延續傳統MCU的生命力,使其獲得更大的發展。

1 MCU 簡介

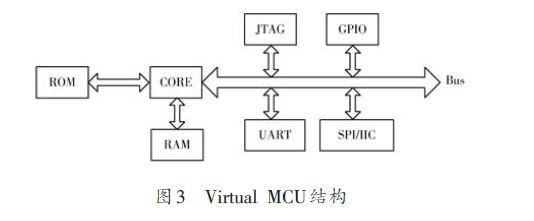

若將4位單片機的出現作為MCU的起點,MCU的發展大致可以分為如下階段:初級階段(1971年-1976年)、8 位低性能階段(1976 年-1980 年)、8 位高性能階段(1980年-1983年)、16位階段(1983年至80年代末)、片上系統(System On-Chip,SoC)階段(1990-)。一個通用的MCU 由ROM、RAM、GPIO、串行設備(UART/SPI/IIC)、計數器/定時器(TIMER)等組成,并通過總線連接,如圖1所示。

傳統MCU 都需要一套指令集結構(Instruction SetArchitecture,ISA)。從現階段主流體系結構講,主要分為復雜指令集(Complex Instruction Set Computer,CISC)和精簡指令集(Reduced Instruction Set Computer,RISC)。

RISC增加了運行速度,大大減小了指令集數目,方便使用多級流水線結構,可增加寄存器數量。AVR單片機就是一款內置FLASH的增強型RISC處理器[4].

另外MCU需要將數據和指令存儲于存儲器中。目前使用最多的兩種存儲器組織結構分別為馮·諾依曼結構(Von Neumann Architecture)和哈佛結構(Harvard Ar-chitecture)。馮·諾依曼結構將處理器指令和數據合并在一起存儲,指向同一存儲器的不同物理地址。哈佛結構將程序指令存儲和數據存儲分開,中央處理器先從程序指令存儲器中獲得指令譯碼后得到數據地址,再由此從數據存儲器中取得數據,并進行下一步操作。哈佛結構的微處理器通常有很高的執行效率。Atmel公司的AVR系列就是采用的哈佛結構。

AVR單片機是由Atmel公司在1997年推出的高速8位MCU,內置FLASH的增強型RISC處理器,可廣泛應用于計算機外部子系統、工業生產和控制、儀器儀表、通信設備、家用電器等各個領域。大部分AVR片上資源豐富:如E2PROM,PWM,RTC,SPI,USART,TWI,ISP,AD,Analog Comparator,WDT等。AVR單片機內嵌高質量的FLASH程序存儲器,擦寫方便,支持ISP和IAP,便于產品的調試、開發、生產、更新。內嵌長壽命的E2PROM可長期保存關鍵數據,避免斷電丟失。片內大容量的RAM不僅能滿足一般場合的使用,同時也更有效地支持使用高級語言開發系統程序,并可像8051單片機那樣擴展外部RAM.

2 FPGA 簡介

ASIC 是指依特定用途而設計的特殊規格邏輯電路。ASIC的最顯著特點是面向特定用戶需求,與通用集成電路相比有更小的體積、更低的功耗、較高的可靠性、較強的保密性和低成本等優點,但因為開發較為復雜,所以研發周期較長。

隨著電子工業技術的發展,ASIC的設計方法變得越簡單,效率越高,可編程ASIC就是一個很有特色的設計分支,它主要利用可編程的集成電路如PLD(Program-mable Read Only Memory)等可編程邏輯電路來設計。

主要特點是直接提供軟件設計編程,完成ASIC電路功能,而不再通過集成電路工藝加工后得到成品。這種方法大大降低了開發周期,且縮小了成本。

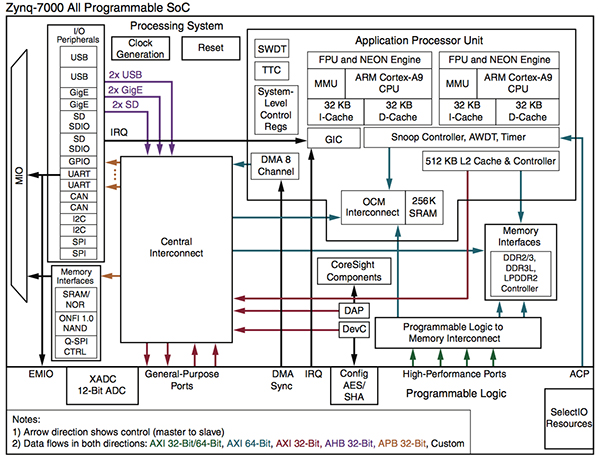

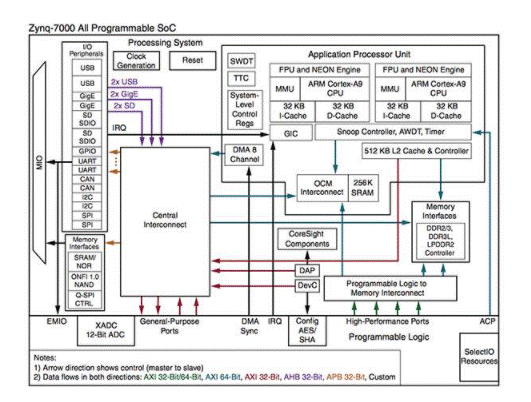

現場可編程門陣列(Field Programmable Gate Ar-ray,FPGA)就是眾多PLD產品中應用最為廣泛的一種,它采用了邏輯單元陣列(Logic Cell Array,LCA),內部包含了可配置的邏輯模塊(Configurable Logic Block,CLB)、輸入/輸出模塊(Input Output Block,IOB)和內部連線(Interconnect)。FPGA采用的是小型查找表來實現組合邏輯的,每個查找表連接到一個D觸發器的輸入端,觸發器再來驅動其他的邏輯電路或者I/O,由此構成即可實現組合邏輯功能又可實現時序邏輯功能的基本邏輯單元模塊,通過內部連線互相連接。FPGA的邏輯是通過向內部靜態存儲單元加載編程數據來實現的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O之間的聯系方式,并且最終決定了FPGA所實現的功能。由于FPGA采用查找表結構,而查找表本質是一個小RAM,所以FPGA內部信息掉電消失,上電需要重新進行配置。FPGA支持多次重復編程。相對于其他的可編程器件,FPGA是ASIC電路中設計風險最小、開發費用最低、周期最短的器件之一。采用高速CMOS工藝,功耗低,可以與CMOS、TTL電平兼容。同時FPGA 的內部邏輯和I/O 資源非常豐富,可以說用FPGA芯片進行小批量生產,對于提高系統集成度、可靠性是很有幫助的。

在眾多PLD廠家中,XILINX公司的產品種類豐富,其開發工具ISE為業界公認的最好的開發工具之一,且其芯片的性價比很高。所以,這里主要使用XILINX公司的產品。XILINX 公司主要FPGA 產品為SPARTAN系列和VIRTEX系列。前者面向低成本應用,滿足一般的邏輯設計要求,后者面向高性能應用,滿足高端要求。文中選擇Virtex-Ⅱ Pro 系列芯片作為開發平臺。

這款芯片含有可編程輸入/輸出塊、可配置邏輯塊、嵌入式RAM塊、數字時鐘管理模塊、專用硬核以及豐富的布線資源。FPGA的設計過程是利用EDA工具將設計輸入轉化為FPGA芯片可運行的過程,開發的一般流程見圖2.

3 Virtual AVR 實現

通過對FPGA和MCU的深入了解,可知使用FPGA的豐富資源來虛擬出MCU是完全可行的。首先,需設計一個總體結構,如圖3所示。ROM用于存放被執行程序及二進制代碼,RAM 為運行內存,用總線將VirtualMCU Core與各外設相連。使用該結構可簡化設計,無需對外設重復設計,只要使Virtual MCU Core滿足同一接口即可。

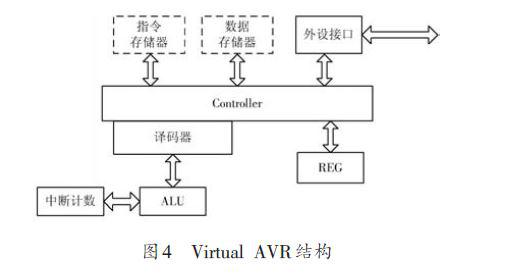

Virtual MCU Core由幾部分構成:算術邏輯單元,運算的主要單元;譯碼器,由二進制文件判斷指令類型并獲得源操作數和目的操作數等;寄存器,用于參加運算和存儲某些中間值等。

Virtual AVR Core 以ATmega103處理器為參考,核心采用RISC結構,3級流水線結構,因為是哈佛結構,所以分為數據存儲器和指令存儲器。它的處理器核心如圖4所示。同時ATmega103共有130條指令,每條指令都是固定結構,為16 位。在該設計中,移植了Open-Cores開源組織的8位AVR核,它支持3級流水線,兼容標準AVR微處理器。

ALU的實現采用模塊化設計,共分為控制模塊、加減法模塊和乘除法模塊。3級流水線設計如下:

stage0:FETCH,給出指令地址,并讀取相應的指令,主要由譯碼機構負責;stage1:ALU/MEM,ALU運算,或數據存儲器操作,讀數據存儲器時,在地址總線上給出正確的值,當寫數據存儲器時,不僅需要提供正確的地址,還需要在數據總線上提供正確的數據,主要由運算機構和總線控制機構負責。

Stage2:LOAD,從數據線上獲取數據,存至寄存器中,主要由寄存器機構負責。

在一個系統中光有處理器是不夠的,需要有豐富的外設來滿足各種控制要求或數據傳輸功能,而片內總線便是將處理器與總線連接的重要途徑。文中采用Sili-core的Wishbone總線進行設計,具有簡單、開放、高效和方便實現等特點,且完全開放并沒有專利保護。Wish-bone有四種連接模式:點對點、數據流、共享總線和十字交叉互聯。文中使用共享總線連接方式,其中充當Master為Virtual Core,而外設為Slaver.

為使Virtual Core能與外部器件進行通信,需要外設的支持。外設按數據流類型分為串行和并行,常用的串行外設有SPI、I2C、UART 等,常用的并行外設有GPIO等。

4 硬件支持與測試

硬件環境主要分為兩部分:第一部分為核心板,用以支持Virtex-Ⅱ Pro的運行;第二部分為底板,主要為添加外設環境,豐富系統的功能。選用XC2VP50FFG1152芯片作為核心的FPGA,在外圍又添加了DDR和SDRAM,方便自由選擇存儲器類型。FP-GA掉電后,內容自動消失,每上電需要重新配置,為讓FPGA 上電后自動配置,需加一片PROM,使用XCF32P.FPGA采用并行主模式。底板上則是增加大量外設:UART、PS2、VGA、ETHERNET、VIDEO、A/D、D/A、SD、USB等。

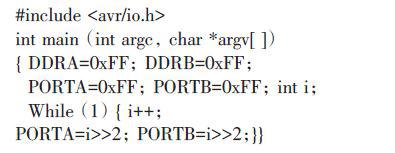

Virtual Core執行的程序都是固化在ROM中,為達到測試要求,要多次更新ROM中內容,為此使用嵌入式開發套件(Embedded Development Kit,EDK)來開發一個測試工具。首先將BRAM配置為雙端口RAM,一端口給Virtual Core來進行讀取操作,一端口給EDK,來更新程序存儲器。同時EDK也可提供簡單的控制任務,如重啟Virtual Core 等,EDK 使用UART 和計算機進行操作。為方便控制,設計一個較為簡單的PC端串口程序,用于將EDK與PC交互,主要是將用戶的命令或文件經串口發送至EDK,如圖5所示。搭建一個簡易測試系統,使用ISE工具,進行綜合布局布線,其資源消耗如圖6所示。編寫一個跑馬燈程序,代碼如下:

使用WINAVR-GCC 編譯工具,編譯生成HEX 文件,后再轉化為BIN文件,將該BIN文件通過EDK組建更新ROM,觀察硬件LED,如圖7所示,其正常工作,Vir-tual AVR得到驗證。

5 結語

隨著MCU 應用范圍越來越寬,對MCU 要求也提高,尤其目前MCU逐漸進入SoC時代,IP核復用將成為主流設計方法。為使老一代MCU延續生命力,開發其兼容IP核,不僅能將以往代碼迅速移植到新系統,且可加快新系統開發,將以往很多分立器件用邏輯功能實現,集成于ASIC中,降低外圍硬件電路的設計。文中從模擬MCU核開始,闡述了用FPGA來虛擬出傳統MCU的設計原理和方法,適度改變內部結構,添加Wishbone總線,替代傳統MCU片內總線,來完成MCU核與外設的連接,使傳統MCU變的更靈活。結果表明,實現了既定目標,與標準的微控制器兼容,系統運行穩定。該方法延續了傳統微控制器的生命力,能使其得到更大發展。由于Wishbone總線支持多主設備,今后可在一個FPGA 中集成多個MCU核,對于性能的提升將是質的飛躍。

-

處理器

+關注

關注

68文章

19404瀏覽量

231085 -

FPGA

+關注

關注

1630文章

21796瀏覽量

605809 -

mcu

+關注

關注

146文章

17316瀏覽量

352535 -

微處理器

+關注

關注

11文章

2274瀏覽量

82752

發布評論請先 登錄

相關推薦

FPGA與MCU的應用場景

工業FPGA與MCU之爭,鹿死誰手?

基于雙核MCU提高系統性能

汽車電子MCU中采用抗EMI的設計方法介紹

如何將MCU與FPGA進行配對呢

Jlink虛擬出來的串口有何作用

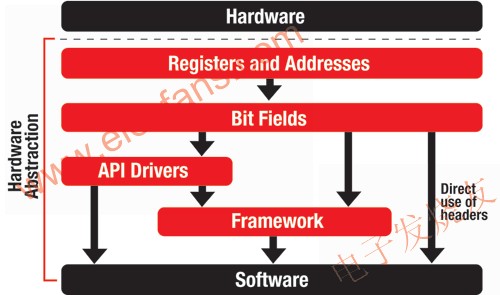

體驗全新的MCU軟件方法

MCU對FPGAs提高系統效率

如何將MCU與FPGA進行配對以達到提高系統效率的目的

AGM MCU+FPGA

如何將MCU與FPGA進行配對達到提高系統效率的目的?

FPGA MCU FSMC通信接口——NAND Flash模式

采用FPGA虛擬出傳統MCU的設計原理和方法,提高MCU的性能

采用FPGA虛擬出傳統MCU的設計原理和方法,提高MCU的性能

評論