FPGA廠商不斷采用更先進的工藝來降低器件功耗,提高性能,同時FPGA對供電電源的精度要求也越加苛刻,電壓必須維持在非常嚴格的容限內(nèi),如果供電電壓范圍超出了規(guī)范的要求,就有會影響到FPGA的可靠性,甚至導(dǎo)致FPGA失效。

無論是Intel (Altera)FPGA還是Xilinx FPGA均在數(shù)據(jù)手冊中明確提出了電源精度要求,其中要求最高的是內(nèi)核和高速收發(fā)器的供電。舉例來看,Intel公司的Cyclone V、Cyclone 10 GX、Arria10、Stratix 10的電源精度要求在±30mV以內(nèi)。

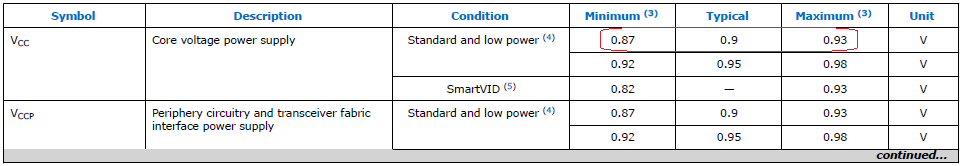

Arria10的core和transceiver數(shù)據(jù)手冊上的供電要求(±30mV):

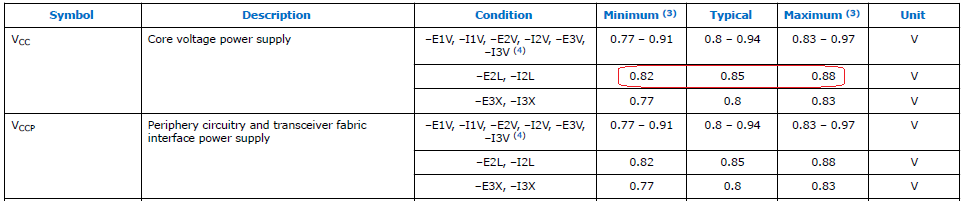

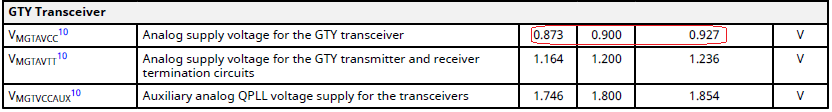

Stratix10的core和transceiver數(shù)據(jù)手冊上的供電要求(±30mV):

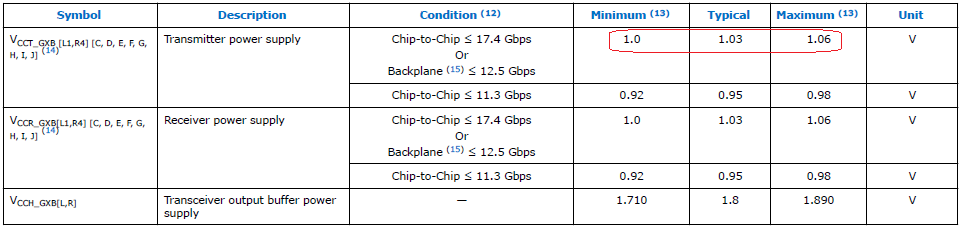

如果Stratix10需要支持26.6G transceiver時,收發(fā)器供電精度要求 ±20mV以內(nèi):

Xilinx公司的Artix 7、Kintex7、Virtex 7等器件電源精度要求也是在±30mV以內(nèi),KU+、VU+器件要求電源精度必須達到±22mV以內(nèi)。

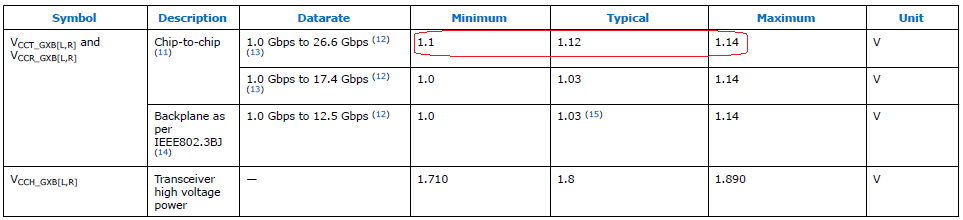

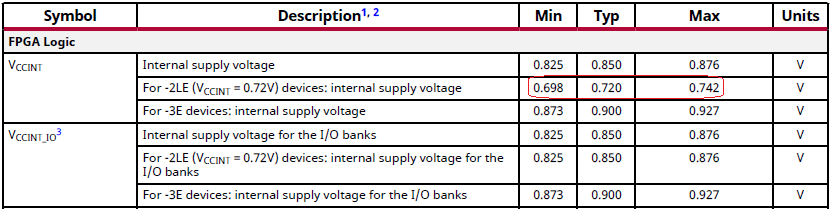

Kintek Ultrascale+的core和transceiver數(shù)據(jù)手冊上的供電要求(±22mV):

由此可見,新一代FPGA的供電精度都在±20-30mv左右,已經(jīng)是單板中對電源精度要求最為苛刻的器件之一了。

由于輸出精度都是理論計算值,并沒有考慮單板PCB布線和其他外部設(shè)備引入的干擾和誤差,因此實際設(shè)計產(chǎn)品時,電源輸出精度不但必須符合數(shù)據(jù)手冊中的要求,還必須預(yù)留一定的余量,通常設(shè)計中,我們還會保留50%-100%余量,以保證系統(tǒng)長期可靠工作。

電源的穩(wěn)態(tài)直流精度及計算方法

供電電源的穩(wěn)態(tài)直流精度主要取決于兩個因素:電壓調(diào)整精度和輸出電壓紋波。這里有一個誤區(qū),很多工程師只通過DC-DC數(shù)據(jù)手冊上的電壓輸出精度來判斷器件是否符合要求,其實這是不正確的。 首先很多DC-DC需要外部反饋電阻來決定最終的輸出電壓,數(shù)據(jù)手冊上的電壓調(diào)整精度是指芯片本身的輸出精度,并沒有計算反饋電路引入的偏差。其次,器件數(shù)據(jù)手冊上的電壓輸出精度并不包含輸出電壓紋波,必須將兩者疊加計算才能得到正確的直流穩(wěn)態(tài)精度。

正確的電源穩(wěn)態(tài)直流精度的計算公式如下:

電源直流穩(wěn)態(tài)精度 =器件輸出精度(這里要求全溫度,全負載時的精度,很多器件手冊只給出典型值,因此要小心)+ ? 紋波 + 外部反饋電阻精度引入的誤差。

高精度電源對減低FPGA功耗的作用

除了電源精度影響整個系統(tǒng)的穩(wěn)定性和可靠性,更高精度的電源還可以幫助我們降低系統(tǒng)功耗。

我們舉一個例子,一個FPGA推薦的典型工作電壓為0.85V,最高工作電壓為0.88V,最低工作電壓為0.82V, 假設(shè)供電DC-DC實際穩(wěn)態(tài)直流精度是±30mV ,那么DC-DC必須正好工作在0.85V,如果電壓更低,就會低于FPGA對電壓下限的要求。

-

電源

+關(guān)注

關(guān)注

184文章

17774瀏覽量

250767 -

FPGA

+關(guān)注

關(guān)注

1630文章

21759瀏覽量

604291 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3438瀏覽量

106068

原文標(biāo)題:關(guān)于FPGA電源精度要求

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

#電機驅(qū)動 Current mode DC-DC和DCAP2 mode DC-DC設(shè)計實例

DC-DC基礎(chǔ)入門教程 Advanced DC-DC Converters

DC-DC工作原理

嵌入式DC-DC轉(zhuǎn)換器怎么選擇?

FPGA對DC-DC精度的要求是什么?

如何選擇合適的DC-DC、LDO器件?

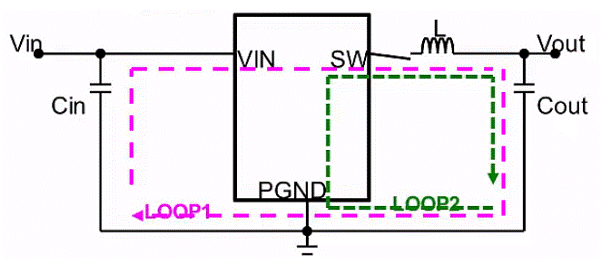

DC-DC的layout有哪些原則

LDO和DC-DC有什么不同?

什么是DC-DC

負載點DC-DC轉(zhuǎn)換器解決電壓精度、效率和延遲問題

pwm dc,如何更好的設(shè)計PWM DC-DC系統(tǒng)?

DC-DC PCB layout指導(dǎo)說明

DC-DC的PCB設(shè)計

DC-DC電源設(shè)計分析及使用注意

DC-DC的PCB設(shè)計注意的點

FPGA對DC-DC精度的要求不斷提升

FPGA對DC-DC精度的要求不斷提升

評論