經過上兩篇文章的閱讀,大家應該清楚自己的CPU大致是如何處理數據的,而又是如何執行指令的。我們現在來在簡略的說一下流水線CPU的設計。(源碼在CSDN下載頁,請自取)

流水線CPU的基本數據通路和單周期沒有什么太大區別,而且也是每個時鐘周期都有一條指令執行結束。但是他又和多周期CPU一樣一條指令需要多個時鐘周期完成。而同時使這兩條條件同時滿足的就是流水線技術了。先上一張圖

由于在多周期CPU中,比如我們正在第三級執行第五條指令的執行操作,對于整個數據通路來講,其它幾級都是空閑狀態,那我們為了提高CPU的工作效率,就讓他提前后邊指令的其他幾級操作。這樣一來,我們的CPU就像工廠內的流水線一樣,每一級都在工作,大大提升了他的工作效率。

在設計中,流水線CPU甚至會比多周期CPU更好實現。由于數據是一級一級向下流,我們都無需進行狀態機的狀態轉移來控制,只需要讓數據與他的控制信號同步流向器件。每一個時鐘周期數據都是從上一級流向下一級。而對應的寄存器就是在每個時鐘上升沿都讀出舊數據,寫入新數據。

但是在流水線CPU中,分支跳轉語句變成了一個難點,當指令發現是分支跳轉指令時,輸出branch信號,后等待ALU輸出比較值是否相等。如果相等,進行跳轉。但是跳轉時,我們的流水線已將后三條指令讀入并操作了一部分了。這時我們便需要清空存儲器。或者我們也可以當檢測到branch信號時CPU停止讀入指令,直到判斷結果輸出時在進行跳轉。、

流水線CPU是非常好用的CPU,在我們后續的程序編寫的時候基本上都會使用流水線CPU,偶爾也會用多周期CPU。

-

FPGA

+關注

關注

1629文章

21759瀏覽量

604283

發布評論請先 登錄

相關推薦

工業讀碼器解決方案在自動化流水線上掃描條碼的應用

SMT流水線布局優化技巧

行云流水線 滿足你對工作流編排的一切幻想~skr

ADS5413 CMOS流水線模數轉換器(ADC)數據表

固定式的掃碼器在SMT流水線中的使用

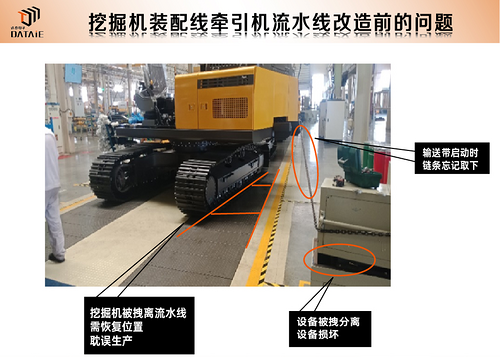

牽引機和挖掘機裝配流水線自動互鎖防呆系統無線通訊應用

自制CPU(三)流水線

自制CPU(三)流水線

評論