介紹

在多個大趨勢的推動下,推動世界對半導體需求的技術繁榮依然強勁。無線基礎設施、物聯網、人工智能、數據中心和電動汽車是推動對先進半導體 IC 需求增加的應用示例。隨著每個單獨的 IC 中包含更多功能,測試要求也會增加,降低成本變得更具挑戰性。半導體制造商如何提高其最終產品的復雜性,同時降低測試成本?

測試系統未標準化

從廣義上講,半導體開發過程包括設計、制造和測試。今天,IC 設計人員使用 EDA(電子設計自動化)軟件工具。這些工具是標準化的,大大簡化了設計過程。晶圓的制造設備在一定程度上也是標準化的,因為許多工藝和設備是代代相傳的。ATE 系統不能這樣說。缺乏標準和 IC 復雜性的增加導致測試成本上升。研究表明,封裝和測試占產品總成本的 50% 到 70% 之間。

降低測試成本

降低測試成本的一個明顯方法是采用更高的并行度并同時測試多個部分。每當 ATE 系統并行測試更多部件時,吞吐量就會提高。例如,如果之前的測試平臺可以并行測試四個設備,總測試時間為 10 秒,那么每個設備測試是 2.5 秒。使用每秒 0.02 美元的假設成本,那么每個設備都有 0.05 美元的測試成本。通過將 ATE 系統升級到八進制站點甚至 16 個站點的測試儀,測試成本顯著下降,分別為 0.025 美元和 0.0125 美元。與 16 個站點的測試設置相比,這項 75% 的測試成本節省比原始測試成本節省了 0.0375 美元。

接下來,想象一下總測試時間是否可以減少一半。由于 ATE 生產車間測試工程師將最大限度地利用資源來測試器件,因此減少測試時間的方法是提高驅動信號到被測器件 (DUT) 和比較器信號返回到 FPGA 的速度。驅動器和比較器 IC 所在的引腳電子速度提高了 2 倍,將測試時間縮短了一半。計算測試成本的數學與前面的示例一樣簡單。測試 16 臺設備需要 5 秒,而不是 10 秒。這意味著每臺設備的測試成本為 0.00625 美元,是 0.0125 美元的一半。雖然實際測試時間各不相同,但這個假設示例清楚地展示了更快系統和更高密度卡的潛在節省。

更高的密度和速度

前面提到的引腳電子驅動板具有驅動器和比較器 IC。圖 1中的 ATE 框圖顯示了MAX32007所在的位置(DCL + DAC + SWITCHES 盒)。MAX32007 是 ADI 最新發布的 8 通道 3Gbps 引腳驅動器。

圖 1. 通用 ATE 系統框圖。

高密度、八通道、高速 3Gbps MAX32007 具有集成的 14 位電平設置 DAC、電纜下垂補償和壓擺率控制,可優化 DUT 的波形。

電纜下垂補償

由于 PCB 上的長跡線和/或長或有損耗的同軸電纜,驅動到 DUT 的波形和返回信號可能會衰減或退化。當波形受到這種影響時,有效數據速率會降低,或者更糟的是,數據無法使用,從而影響測試的吞吐量和成本。MAX32007 在輸出波形中加入了長 (CDRPL) 和短 (CDRPS) 雙時間常數,通過受控量的過沖和下沖來恢復圓潤邊沿。

圖 2. 驅動器電纜下垂補償的概念表示。

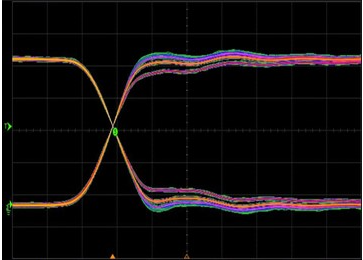

補償量可以通過一個 3 位內部寄存器從 0 到 10% 進行編程。圖 3中的示波器顯示了電纜下垂補償如何幫助信號保真度克服 24 英寸 50Ω 同軸電纜上的劣化波形的示例。外部綠色跡線表示應用到波形的 10% 補償,內部跡線顯示 0% 補償。

圖 3. 電纜下垂補償的范圍拍攝。

結論

隨著半導體 IC 不斷跟上最新的技術需求,測試它們所需的自動化測試設備也必須如此。Pin 電子驅動器在處理這種技術激增方面發揮著關鍵作用,更高密度和更高數據速率可實現下一代設備的高吞吐量和更低的測試成本。

審核編輯:郭婷

-

FPGA

+關注

關注

1630文章

21761瀏覽量

604384 -

驅動器

+關注

關注

53文章

8259瀏覽量

146635 -

半導體

+關注

關注

334文章

27527瀏覽量

219926

發布評論請先 登錄

相關推薦

舵機在自動化設備中的應用

驅動器在自動化中的應用 驅動器的類型及特點

伺服驅動器在工業自動化中的應用

選擇工業自動化設備時有哪些關鍵考慮因素?

變頻驅動器的結構和應用

DC電源模塊在工業自動化中的應用案例分析

Pin電子驅動器在自動化測試設備中應用分析

Pin電子驅動器在自動化測試設備中應用分析

評論