0 引言

雷達導引頭是反輻射導彈(ARM)的關鍵部件,被譽為ARM的“眼睛”,主要功能是完成對輻射源的分選、截獲和跟蹤,其技術性能將直接影響反輻射導彈的作戰性能[1]。隨著雷達技術的提高,超寬頻帶導引頭進一步擴大頻率覆蓋范圍,使反輻射導彈幾乎能覆蓋所有頻段的各種輻射源[2]。傳統導引頭在分選識別多頻帶輻射源時,一般流程是AD采樣處理后直接傳送超寬帶頻譜至數字信號處理部分,再對寬帶數據進行抽取和濾波。隨著導引頭頻率覆蓋范圍的進一步擴大,傳統處理流程不僅會造成效費比總體偏低[3],而且傳統并行LVDS傳輸接口存在大量數據連線復雜[4]等難題,難以迎合現代反輻射導引頭寬頻帶、小型化的發展趨勢。

為了提高導引頭總體效費比,簡化其物理互聯以趨向小型化,提出了一種基于DDC模塊和JESD204B接口的導引頭接收電路設計方案。一方面,通過ADC內置的DDC模塊對數字化后的寬帶數據進行篩選、抽取和濾波之后再傳送給信號處理部分,提高了導引頭對多種頻帶雷達信號的處理效費比;另一方面,采用JESD204B高速串行接口作為數字信號傳輸接口,在保證單通道數據傳輸速度的同時,極大地簡化了數據連線復雜度,為系統小型化設計奠定了基礎。

1 方案設計

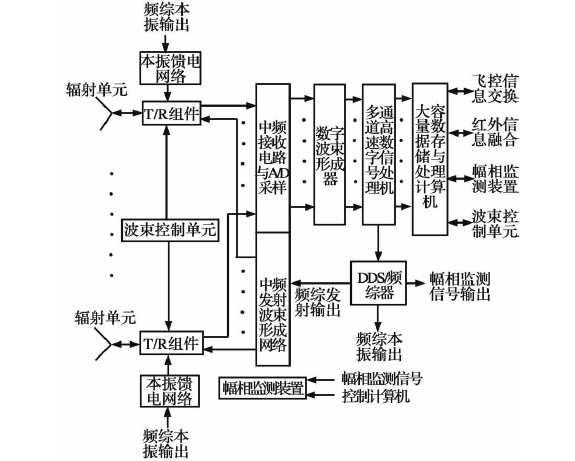

典型被動雷達導引頭由天線、接收機、信號分選與選擇系統、指令控制放大器等組成[5]。圖1是16通道導引頭接收系統框圖。超寬頻帶接收天線接收超寬頻帶雷達輻射信號,傳輸至射頻信號調理電路,射頻信號調理電路的作用是防止接收輻射信號中噪聲、雜波影響模數轉換器的轉換精度。模數轉換器將輸入模擬信號進行采樣轉換成數字信號,再由模數轉換器所帶的DDC模塊進行抽取和濾波,最后通過JESD204B高速接口送給數字信號處理電路,通常是帶JESD204B接口的高性能FPGA。該系統的導引頭接收電路由16通道的射頻信號調理電路,8片帶DDC模塊和JESD204B接口的雙通道模數轉換器以及8片帶JESD204B接口的FPGA組成。

1.1 高速模數轉換芯片ADC32RF45

設計的反輻射導引頭接收電路選擇采用美國TI公司的雙通道、14位3.0GSPS模數轉換芯片ADC32RF45,支持輸入頻率高達4 GHz及以上的射頻(RF)采樣,并且模擬單通道能夠同時處理并輸出帶寬為75 MHz~600 MHz范圍內的雙基帶信號。如圖2所示,其內部集成了模擬信號緩沖模塊、高速14位ADC、自動增益控制模塊、數字下變頻模塊和JESD204B接口模塊。

1.2 片上數字下變頻器

片上數字下變頻器由混頻器、數控振蕩器和抽取濾波器3部分組成,其結構框圖如圖3所示,主要功能是從采樣轉換輸出的高速寬帶信號中提取到基帶信號,同時對基帶信號進行抽取和濾波,降低信號速率,以滿足后續模塊的實時處理[6]。本文中所采用ADC的每條模擬通道后面都有一組數字下變頻器,可以在單通道模擬載波輸入中實現雙基帶信號提取與處理。

1.3 JESD204B接口

ADC32RF45的數字輸出接口為JESD204B子類1接口,模擬單通道最高同時支持四路鏈路,每一條傳輸鏈路帶寬最高為12.5 Gbps。ADC32RF45芯片中的JESD204B接口的單模擬通道輸出鏈路數取決于前端采樣率和總抽取階數的配置,可以被配置為1線、2線和4線模式。

2 系統設計與應用

本文中反輻射導引頭系統以TI公司模數轉換芯片ADC32RF45作為導引頭接收電路核心,采用賽靈思K7系列FPGA作為后端數字信號處理單元,通過軟件仿真和實驗測試驗證了基于數字下變頻處理和JESD204B接口的模擬單通道接收方案的可行性與優點。

2.1 寬帶接收電路設計

為了初步驗證方案的可行性,設計了基于ADC32RF45接收電路,具體實現方式為將ADC32RF45開發模塊與單片FPGA開發套件通過專用連接插件相連。該接收電路采用FPGA作為數字信號處理中心,利用其內部高速收發器GTX實現了JESD204B接口,使得FPGA完成了對模擬前端ADC32RF45單路輸出數據的接收。

2.2 數字下變頻器應用分析

在高速采集系統中,高采樣率和輸入帶寬的ADC為后端數字信號處理單元提供了較寬的可見頻譜[7]。在以往的數字下變頻結構設計中,很少在考慮多級濾波器設計的同時,引入多帶寬設計的思路來擴展數字下變頻器的適用范圍[8]。針對反輻射導引頭工作特點,需要實時檢測多個窄帶數據以實現對多種型號雷達的制導攻擊,本文采用片上數字下變頻器實現了對多帶寬基帶信號的篩選、抽取與濾波。

ADC數字化后的多頻帶復合射頻信號對應兩條下變頻鏈路,分別乘以兩個零相位、頻率為目標頻帶中心頻率的正弦信號,將感興趣頻帶中心變頻到零赫茲。在將感興趣帶寬信號降頻之后,再通過帶有抽樣功能的低通濾波器濾去不需要的頻率成分,保留感興趣且對后續信號處理有用的頻段信息,使得后端資源利用率得到優化。

2.3 JESD204B接口應用分析

當前并行輸入/輸出技術存在帶寬限制,例如CMOS或LVDS,迫使數據轉換器的管腳數目越來越多[9]。當導引頭接收電路實現多頻帶采樣處理功能,應用并行LVDS接口不僅難以負荷高達吉赫茲的瞬時帶寬,而且使得模擬前端與后端FPGA之間連線布局復雜。為了提高數據傳輸速率,降低導引頭內部電路復雜度,使導引頭整體趨向小型化,本設計采用JESD204B協議。JESD204協議于2006年首次提出,僅支持單一通道的數據傳輸,傳輸速度為3.125 Gb/s,其升級版JESD204A 協議增加了對多路串行通道傳輸的支持能力,而最新版JESD204B增加了對確定延時的條款并將傳輸速度進一步提高到了12.5 Gb/s[10]。鏈路建立及傳輸具體流程圖如圖4所示。

本設計以賽靈思公司免費的基于GTX的JESD204 PHY IP核作為設計基礎,使用VIVADO軟件設計上層硬件邏輯。JESD204B鏈路間同步分為三個階段,字同步、幀同步和數據傳輸。在字同步階段,FPGA使用GTX中的時鐘數據恢復技術從ADC輸出數據流中定位控制字。在幀同步階段,為了對齊所有鏈路,作為接收方,FPGA需要檢驗鏈路參數和通過系統參考信號建立幀數據與多幀數據邊界。在數據傳輸階段,本設計通過FPGA內部邏輯設計實現了數據流中控制字符的替換,完成原始數據還原。

3 測試結果與分析

3.1 JESD204B接口測試

利用Xilinx提供的Integrated Bit Error Ratio(IBERT)對高速串行通信測試,不僅使測試更加方便快捷,更有利于快速檢測、改善FPGA板卡上高速吉比特收發器的通信質量[11]。通過VIVADO軟件內部誤碼分析眼圖,“眼”睜開狀態明顯,誤碼率量級為e-9,屬于正常范圍,證明鏈路信號完整性良好。

同理,Xilinx公司的FPGA芯片具備內部邏輯分析工具,通過JATG接口實現與FPGA芯片之間數據的連接[12],通過配置使ADC進入JESD204B鏈路自測試模式,即在不采樣的情況下ADC輸出測試信號波形。通過VIVADO軟件內部邏輯分析工具抓取經過單鏈路JESD204B接口接收的測試信號如圖5所示,正弦波形顯示良好,由此可證明單鏈路JESD204B接口可以正確解析信號。

3.2 基帶篩選仿真

在默認采樣率fs為3 GSPS的情況下,通過MATLAB軟件驗證利用兩個數字下變頻器從雙頻帶載波信號提取兩個基波信號方案的可行性。采用頻分復用調制,利用信號發生器AMU200將帶寬為50 MHz和140 MHz的基帶信號分別調制到中心頻率分別為400 MHz和1.2 GHz的正弦載波,模擬出經過采樣轉換后的雙頻帶載波信號。仿照ADC內部下變頻模塊組成建立模型,設置本振頻率NCO2為400 MHz和NCO1為1.2 GHz,并且每一個抽取濾波器的抽取系數為4,因此每一個數字下變頻器的總抽取系數為8,經過數字下變頻后輸出基帶信號的截止頻率為0.0625×fs。將輸入雙基帶載波信號和輸出的兩個基帶信號分別進行快速傅里葉變換,得到如圖6、圖7和圖8所示頻譜。

由仿真圖分析可知,仿照ADC內部單通道數字下變頻器所建立的數字下變頻模型可以實現雙基帶信號提取濾波功能,證明設計方案具有可行性。

4 結論

本文設計了基于數字下變頻和JESD204B接口的導引頭接收電路,介紹分析了數字下變頻器和JESD204B接口在反輻射導引頭領域的應用優勢。針對反輻射導引頭研制領域寬頻帶、多載波和小型化的發展趨勢,靈活應用新型高速ADC中數字下變頻器,寬帶導引頭接收可以輸入帶寬高達4 GHz,在導引頭前端實現了頻帶篩選,能夠完成75 MHz~600 MHz帶寬范圍內多個不同的基帶信號的數字下變頻,與傳統方案相比,提高了后端信號處理效率。利用基于高速收發器GTX的JESD204 Phy IP實現了單通道JESD204B接收接口,與并行傳輸接口相比,簡化了板級布局連線,同時保證了數據高速傳輸。經過軟件功能仿真以及硬件實際測試,初步驗證了方案設計的可行性,為研制寬頻帶、小型化反輻射導引頭奠定了一定技術基礎。

-

ARM

+關注

關注

134文章

9105瀏覽量

367916 -

模數轉換

+關注

關注

1文章

216瀏覽量

36888 -

DDC

+關注

關注

2文章

91瀏覽量

37104 -

雷達導引頭

+關注

關注

1文章

5瀏覽量

7001

發布評論請先 登錄

相關推薦

怎么利用FPGA+DSP導引頭信號處理FPGA?

FPGA+DSP導引頭信號處理中的FPGA技術該怎么實現?

如何利用FPGA+DSP導引頭信號處理?

一種通用PD導引頭目標模擬器的設計

相控陣雷達導引頭捷聯去耦數字平臺設計

相控陣雷達導引頭的介紹及其數字平臺設計

如何進行相控陣雷達導引頭收發系統的設計

微帶天線的功率容量能否滿足相控陣導引頭的要求?

解析多種雷達導引頭和有源相控陣雷達

自研國產化圖像處理板在導引頭的應用

可編程導引頭模擬器怎么用

關于一種小型、高效反輻射導引頭接收方案的設計

關于一種小型、高效反輻射導引頭接收方案的設計

評論