隨著SerDes芯片集成度、復雜度、傳輸速率的不斷提高,傳統的自動化測試系統已經無法滿足SerDes測試速率需求。但通過Nautilus UDI方案的導入,成功實現了32 Gbps SerDes的量產測試。那么,Nautilus UDI方案是如何實現包括UDI結構、輸入時鐘設計、Load board設計、socket選型等多個測試環節高速SerDes測試的呢?

引言

隨著信息通信技術的發展,對數據傳輸的速率、效率要求越來越高,傳統并行接口的速度已經達到一個瓶頸,速度更快的串行接口是技術發展趨勢。于是原本用于光纖通信的SerDes技術成為了高速串行接口的主流。

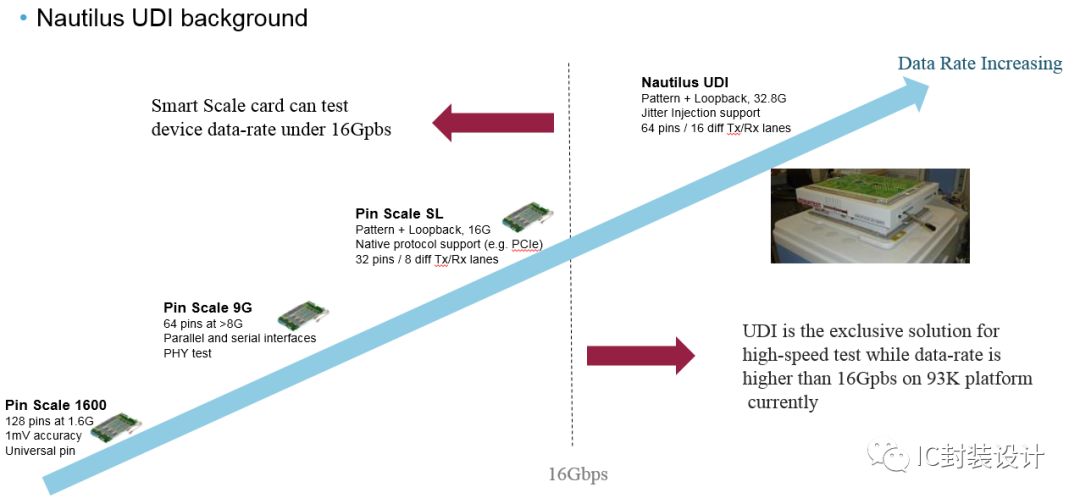

SerDes自動化測試受制于測試系統傳輸速率限制及硬件設計,導致SerDes測試遠遠落后SerDes芯片的發展。愛德萬經過多年的研發及高速IO測試經驗的積累,基于93000平臺研發出了一套完善的,最高速率支持到32.8 Gbps測試方案(Nautilus UDI),彌補了16G-32.8 Gbps SERDES高速IO自動化測試的空白。如圖1:93000平臺提供了支持最高速率速率為9 Gbps, 16 Gbps, 32.8 Gbps多種傳速速率SerDes測試方案。

圖1:93000 0-32G傳速速率測試方案

1 SerDes

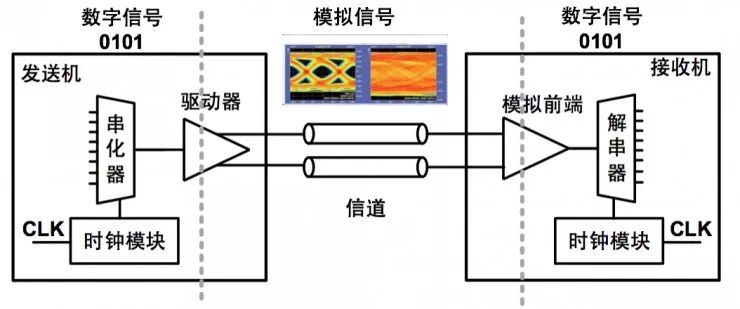

SerDes是英文Serialize (串行器)/De-Serialize (解串器) 的簡稱。它是一種主流的時分多路復用(TDM)、點對點(P2P)的串行通信技術。即在發送端多路低速并行信號被轉換成高速串行信號,經過傳輸媒體(光纜或銅線),最后在接收端高速串行信號重新轉換成低速并行信號[1]。日常見到的消費類電子產品中的PCIE、SATA等接口即是SerDes技術的應用案例。

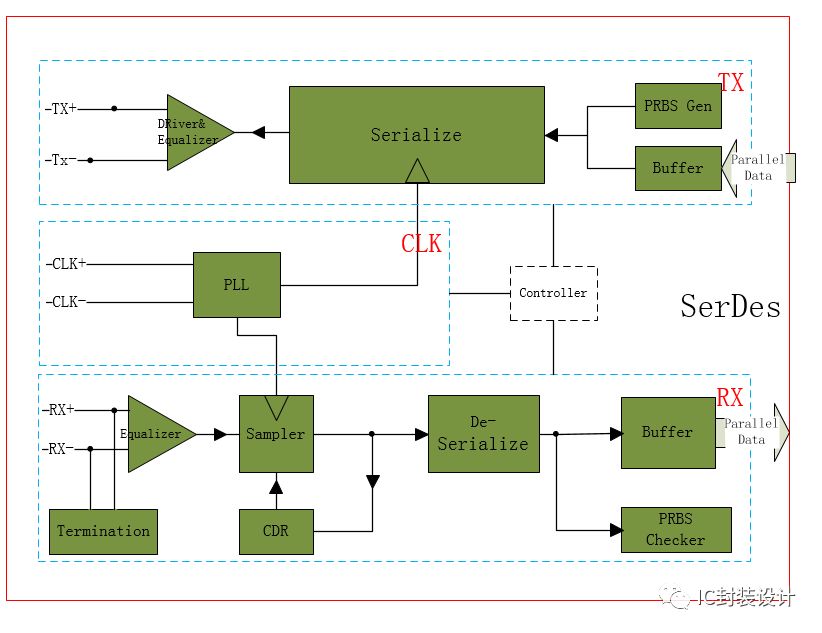

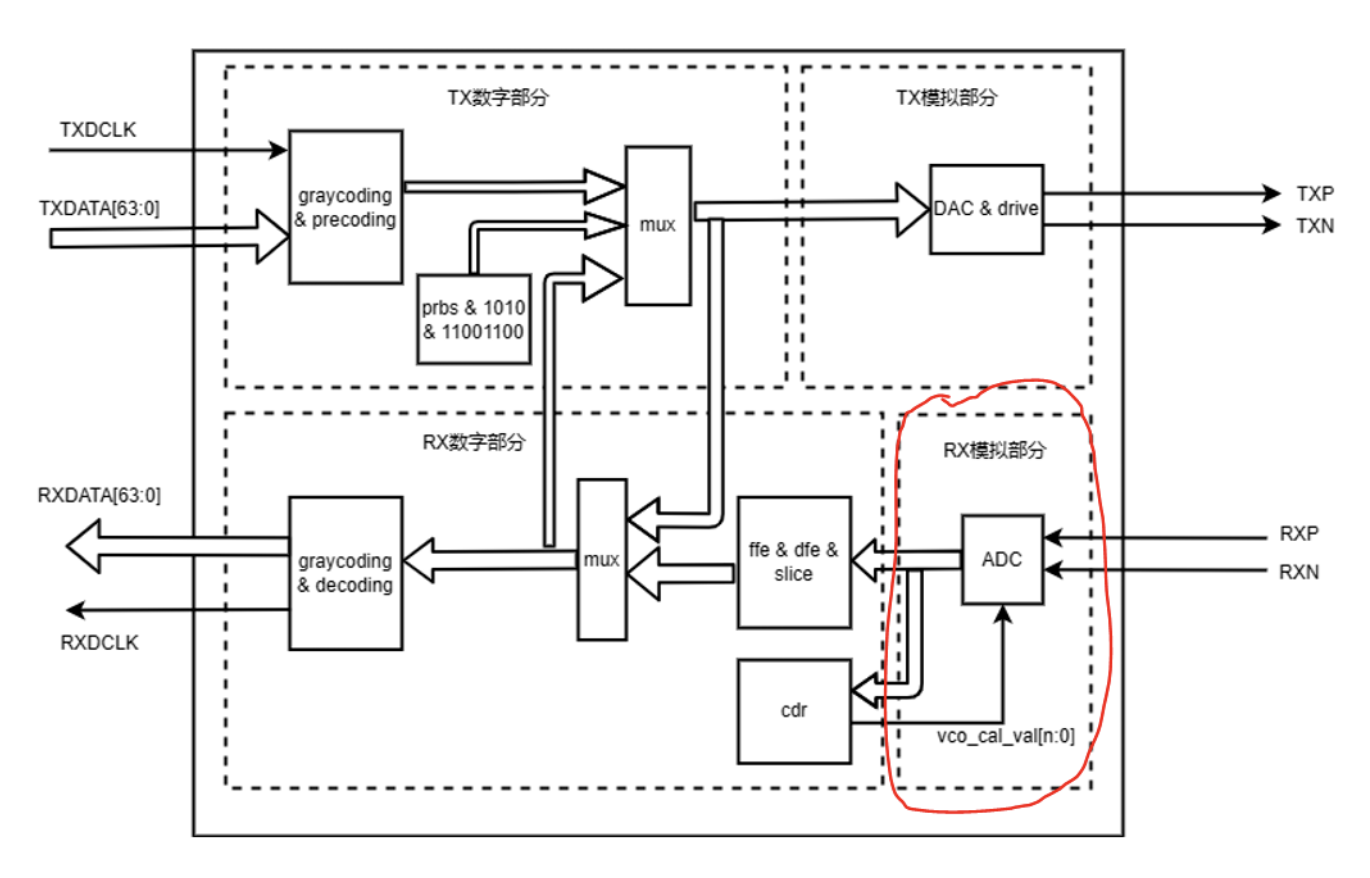

SerDes主要由PLL組成時鐘模塊, 控制模塊,發射器和接收器組成(如圖2所示)。為了解決測試難題及降低測試成本,如今的SerDes還添加了偽隨機碼(PRBS)產生器, 偽隨機碼(PRBS)檢驗器和環回路徑等模塊輔助測試。

圖2:SerDes結構

2 SerDes測試

SerDes測試主要分BIST測試和high speed I/O測試。BIST測試主要依賴于芯片內部的測試模塊,測試芯片功能是否正常,其主要特點是測試效率高,成本低,對load board等硬件制作要求低,但無法測試芯片的特性,測試覆蓋率相對較低,并且無法失效定位。而High speed I/O測試基本可以滿足所有SerDes測試需求,測試覆蓋率高,但是對于硬件制作要求高,測試成本高。

SerDes High speed I/O 依據測試模塊可分成接收器測試和發送器測試兩大部分。接收器性能指標主要有:靈敏度測試,抖動容忍度測試,skew測試,阻抗測試等。發送器性能指標主要有:輸出幅度測試,眼高,眼寬測試,上升下降時間測試,抖動測試(TJ,RJ/DJ),眼圖測試,共模電壓測試,skew測試,阻抗測試等[2]。

3NautilusUDI方案

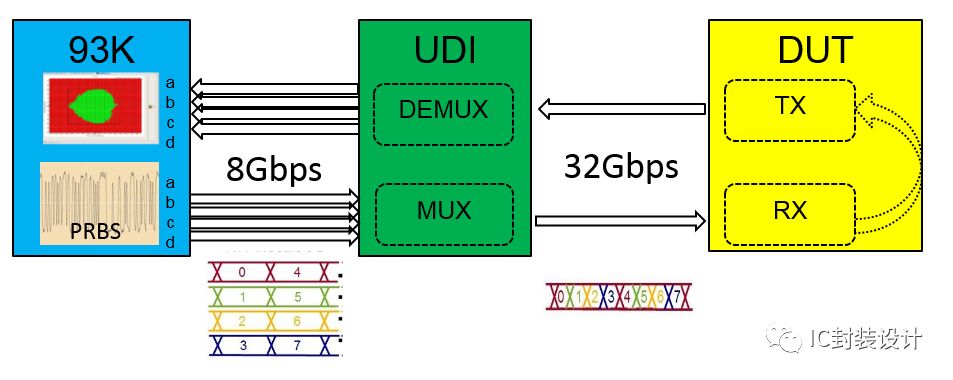

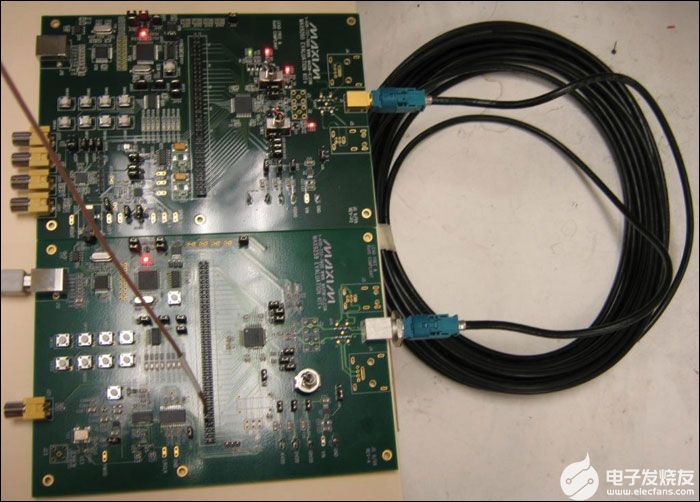

Nautilus UDI(下面我們簡稱UDI)方案如圖3所示,93000發送4路8 Gbps信號至UDI,經UDI內部MUX合成成1路32 Gbps信號至芯片,結合芯片內部偽隨機碼檢驗器實現接收器測試。芯片內部發射器發送32 Gbps 信號,通過DEMUX分解成4路8 Gbps信號后,被93000采樣測試分析,實現了發射器測試。借助芯片parallel loop back模型[3],在實際的量產中我們通常以環回眼圖測試來覆蓋接收器和發送器。UDI測試速率為16G~32.8 Gbps (未來最高速率可達64 Gbps) ,能夠支持最多16組接收器和發射器測試。

圖3:UDI測試方案模型

3.1 Nautilus UDI工作原理

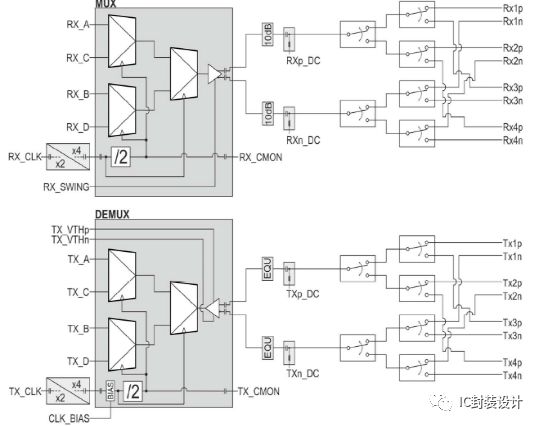

UDI主要由MUX和DEMUX 2部分電路組成。MUX內置1個4:1多路復用器(如圖4所示),通過RX_CLK(4 Ghz)x2倍頻時鐘控制第一級2:1復用器,實現AC, BD合成,經過X4倍頻時鐘控制第二級2:1復用器后轉換成ABCD。再通過一個輸出幅度(0~1200mV)可調的放大器及10db衰減器作為輸出(0~260mV),滿足了測試接收器靈敏度功能及精度需求。RX_CLK除了提供復用器觸發時鐘外,通過在RX_CLK上增加抖動的方式來實現在輸出信號上添加抖動,從而達到測試接收器容忍度的目的。DEMUX結構和MUX近似,內置1個1:4多路解復用器,并且在DEMUX前增加了一個無源的均衡器,使因路徑插損造成畸變的信號更平坦,降低因路徑造成的碼間干擾。

圖4:MUX和DEMUX結構

3.2芯片輸入時鐘

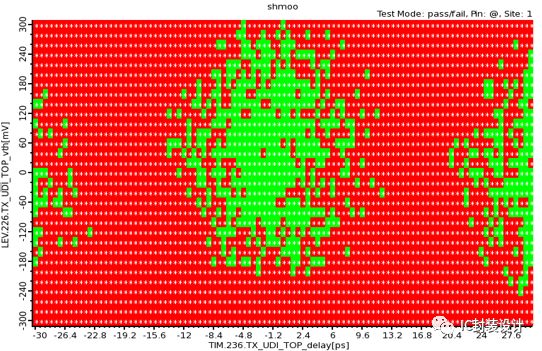

SerDes對于參考時鐘有較高的要求,輸入時鐘的RJ會被SerDes混入,無法測試出芯片真正的Jitter, 如圖5所示使用RJ=1ps的參考時鐘(SerDes要求RJ<400fs),眼圖散點太多無法保證測試穩定性。為此我們選用了一個標準化模塊Jitter Attenuator Module(簡稱JAM),通過93000對其可編程控制,實現了不同頻率時鐘輸入降噪處理,經過JAM后的參考時鐘RJ降低到300fs以內(如圖6),掃描的眼圖沒有散點(如圖7),保證了量產測試穩定性。

圖5: RJ=1ps系統時鐘,PLB眼圖

圖6: JAM輸出時鐘相位噪聲指標

圖7: 使用JAM作參考時鐘PLB眼圖

3.3 Load Board 設計

SerDes高速IO接口測試,對發射和接收管腳外圍電路的信號完整性要求是很高的,稍有不慎,就會導致測試結果出現巨大誤差。對于SI規則我們提出了以下幾點:1)對于TX,RX全鏈路(包含過孔)的TDR要求是單端阻抗50Ω±5Ω,差分阻抗要求100Ω±10Ω。2) 需要考慮封裝因素,做到以lane間的衰減相等代替原先只考慮Load board的走線的等長。3)對于Load Board的材質,盡量使用介電常數小的材質,如Roger,Megtron6,Necole等,介電常數越小,線損衰減也越小[4]。4)全鏈路采用高速布線的要求(線寬,間距需滿足一定比例,信號包地處理等)。5)Load board設計完成之后必須使用“3D”仿真,以滿足S21>-3db@15GHz;S21>-6db@30GHz的要求。3.4 Socket選擇

Socket也是測試過中比較重要的部分,主要有pogo pin和導電膠2種材質,Pogo pin的socket耐用性好,高低溫差異不大,適合量產使用。導電膠 socket 由于加工工藝特性,信號衰減小,適合高頻測試,但是由于其不耐磨,無法滿足大批量生產的需要,所以只適合特性測試。4 測試結果

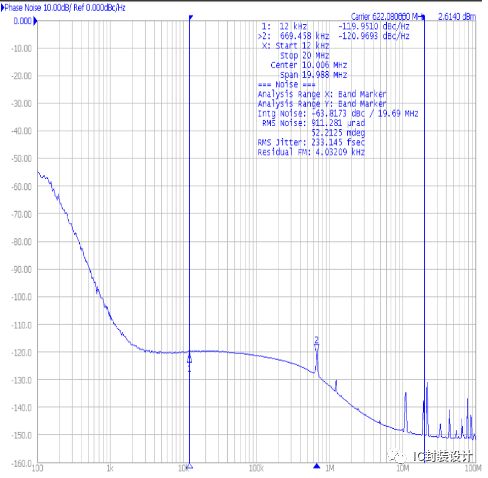

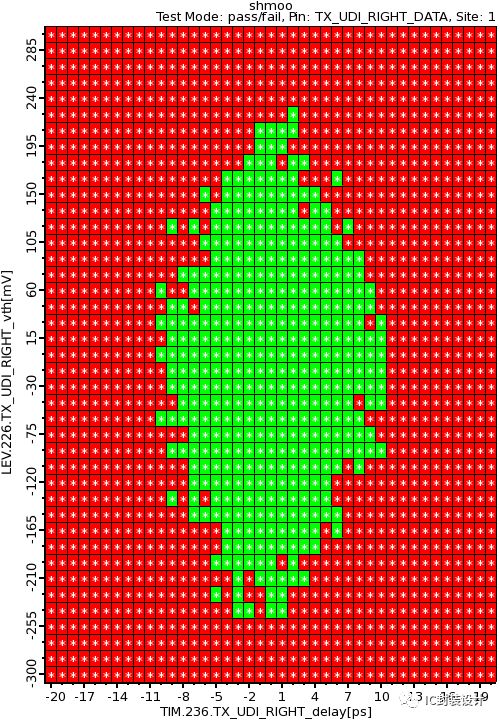

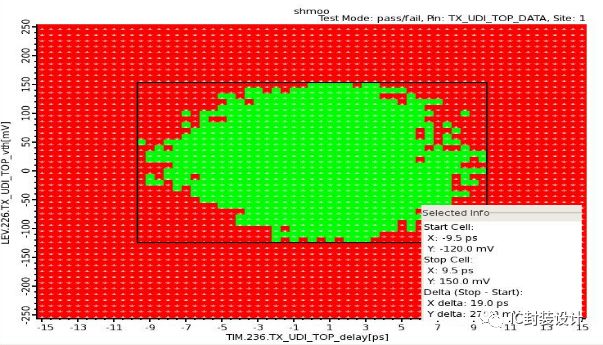

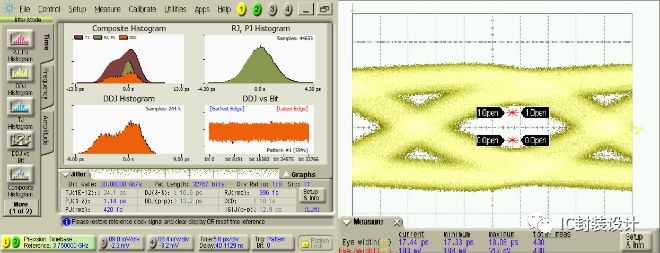

應用UDI的方案我們對32 Gbps SerDes芯片進行了PRBS15 Loopback測試,UDI測試的眼寬眼高分別為19ps,270mV(圖8),和DCA量測結果(圖9)基本保持一致。

圖8:UDI眼圖SHMOO掃描

圖9:DCA 實測結果

5 結論

Nautilus UDI方案提供是一套實現高速I/O接口特性測試及量產測試自動化的完善方案,一經推出即得到許多國內外客戶的認可,并且與國內某知名半導體公司合作,實現了多個25~32G Bps SerDes芯片的穩定量產,相信未來能夠幫助更多還在為高速SerDes測試而困擾的客戶解決高速I/0測試這個難題。

-

SerDes

+關注

關注

6文章

199瀏覽量

34937 -

輸入時鐘

+關注

關注

0文章

3瀏覽量

7257 -

Gbps

+關注

關注

0文章

9瀏覽量

9736

原文標題:32 Gbps 高速SerDes 量產測試方案

文章出處:【微信號:gh_f97d2589983b,微信公眾號:高速射頻百花潭】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

提供量產23D+DSP 實現25 全功能量產方案

淺析HDMI接口和UDI接口技術

SERDES接口電路設計

如何設計低功耗FPGA的8b/10b SERDES的接口?

請問單個SERDES Quad可以同時運行4個接收通道嗎?

Nautilus UDI方案是如何實現高速SerDes測試的?

Osiconcept靈感系列傳感器 Nautilus壓力傳感

Avago Technologies于28nm CMOS工藝達成32Gbps的SerDes性能

如何通過SerDes獲得32Gbps的板級傳輸速度

基于SERDES時鐘的頻率跟隨的設計

基于FPGA芯片的SERDES接口電路設計

使用內置誤碼率測試電路的2.5Gbps SerDes可以輕松測量鏈路質量

serdes串行發送和接收是怎么實現的?serdes就是用56G的ADC和DAC嗎?

DS320PR1601 32Gbps 16通道PCIe 5.0、CXL 2.0線性轉接驅動器數據表

通過Nautilus UDI方案的導入,實現32Gbps SerDes的量產測試的概述

通過Nautilus UDI方案的導入,實現32Gbps SerDes的量產測試的概述

評論