1. 現象描述

產品在進行 25KV 空氣靜電放電抗干擾試驗時,對儀表顯示屏正下方外殼的縫隙位置放電時,儀表盤液晶屏字符顯示錯誤,出現斷碼、花屏等現象,具體見下圖 1 所示:

圖 1 空氣放電實驗

2. 原因分析

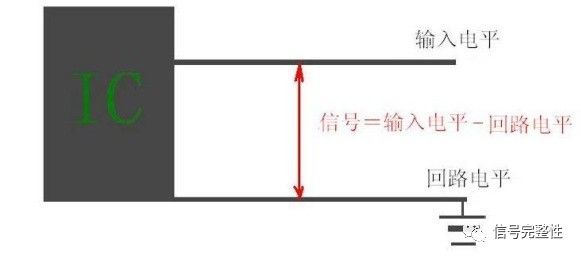

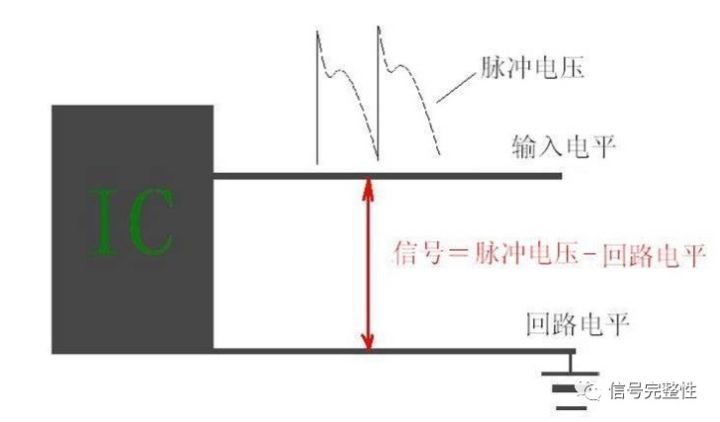

首先我們來分析信號形成的原理,當一個電平被輸入,要區別它是有用信號或無用信號,必須對其電平值進行判定識別。簡而言之,就是要判定信號的電平大小、極性、頻率等參數,必須要有一個總體的參考電平為基準。在電路設計中,我們把電流回路作為單個系統的總的參考電平基準,即 0V 電平。如示意圖 2 所示,信號等于輸入電平減去參考電平,得出的信號電平可能是正極性,也可能是負極性。只要單個單元回路的參考電平一致且穩定,那么整個電路單元就能按原設計指標正常地運作。

圖 2

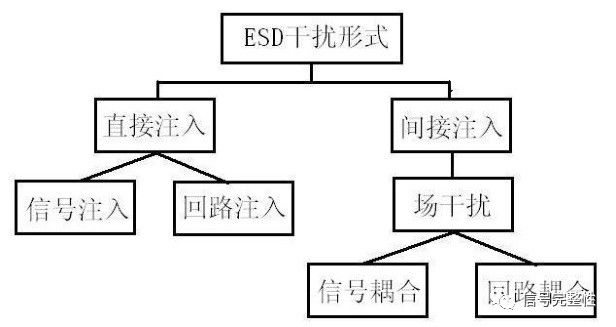

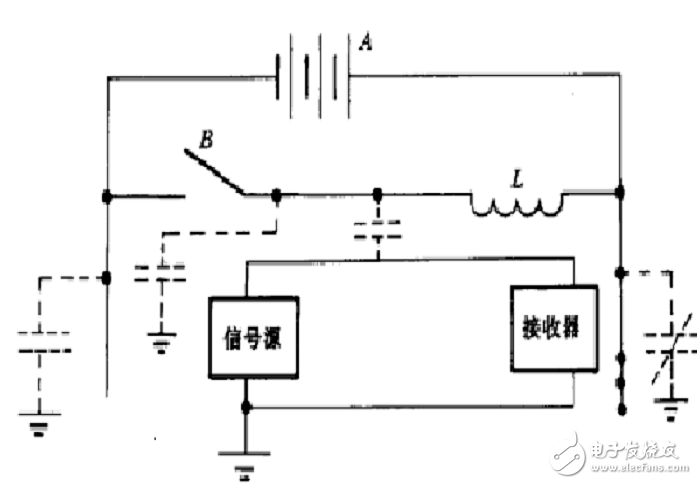

在 EMC 實踐工作中,靜電的干擾方式、耦合途徑、耦合的脈沖電壓、極性等多種多樣,從泄放途徑上基本上大致分為直接干擾和間接干擾兩大類,對電路的影響主要表現在信號干擾和回路干擾兩種基本形式,見下圖 3。

圖 3

該汽車儀表總成的測試現象為空氣 25KV 等級對顯示屏周邊的縫隙進行放電,出現顯示錯誤或工作異常,對應圖 5 我們就能找出空氣放電干擾的基本形式——即靜電場干擾。此時還需要分析清楚這個靜電場是如何導致系統工作異常的,是如何耦合到內部電路系統的,是信號通路還是回路被干擾等等問題。只有把病因了解透徹,才能從根本上治療病癥。對應前面所述的測試現象,其靜電的幾種干擾形式可以借助示意圖 4、5 來分析。

圖 4 圖 5

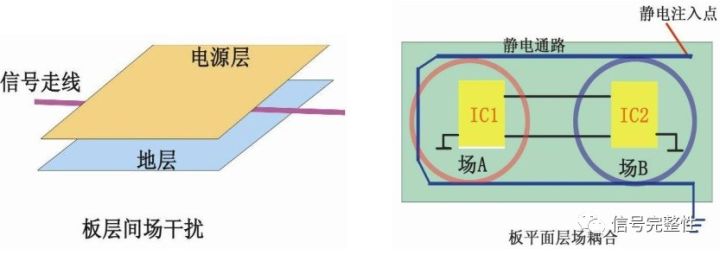

圖4示意圖所示為多層板之間的形成的靜電場干擾示意圖,在多層PCB板中,往往很多信號走線被敷設在了電源層或地層的相鄰層或中間層,根據我們的大量實驗分析證明,在靜電放電抗擾度試驗中,一旦地層的泄放路徑阻抗較大時,那么與之相鄰層的信號層或電源,就極易被地層上形成的靜電場所耦合。同理,電源層形成的靜電場原理類似,圖 4 中,主要是考慮多層 PCB 所導致的失敗因素。

圖 5 所示多見于單面或雙面板的結構分布,由于 PCB 的走線或周圍的鋪地結構引起,被直接或間接注入靜電脈沖電壓,它所形成靜電電流流動的環路而產生的靜電場分布,在該靜電電流環路中的系統或單元模塊會因此而耦合到場能量,如果有多個單元或模塊,那么每個單元或模塊所耦合到的靜電場能量會根據 PCB結構的布置而有所不同。圖 4、圖 5 在理論上,又可以用圖 6 的等效圖來幫助分析。

圖 6

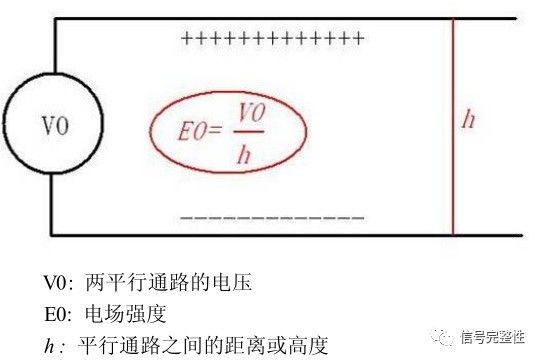

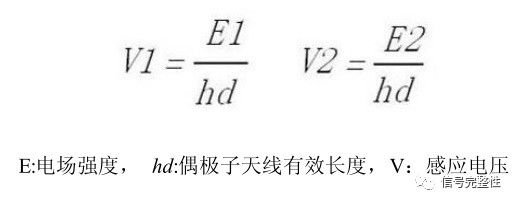

電場 E0 等于 V0 比上兩個平行通路的距離 h 。在實際的生產和過作中,我們會發現,由于走線的結構、導體橫截面積、器件分布、通路阻抗等因素的影響,會導致多個不同強度的場分布,如圖 5 所示,形成靜電場 A 與靜電場 B 兩個強度不同的場分布,處于該場分布中的 IC1 和 IC2 兩個單元模塊會受到兩個不同強度的靜電場干擾,假設場分布中 IC1 和 IC2 的中間走線看似為偶極子天線,有效長度為 hd ,那么根據理論公式計算,能夠在其走線上感應到兩個不同的電壓值,設靜電場 A 為 E1,靜電場 B 為 E2,由于 E1≠E2,設定兩個單元的有效天線長度相同(實際中對應兩個單元模塊而言永遠不可能一致),最終得出 V1 ≠ V2。計算方法如下:

當所感應到的 V1、V2 能量足夠高、△V1V2 足夠大時,就能夠擾亂 IC1 和IC2 之間的正常通訊信號,根據前面圖 2 的分析基礎,此時的信號等于信號走線上感應到的脈沖電壓減去回路電平,如圖 7 所示。此時的電路已經無法識別信號,導致電路工作異常中斷。

圖 7

3. 整改措施

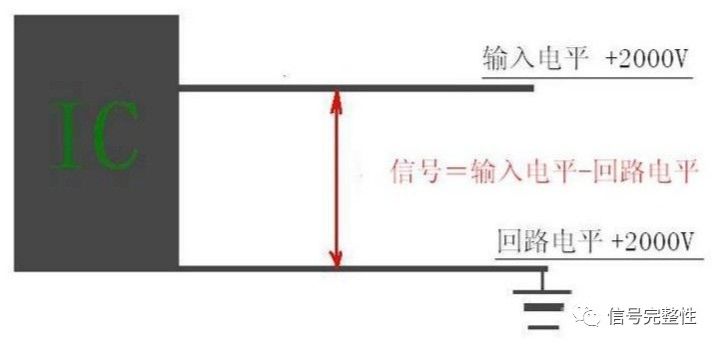

通過上述的理論分析,該產品的故障因素主要是由靜電場干擾所引起,要解決場干擾問題,大致的方法有兩種:一是采用泄放的方法,對敏感的“天線”進行有效地去耦處理,在信號通路上進行泄放,達到通過的目的;二是采用屏蔽的方法,對敏感的單元模塊、“天線”等進行必要的靜電屏蔽,保證信號與參考電平的差值不發生突變,使之正常工作。無論我們采用何種技術方案,其根本的目的還是在于消除信號電平與回路參考電平的差值不會突變。如下圖 8 所示,使單元電路的輸入電平和回路電平保持同時的升高或降低,對于信號電平總差值而言,可以基本維持不變化。

圖 8

靜電的器件通常可采用如 TVS、放電管、壓敏電阻、高分子吸收材料、電容等器件。對于信號端口而言,最有效、成本最低、性能最可靠的還是選用電容器件,利用電容對脈沖信號的瞬時導通的特性,可以迅速地將靜電脈沖往低電勢方向泄放,達到平衡的目的。

進一步分析產品內部結構,圖 11 為 LCD 屏信號走線,其走線較長,空白位置沒有鋪設地層,留有較多空白處,在靜電放電時,走線極易形成天線效應。

圖 9 顯示數據線的走線

圖 10 是 LCD 與主板的連接結構,直插式,距離較高,約 1cm。LCD 數據引腳也可能形成天線效應,接收到靜電場強干擾。

圖 10 LCD 屏的引腳連接結構圖

通過基本電路結構的分析,PCB 在布板時,尤其是在 LCD 屏的數據走線的設計方面,存在不足,走線較長,且走線空白處和芯片周邊未鋪地,沒有隔離和吸收作用地層,LCD 在組裝結構上同理,插件引腳太長,沒有增加任何去耦措施,導致靜電在放電過程中,所有的數據線全部成為了接收天線。在設計上稍作改進便能通過測試,但客戶的產品已經生產,后期不對 PCB 進行大改。故制定的整改方案是在不大改 PCB 板的前提下調整或增加器件,并保證成本和工藝的可行性。

根據前面所述原理,制定整改方案:

1、對靠近邊沿的重要數據線,采用去耦的技術方法,減小其“天線”的接收能力,使其對地形成泄放路徑,達到抑制靜電干擾的目的。在 LCD 引腳上采用 100pF電容與地并聯,如圖 11 所示;

圖 11 數據線去耦

2、對走線進行屏蔽。由于引腳過長,對屏引腳進行靜電場屏蔽處理,消除電場影響,在 LCD 左右兩邊的引腳支架上,采用銅箔屏蔽并良好接地,用于吸收靜電干擾。屏蔽措施在重新的設計改進中,可以更改為 PCB 走線間鋪地和 LCD引腳周圍鋪地代替。

圖 12 LCD 屏蔽

4. 試驗驗證

25KV 靜電放電試驗通過。

-

emc

+關注

關注

170文章

3935瀏覽量

183413 -

儀表盤

+關注

關注

0文章

56瀏覽量

14954

原文標題:20180501-EMC之靜電整改案例

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

深圳比創達電子EMC|人體靜電對精密電子器件的傷害如何避免.

電波暗室是什么?#電磁兼容EMC #電波暗室 #EMC #電磁干擾 #靜電放電#雷擊浪涌

電源設計中的EMC、EMI、ESD概念簡述

汽車整車靜電放電測試

測量技術系列之MC測試與靜電放電抗擾度試驗

什么是EMC和EMC設計

USB 端口的兩種優化設計:靜電放電保護與單通道保護

電纜對靜電放電的影響分析

避免閘極過度耦合效應的靜電放電防護電路設計

什么是靜電干擾?靜電屬于電磁干擾嗎?

EMC工作中常用的公式

EMC實踐工作中,如何避免靜電放電干擾

EMC實踐工作中,如何避免靜電放電干擾

評論