在知乎上有一個問題,“芯片產(chǎn)業(yè)中的光刻機是怎么雕刻出遠遠小于自己波長的線寬的?”這個問題很有意思。

半導(dǎo)體工藝1年一變,學(xué)生在學(xué)校看到的教材,實在跟不上。EDN編輯看到了網(wǎng)友Ida Lin的回復(fù),覺得通俗易懂,特地授權(quán)轉(zhuǎn)載過來分享給大家。

當(dāng)然更專業(yè)的解釋也可以去查Wiki

想當(dāng)年整個芯片工業(yè),各家包括intel ,GF, 臺積電,三星都在三星都在22nm,28nm這個節(jié)點卡了很久,想必是遇到193nm ArF的極限了。

然而193nm能做出50nm以下,1/4波長的尺度,已經(jīng)非常神奇了不是嗎?

不過這背后也存在命名問題。xx nm節(jié)點不意味著真正的結(jié)構(gòu)就那么小。首先這個數(shù)字原來是指結(jié)構(gòu)的half pitch,即一半的周期。而到了后來水份更多,一般是指最小feature-size。比如一排100nm周期的突起或者凹陷,突起的寬度20nm, 空隙80nm,那么不嚴格的說這也是一個20nm的工藝。

此外, 32nm 22nm 14nm只是一個技術(shù)節(jié)點的標(biāo)志, 可能對應(yīng)的最小結(jié)構(gòu)是 60nm, 40nm, 25nm等等,總之要比標(biāo)稱大不少。這個節(jié)點各家公司還不一樣,比如大家常說Intel的14nm比Samsung和臺積電的10nm密度都大等等(不置可否)。

但是如何做出遠小于一半周期的minimum-feature呢?

單從光場分布來說,一個峰或谷的寬度很可能還是突破不了衍射極限。但是可以利用光刻膠的性質(zhì)!

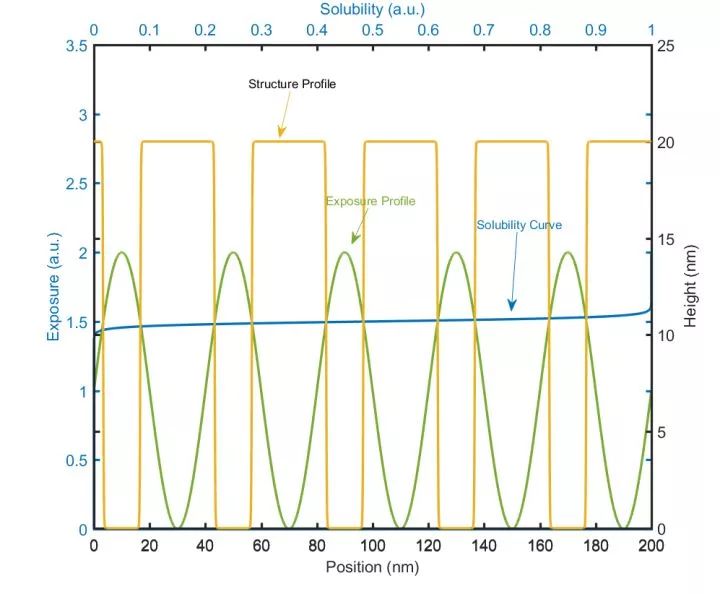

光刻膠曝光后的溶解性依賴于曝光量,這大家都知道,但是這個依賴很不線性。通過控制這種不線性,使得在某個閾值曝光量附近,小一點的完全不會溶解,大一點的極易被溶解,那通過準確把握曝光量,就可以輕松控制最小結(jié)構(gòu)的線寬。

試想一個均勻分布類似正弦波的光場,把曝光將控制到只有波峰附近那些位置能完全溶解,之外的部分溶解性不變,那么最后做出來的結(jié)構(gòu)就是一個周期和正弦波一樣,但是最小寬度小的多的結(jié)構(gòu)。

見下圖。黃色曲線代表的結(jié)構(gòu)的凹陷要小于光場分布一個峰的寬度。

當(dāng)然這種方法也不是能做出無限小的Feature。畢竟光刻膠的溶解特性哪兒有想要什么就有什么的,每一種配方的研制都非常復(fù)雜,還要和現(xiàn)有的流程工藝匹配。而且光刻膠涂層畢竟是有厚度的,表面的曝光分布和整體也不盡相同。同時它的機械性質(zhì)也無法維持很窄的細節(jié)的完整性。

還有另外一些方法能將光刻膠層被激活的區(qū)域集中在比曝光光場小很多的尺度內(nèi),包括各種玄乎的化學(xué)處理,熱處理等。

既然有了上述方法,能讓Minimum Feature Size至少小于半周期,那么接下來實現(xiàn)密度的增長就有了可能——通過多次曝光。

同樣的結(jié)構(gòu),平移一下再做一遍就多了一倍的密度。

但是實施起來并沒有那么簡單。

關(guān)鍵就是在后續(xù)曝光中要做到一個對先前結(jié)構(gòu)保護凍結(jié)的步驟。最樸素的多重曝光技術(shù)就是,做一次,再做一次,可以稱作LELE(Litho-Etch-Litho_Etch)。如下圖

最上面是已經(jīng)經(jīng)過一次Patterning的保護層(藕荷色,如SiN)再加上一層光刻膠(紫色)。光刻膠在新的Mask下被刻出另一組凹槽(中間)。最后光刻膠層被去掉,留下可以進一步蝕刻的結(jié)構(gòu)(下圖)。

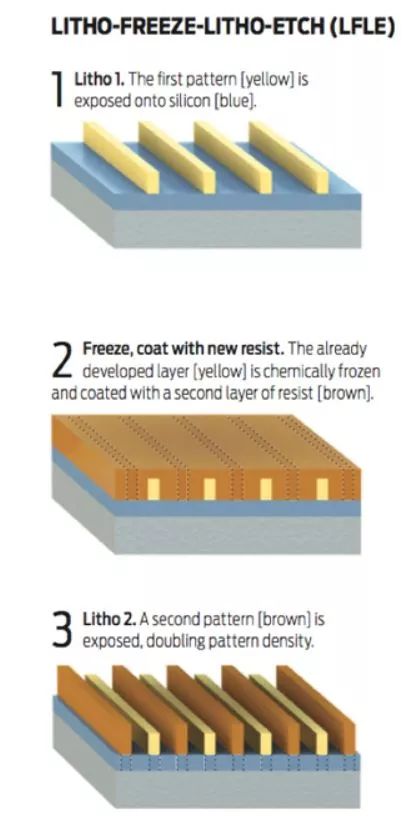

另外一個變種是Litho-Freeze-Litho-Etch (LFLE).

第二層光刻膠直接加在第一層沒被去除但被化學(xué)凍結(jié)的光刻膠上,再來一次光刻,形成兩倍的結(jié)構(gòu)。比LELE可以節(jié)省些步驟。

這一類多重曝光的特點就是流程簡單粗暴,很早就有人嘗試應(yīng)用。但一個最大的問題就是,后一次光刻和前一次的對準問題。

這幾乎是一個可以讓這類方法徹底無效的巨大難關(guān)。

想要做出20nm左右的結(jié)構(gòu),那對準誤差要控制在4-5nm以下,然而可以用于實施觀察的SEM分辨率最好也就10nm!

總之這個問題確實阻礙了這種方法的應(yīng)用——除了早期45nm、32nm節(jié)點的DRAM工藝(結(jié)構(gòu)簡單,重復(fù)性高),而且超光雙重曝光的情況幾乎沒有,CPU GPU芯片應(yīng)該采用的并不多。接下來是另一類聰明一點的多重曝光,可以統(tǒng)稱為SADP (Self-Aligning Double Patterning).

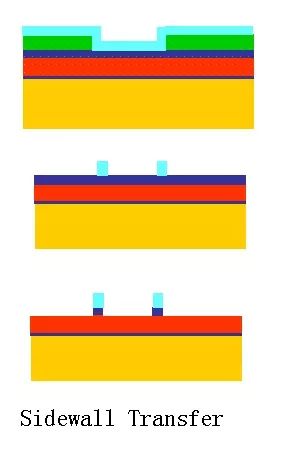

比如Side Wall Transfer就是核心的實現(xiàn)方式。主要是利用第一層結(jié)構(gòu)的Sidewall來形成兩倍的Feature, 從流程上來說省了不少事兒,而且不用考慮對準的問題。

但是這個方法對技術(shù)要求也很高,我再放一張圖:

注意看第二步的棕色材料的沉積——這一步是一個Conformal Deposition-所有表面不論取向都有類似的沉積率。而接下來第三步的蝕刻應(yīng)該是一個Non-conformal Etching ——蝕刻幾乎只在垂直方向上進行,才能呈現(xiàn)出想要的效果。這兩個步驟對材料和工藝都有一定限制。

Sidewall Transfer有一個難點就是,最開始的結(jié)構(gòu)的Sidewall必須夠直夠平整,不然之后補充材料的支持會有問題,形狀也可能出現(xiàn)很大偏離,導(dǎo)致對其下的材料層的蝕刻出現(xiàn)偏差。而且自由度明顯前一類方法高。生成的結(jié)構(gòu)的寬窄,對稱性等都受到了限制。

不過這并其實并不是什么大問題,都是可以前期設(shè)計時考慮好的。主要是沒有了對準這大難題,應(yīng)用范圍就廣了不少。

基于這種方法,重復(fù)一次就可以實現(xiàn)SAQP, 做20nm左右的feature不是什么問題。

還有一種比較奇葩的方法,Direct Self-Assembly——即利用保護層材料本身的Phase Seperation 實現(xiàn)一層材料就可以用來做兩次互不影響的蝕刻。

具體地說是利用某種Copolymer,比如PMMA-PS,在滿足一定分子比和物理條件的形況下,PMMA跑到一邊,PS跑到另一邊,形成很有序的交錯結(jié)構(gòu),再進行針對不同組分的蝕刻就可以Double Pattern了。

不過這個方法想來限制也很多,比如交錯結(jié)構(gòu)的分布,占空比,也不是你想讓人家怎么分布就能怎么分布。而且平整度肯定比不上那些Hard Mask Material。這個方法當(dāng)前應(yīng)該還是主要用于學(xué)術(shù)界玩兒各種小規(guī)模簡單結(jié)構(gòu)的試驗,似乎沒有應(yīng)用到工業(yè)領(lǐng)域。

以上所述的各種方法,結(jié)合實際來看,由于真實的集成電路結(jié)構(gòu)超級復(fù)雜,各種不同材料,不同區(qū)域,不同的互聯(lián)和切斷的要求,而且實際的布局是需要二維甚至三維考量的,所有這些復(fù)雜因素就構(gòu)成了更多更多的難題,和捷徑,由此衍生了基于不同材料(電介質(zhì)層,金屬)和不同功能區(qū)域的奇技淫巧。但是這塊太復(fù)雜了,我也不甚了解。

說了這么多怎么通過光刻之后的手段來增加密度減少線寬的,但還需要一個最核心的技術(shù)——如何把老老實實的單次曝光的Feature/周期做的最小最漂亮呢?

基于CD=k*lamda/NA, k通常為一個0.25-1之間的常數(shù),那么首先想能提高的就是NA=nsin(像方半孔徑角)。正弦最高做到1,而在物鏡和晶圓之間加一層高折射率液體,比如水,NA就到了1.33。(應(yīng)該也可以用更高折射率的油到1.4多?)。

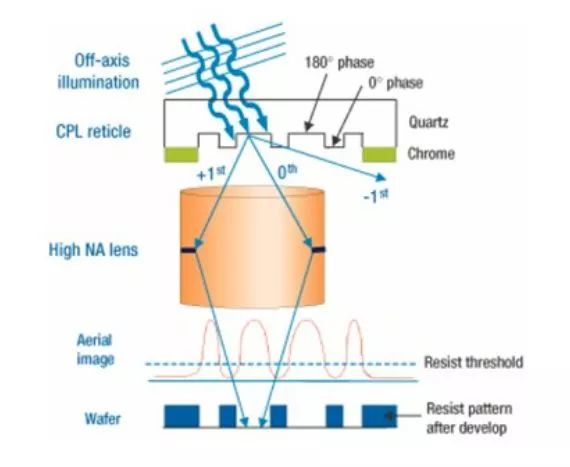

Immersion Lithography,不多說了,EUV之前妥妥的必備技術(shù)(然而到了EUV肯定用不了了)。然后就是Off-Axis Illumination。讓光學(xué)系統(tǒng)的主光軸和照明方向不一樣,光源斜著打。

這個原理也比較直觀,就是盡可能的舍棄一些MASK的空間低頻成分,讓含有更精細結(jié)構(gòu)的高頻成分進入物鏡從而成像。從原理上來講,MASK上凡是小于光照波長的高頻成分,都成為了高頻信息,所對應(yīng)的光是只在橫向傳遞,而軸向極具衰減的隱失波,很大可能沒有辦法被物鏡收集。斜照明的情況下,高頻空間成分正負至少有一支有更小的衍射角從而進入物鏡,甚至從隱失波變成可以被收集的成分(當(dāng)然 另外一支就被推的更遠了,不過無所謂)。最后的效果就是Wafer上的像含有更多的高頻成分,自然也就更接近Mask的形態(tài)。

Mask上面也可以做文章。首先就是采用Phase-Shift Mask。相鄰的很近的通廣孔,引入不同的相移,那么相干成像的情況下,雖然兩者各自的電場強度分布有很大重疊,但是電場疊加以后由于有(最好是pi)的相差,變成了一加一減,中心強度為零,正好分開成了兩個獨立的峰。

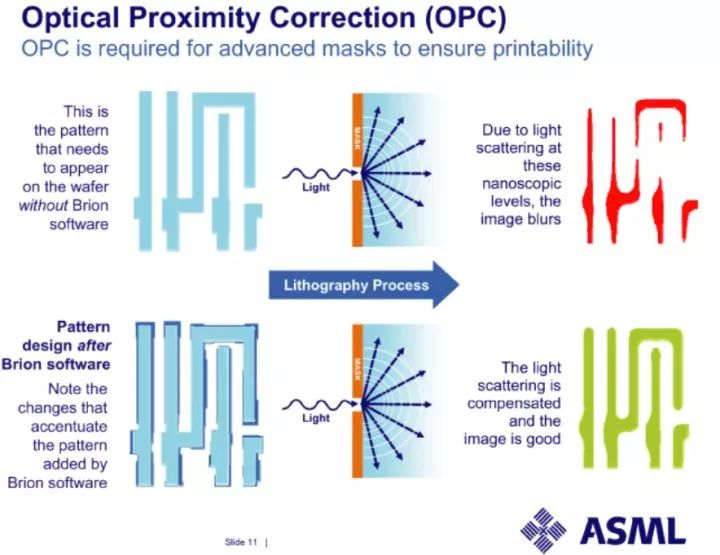

最后的關(guān)鍵技術(shù)是Optical Proximity Correction。

以上所說的種種技巧,都無法保證最終的結(jié)構(gòu)具有完美的、橫平豎直、想圓就圓想方就方的形狀,對于2D結(jié)構(gòu)更是如此。雖然說一個MOS管不需要有完美的形狀來保證工作,但是一大片密集的工作單元,互相的分離連接,是一定要保證的。可以肯定的說,如果你把MASK天真的做成和最后想要的結(jié)構(gòu)長一個樣子的話,那100%在65nm一下尺度你最后得到的就是一疊垃圾。

OPC的神奇如圖:

這個過程是怎么實現(xiàn)的?

我也不知道,但想必需要非常復(fù)雜的波動光學(xué)模擬方法以及無數(shù)次的實驗反饋及后續(xù)優(yōu)化。從某些角度講,OPC這一領(lǐng)域好像是當(dāng)前FAB前沿最吃香的工作(純屬道聽途說,準確性不保證)。

最后說一下,我并不是從業(yè)者,純屬為了做課程Presentation,并且對這方面感興趣就收集了一系列材料。我一直以來的困惑就是發(fā)現(xiàn)這些材料都非常零散非常瑣碎,很少能看見大型的綜述文章或者雜志專題,不知道是由于商業(yè)機密還是什么,但能感覺到根本不入學(xué)術(shù)界的法眼。畢竟所有人都在玩兒Graphene, CNT, TMD,Single-Molecule Transistor是不是?硅?這玩意兒應(yīng)該過時30年了。

我個人也有很多問題這些年來都沒能解決。比如Multi Patterning到底從哪個節(jié)點開始被廣泛采用?65?45?EUV談了這么多年,現(xiàn)在成型了嗎,14nm 10nm這兩代到底主流是什么技術(shù)?畢竟這么巨大的投資和技術(shù)轉(zhuǎn)換,沒什么可能D/E混用吧?其實想來也挺神奇的,這5年來由于技術(shù)瓶頸,半導(dǎo)體工藝界不知道發(fā)生了幾輪巨大的技術(shù)革新和變動,可是外界根本看不出什么大動靜,基本上每年都能簡單的小一號兒。這種產(chǎn)出的穩(wěn)定性真是有點細思極恐。

關(guān)于Sidewall部分,知乎網(wǎng)友Albert Hu做出來自己的解答:

193nm波長的光為什么能用在130nm,90nm,65nm甚至45nm的制程上?因為130nm以下柵極的多晶硅條一般使用側(cè)墻轉(zhuǎn)移(Sidewall Transfer),并不是直接使用光刻.簡單來說,側(cè)墻轉(zhuǎn)移是先用光刻等方式形成圖案。這個圖案的并不需要很精細,但是經(jīng)過一些處理,邊緣做成階梯狀且比較陡直。然后沉積一層所需材料,這樣圖案邊緣也會有一層可控制厚度的材料形成同樣的階梯。蝕刻掉上下平面的多余材料,階梯處保留下來就出現(xiàn)非常細的一條。這一條材料的寬度要看材料的選用和沉積的方式和持續(xù)時間,所以光刻波長并不起作用。它的精度要看材料(以及刻蝕材料)的“物質(zhì)波長”了。

真正用光刻的是在互連層,而65nm工藝下最低一級互連層的最小間距目前也在120nm以上,還沒有達到193nm光刻的瑞利極限.使用這樣的方案,193nm的波長就可以用到90nm,65nm甚至45nm的制程上。比較特別的是,線寬因為與光刻波長失去了聯(lián)系,半代,甚至更奇特的線寬都可以在同樣的設(shè)備上完成-----80nm的生產(chǎn)設(shè)備可能和90nm的一樣,55nm和65nm一樣。半代之間甚至兩代之間的差距變得很小。線寬幾乎變成了工藝中最不重要的參數(shù)了。

-

芯片

+關(guān)注

關(guān)注

456文章

51157瀏覽量

426874 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27693瀏覽量

222241 -

光刻機

+關(guān)注

關(guān)注

31文章

1156瀏覽量

47566

原文標(biāo)題:193nm波長的光刻機,是怎么刻出來28nm線寬的芯片?

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

光刻機工藝的原理及設(shè)備

光刻機是干什么用的

魂遷光刻,夢繞芯片,中芯國際終獲ASML大型光刻機 精選資料分享

光刻機能干什么_英特爾用的什么光刻機_光刻機在芯片生產(chǎn)有何作用

政策助力光刻機行業(yè)發(fā)展,我國光刻機行業(yè)研發(fā)進度仍待加快

芯片產(chǎn)業(yè)中的光刻機是怎么雕刻出遠遠小于自己波長的線寬的?

芯片產(chǎn)業(yè)中的光刻機是怎么雕刻出遠遠小于自己波長的線寬的?

評論