物理層的一致性測試作為近 10 多年來示波器最主要的用途之一,一直是產業界最常提到的名詞之一。本文嘗試將物理層一致性測試的含義,要素與目的及未來發展趨勢做一個簡單的探討和說明。(如無特別說明,本文后續提到的一致性測試均指物理層一致性測試)。

一致性測試的由來和什么是一致性測試?

英文單詞 Compliance,廣泛用于各行業,用在電子行業顧名思義就是合乎規范。一致性測試作為產業界工程師們最耳熟能詳的名詞,已經深入人心十幾年了。

物理層一致性測試最初發軔于 USB2.0 標準,由 USB-IF 協會和業界巨擎Intel 公司推廣普及。由于采用 USB2.0 標準的主機(Host)及設備(Device)和集線器(Hub)數量暴增,需要解決各設備之間的物理層和協議層的兼容性和分歧,因此制定了一個統一的標準化的衡量方法來評估各設備的信號質量。一致性測試類似黑盒測試,通常只關注設備外部接口處的信號質量。通過協會認可的一致性測試,可以打上對應的Logo 。今天一致性測試已經廣泛被各大標準和協議會組織采納,比如 HDMI,DisplayPort,USB3.x,SATA/SAS,PCIExpress,ThunderBolt 等。

業界另外一大組織IEEE 相應地后來在 10/100/1000 BaseT 的測試上也引入了一致性測試的概念用于評估各設備的信號質量。事實上無論如何滄海桑田,USB2.0和以太網是最成功和經久不衰的兩個接口和通訊標準。即使在近幾年 IEEE 發表的最新的200G/400G標準中也定義了類似的測試方法。

那么一致性測試到底是什么呢?其依據是什么?在此,筆者給出一個粗淺的定義:業界廣泛接受的用同一把尺子來衡量產品的信號質量是否符合標準的測試的統稱,其依據就是各個標準和協會組織定義的一致性測試規范CTS (Compliance Test Specification)。通過對產品進行一致性測試,除了了解產品是否符合標準測試規范外,還可以量化信號的各指標距離CTS 的裕量。如果裕量充分,則意味著可以對產品進行降成本設計,反之則需要重新設計。對于系統廠家,在快速變化的市場和殘酷激烈的競爭面前,降低產品成本是生存的法寶。對于上游芯片廠家而言,基于其芯片的系統經過一致性測試如果可以顯示出有非常高的裕量,則可以表明其產品的性能,為其下游客戶的產品設計和開發提供了充分的信心和裕量以供進行降成本設計。因此一致性測試對于整個行業而言其重要性不言而明。

近年來隨著數字技術和芯片集成技術的發展,電子電路調試(Debug)在電子產品開發工作中占比越來越小,而一致性測試作為產品最終出貨前的一環日益重要也事實成為示波器最重要的用途。

一致性測試的含義或要素

一致性測試如此重要,那么其含義是什么或者說前面給出的定義同一把尺子包含哪些要素?

1. 統一的標準的測試信號

這個統一的標準的測試信號,英文名稱是Compliance Pattern。從 USB2.0 開始 Intel專門針對 PC 系統開發了一個軟件發包工具(USBHSETTool)發出各種信號,比如測試眼圖的 Test Packet等。發展到今天支持USB3.x 標準的 被測設備在上電后發出 IN包如果未檢測到ACK 包,即進入 Compliance 測試模式,發出各種 Compliance Pattern. PCIExpress 標準的原理類似。也有特例,比如顯示技術HDMI 就不太一樣,Sink 設備一般無高速信號回傳給源端,因此需要采用外接EDID Emulator 來欺騙源端設備已經外接某一格式的 Sink 設備,源端設備就會開始輸出信號。而DisplayPort 標準和 SATA標準通常需要修改寄存器配置測試碼型。有的標準還支持通過外接控制器用軟件進行自動化配置測試碼型以配合一致性測試,比如 Unigraf公司開發的 DP 測試控制器和 Wilder 公司開發的 Thunderbolt 控制器。

為什么會定義統一的測試信號呢?因為采用不同的碼型進行測試,得出的測量結果也是不一樣的。比如采用 0101 碼型和采用00110011碼型,得到的 ISI 抖動肯定是有差異的。所以為了統一和規范測量,協會和標準組織定義了標準的測試碼型。當前最典型的是USB3.1 標準定義了多種分別用于不同測試項目的碼型:

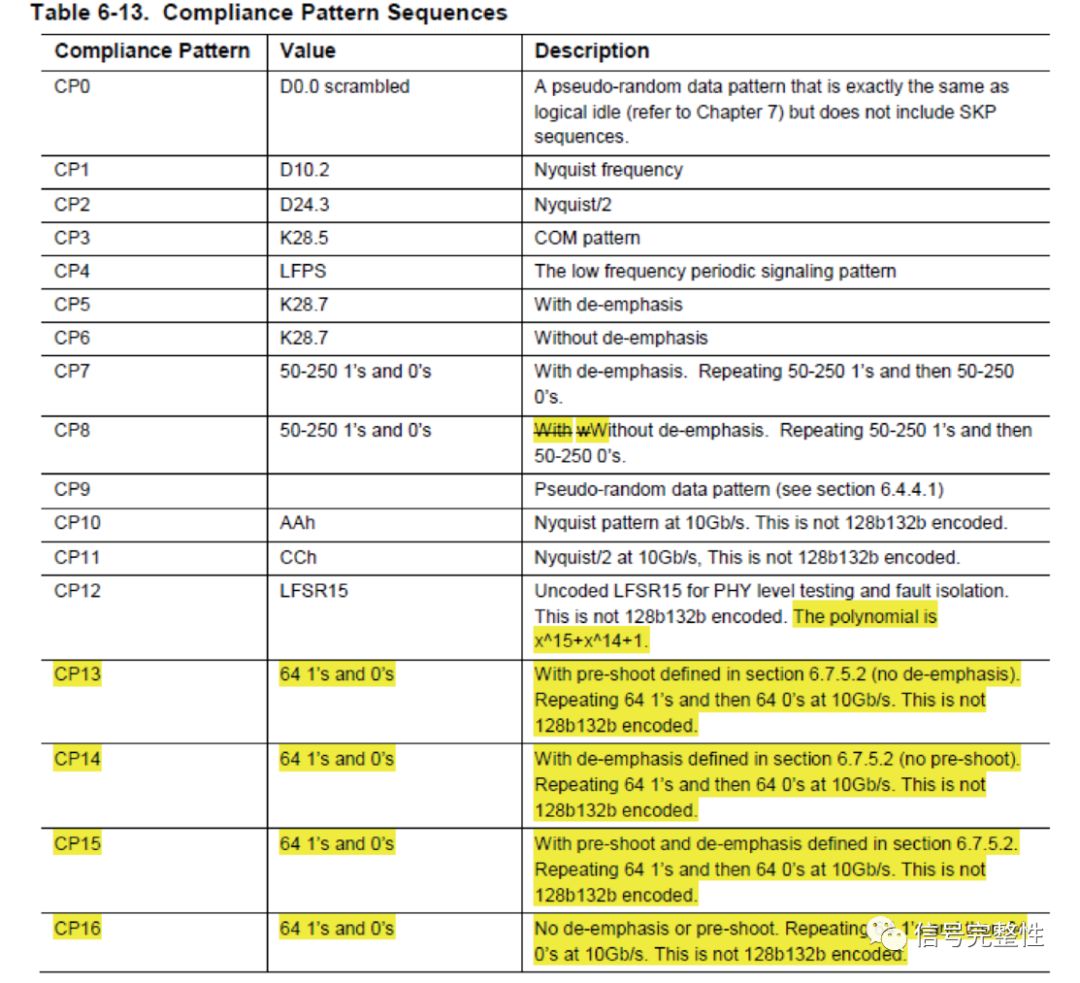

表 1. USB3.x測試碼型表

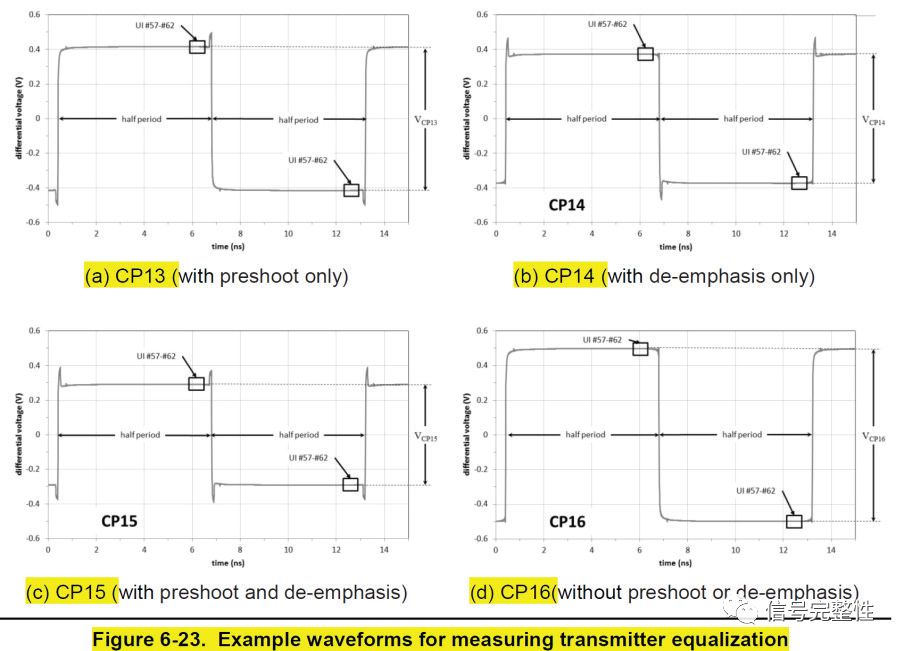

以上黃色標注的碼型CP13-CP16,是 USB3.1 規范里新增加用于測試發送端預/去加重或均衡的碼型:

圖 1. USB3.1 CP13-CP16 碼型說明圖

2. 標準的連接方式,通常為夾具和電纜組合

另外為了統一測試環境,協會和標準組織還定義了標準的連接方式,通常采用協會或第三方公司開發的標準夾具和電纜。夾具和電纜通常都是為了方便測試連接而引入的部件,必然會引入測試誤差,降低系統的測試裕量。因此在一致性測試過程中,必須要求采用相同的測試工具以標準化測量避免測試差異。在當下主流的各種標準中,除了USB3.x 和 PCIE 夾具依然主要是由 Intel主導的 USB-IF 和 PCI-Sig 協會組織提供外,其它各種標準的夾具 Wilder 公司均可提供。在測試連接上,HDMI標準由于最初需要接入 3 對 Data,1 對CLK 同時進行測試,采用了夾具 連接 SMA 探頭再連接到示波器上進行測試,以實現一次完成所有差分項目的測試。

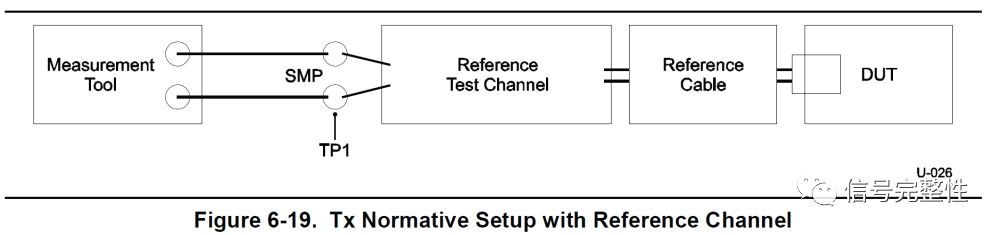

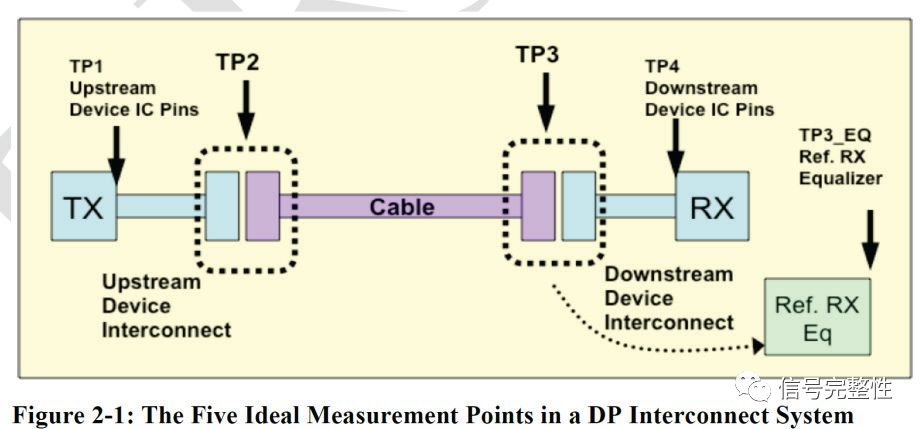

在標準和規范定義中,一般會定義若干測試點,比如USB2.0 規范里定義了 TP1,TP2,TP3,TP4.TP2 是典型的 Host 測試點位置,而 TP3 則是典型的 Device 設備的測試點位置。不同的標準定義的測試點含義不同,比如到 USB3.x標準則主要定義了 TP1 ―發送端測試的遠端測試點,而 TP0通常指發送端近端測試點僅在示波器的測試軟件里作為 Informative 測試:

圖 2. USB3.x 測試方法拓撲說明圖

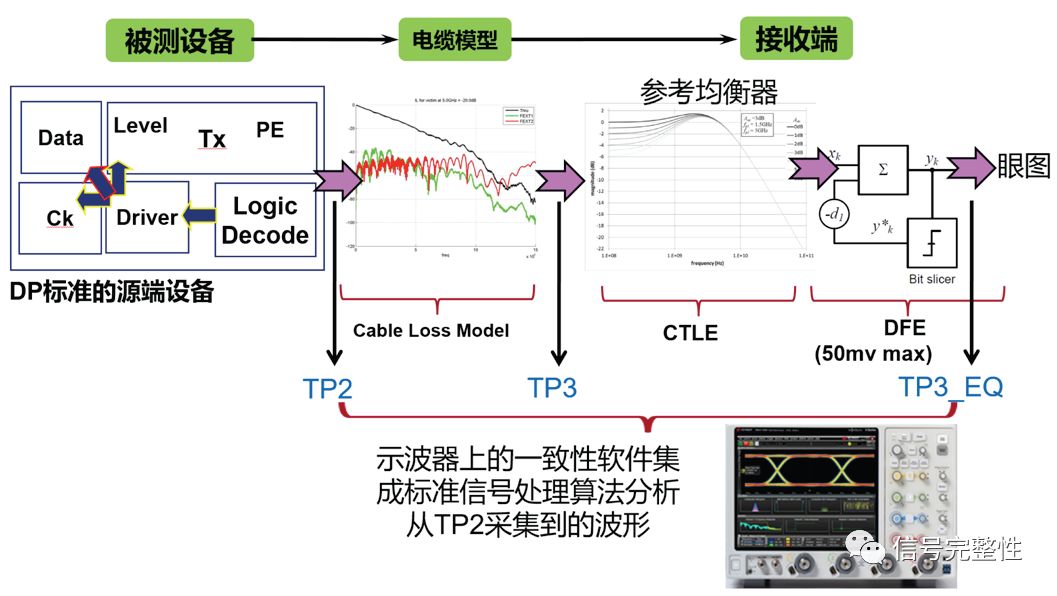

近兩年在信號速率持續推高到5Gbps 以上后,通常在測試點上還引入了 TPxEQ 測試點,比如DP1.4 標準中,定義的測試點就是TP3_EQ,這個測試點通常表征的是接收系統里經過均衡算法后的測試點,而實際測試中通常是無法探測得到的,需要在示波器上的一致性測試軟件里模擬接收端的均衡算法:

圖 3. DP1.4 測試點定義和拓撲圖

3. 標準的測試算法和流程

被測設備發出標準的測試碼型并通過夾具和電纜連接到示波器后,示波器作為接收端,模擬芯片接收端的信號處理方法對信號進行測試和分析,除了常規的針對信號的電氣特性參數測量外,通常還要執行眼圖和抖動分析。本文提到的標準測試算法在早年主要指時鐘恢復和眼圖與抖動分析方法,比較簡單。近幾年在高速串行總線系統普遍引入和嵌入和均衡等技術,信號分析算法程度大大提高。

典型的外部接口標準如USB3.x/HDMI2.x/DP1.4 均需要測試遠端眼圖,在實際連接中采用的是在被測設備近端即發送端用夾具拾取信號然后嵌入標準提供的電纜參數模型模擬真實的傳輸電纜,此有損電纜參數模型給信號帶來很大的衰減,在接收端必須采用均衡算法(CTLE/FFE+DFE)恢復信號。示波器上運行的一致性測試軟件則會完全嵌入接收端的標準均衡算法恢復信號然后進行各參數分析和眼圖與抖動測試。以 DP1.4標準為例:

圖 4 DP1.4 測試原理框圖

可見,在今天的高速信號測試中,一致性測試軟件的地位和作用日益重要。一致性測試軟件除了執行標準的測試算法進行分析并給出測試結果外,有時還可以進行一些配置的改變以進行調試性測試,即修改一些測試配置參數和選項,稱之為DebugMode。

一致性測試軟件在測試完畢后會將所有測試結果整理輸出成為報告,在報告中會專門標注每個測試項目的裕量水平,比如下表所示KeThunderbolt N6470B 測試報告,綠色方框內分三列顯示測量值,裕量及 Pass/Fail判斷:

表 2 Thunderbolt 一致性測試軟件結果報告

事實上,今天Server,PC 和筆記本行業的很多接口標準比如PCIE,SATA, USB3.x等,業界主導公司 Intel 還開發了專門的測試軟件 Sigtest可以進行數據后分析。在 Sigtest 軟件里會針對不同的標準不同的測試點定義一些不同的測試腳本文件(在 Sigtest安裝文件夾的 Template 文件夾里)。標準的一致性測試軟件中通常也可以調用 Sigtest 程序里的 DLL(動態鏈接庫)文件執行此行業內主導公司的標準算法測試。

由于篇幅和標準的多樣性及水平有限,本文這里就不再對測試算法做深入探討和描述。

4. 影響一致性測試精度的因素

前面我們描述了一致性測試的含義與本質,一致性測試到底在追求什么?歸根結底是裕量(Margin)。其本質或者最終的動機就是降成本。對于系統廠家而言,在產品設計完成后如果經過一致性測試,發現信號質量距離 CTS 規范規定的要求有較大的裕量,那就意味著可以對產品進行降成本設計,比如可以減少電容,或者采用更廉價的連接器乃至降低 PCB 層數等,所有的每一個看起來很小的降成本考慮,在規模化的大批量生產時都會被放大,從而帶來可觀的經濟效益。當然降成本設計也不是無底線的,底線就是CTS,所以業界有很多廠家有時會反復對產品進行設計和測試以找到最終的平衡點,示波器在這個過程中就在扮演重要的角色。對于芯片或產業鏈上游廠家而言,在產品設計完成后也需要進行參考設計并做一致性測試驗證以提交報告給下游廠家,以證明其產品的高品質和大裕量并給予其客戶足夠的信心以進行降成本設計。

測試測量過程必然會帶來誤差,那么如何將誤差降到最小或得到最高的Margin?除了我們前面討論的 3 點,確保進行正確的一致性測試外,就必須要從儀器設備方面考慮。首先是要選擇恰當的示波器,示波器的一些指標如帶寬,采樣率,底噪和抖動等均會影響一致性測試的裕量。關于帶寬是很多人都比較耳熟能詳的指標,經常提到的選擇正弦波3-5被帶寬以及方波 9 倍頻率的帶寬等,針對一般的高速串行總線數據(NRZ編碼)過去主要采用一種速算法:信號頻率/2*5,比如 5GBps 的 NRZ 信號,基波頻率為2.5GHz,采用2.5GHz*5=12.5GHz 以上即可。另外更加準確的是根據被測信號的上升沿時間計算帶寬,通常為20%-80% 上升沿時間,信號頻率 Bw=0.4/Tr,推薦的示波器帶寬再乘以1.4~1.8 左右的系數即可。帶寬不能滿足測試要求會直接削減信號的幅度從而直接影響到眼高幅度和上升沿的準確測試。

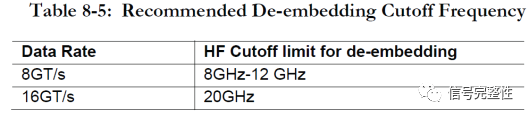

近年隨著技術的發展去嵌和均衡的引入,這一規則也在改變。比如針對PCIE4.0 16.0Gbps,為了防止去嵌過度放大儀器的本底噪聲,因此在 PCIE4.0 規范里給出的推薦的 CTLE 和去嵌的截止帶寬頻率是 20GHz:

表 3 PCIE4.0 規范推薦的去嵌截止頻率點

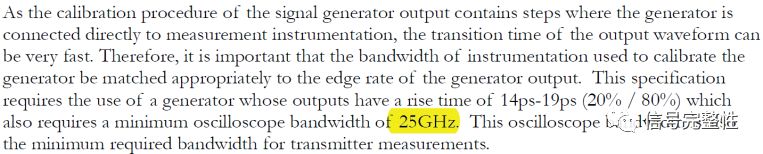

另一方面針對RX測試時的信號源校準為了確保精確校準誤碼儀輸出的信號的邊沿,在規范里推薦了 25GHz 帶寬的示波器進行測試:

兩者兼顧,在CEM 測試中針對 PCIE4.0 推薦的帶寬就是 25GHz:

圖 5 PCIE4.0 Compliance Updates 關于一致性測試帶寬說明

采樣率是示波器另外一個重要指標。對今天的數字實時示波器而言,采樣率必須是示波器帶寬的2.5 倍才能保證將信號準確還原。雖然奈奎斯特采樣定理指出 2 倍采樣可將信號還原,但是奈奎斯特定理針對的信號是正弦波,而今天的被測信號多為高速數字信號。

另外兩個比較明顯的影響比較大的指標是示波器的本底噪聲和抖動。示波器的固有抖動對眼圖測試時的影響也是類似的,必然會增加抖動類相關項目測試的誤差。由于均衡和去嵌均在信號垂直幅度方向對信號進行補償,疊加在固有抖動上的作用和影響需要進行嚴格的數學運算定量分析。對于還需要采用探頭進行測試的HDMI 接口,探頭接入信號時由于其固有的衰減特性在對信號衰減后才會進入示波器的前端和 ADC 采樣,示波器會對信號再進行放大同時會放大本底噪聲,因此探頭的衰減倍數也是影響一致性測試精度和裕量的因素之一。關于示波器的本底噪聲對眼圖測試的影響可參見參考文獻《淺論示波器的低本底噪聲對高速眼圖測試的意義》。

一致性測試的發展趨勢

最后再來談談一致性測試的發展趨勢。

作為產品出貨前的重要環節,一致性測試既然在今天的各種產品研發和制造中扮演著如此重要的作用,必然會帶來巨大的工作量和負擔。因此從最初的幾百MBps 級的 USB2.0 和 Ethernet10/100/1000 BaseT 到今天的幾十 Gbps 的高速串行數據標準,一直在朝向更加簡單,更加標準化,更加自動化的方向發展,最終的宗旨和目的是為了降低測試復雜程度,提高生產效率。

更加簡單,主要體現在測試碼型的輸出上。如前文討論,從最初的需要專門的發包軟件或者改寄存器輸出測試信號到今天的內置BIST(Built in Self-Test Pattern)測試碼型,目前在 PCIEXpress和 USB3.x 上均已實現。在 DisplayPort 和Thunderbolt 兩種標準上,則有第三方開發的專門的測試碼型控制器,比如 Unigraf提供的 DP 控制器和 Wilder 公司提供的Thunderbolt 控制器。

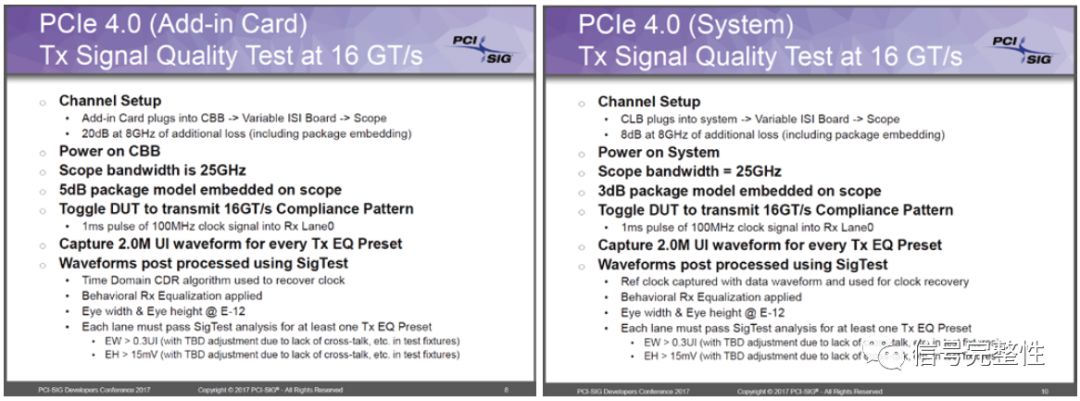

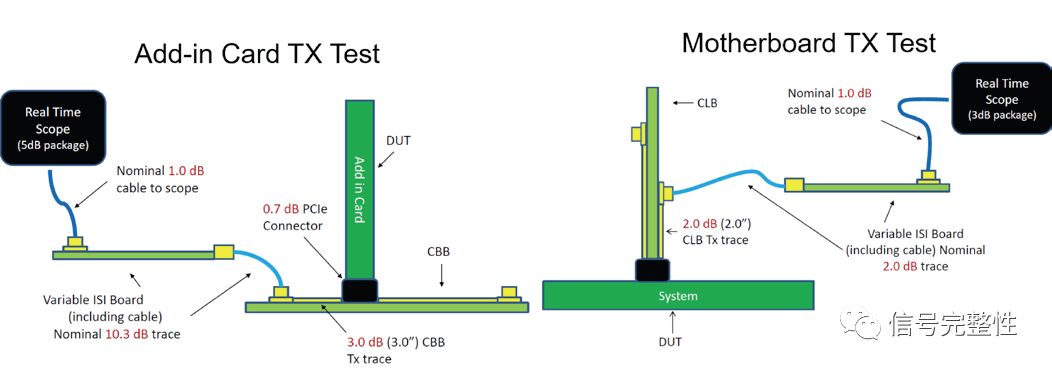

更加標準化,體現在測試連接的定義上。比如在USB3.0 測試方法的定義上,最初定義采用通過協會認可的實物電纜來模擬遠端測試點,但是后來由于實物電纜依然存在差異,因此后來采用S參數模型替代實物電纜,如此完全消除了不同連接環境的差異。這一方法今天在 HDMI2.0/DP1.4 也得到了應用。在 PCIE4.0規范里,也采用了類似的方法,不過不是軟件 S參數模型而是采用由協會提供的一塊硬件的 ISI 夾具板來模擬整個鏈路,以 CEMAdd-inCard TX 測試為例,專門設計了 ISI 夾具板用于模擬額外的標準 20dB@8GHz損耗:

圖 6 PCIE4.0 CEM 測試原理框圖

圖 7 PCIE4.0 CEM ISI 夾具板

這一硬件 ISI夾具由 PCI-Sig 協會組織出售,具有唯一性和標準性。未來是否會采用軟件的S 參數模型方法去實現,當然也不排除這種可能性。

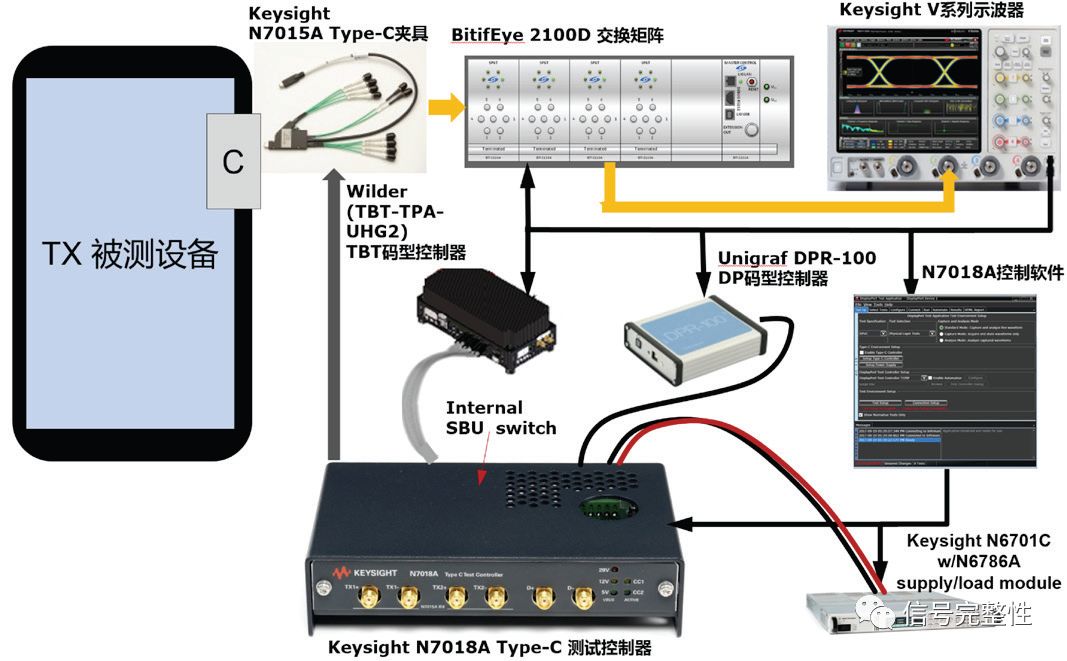

最后一個趨勢是,測試自動化的要求日益凸顯。由于多種標準和接口紛繁復雜,給消費者帶來許多使用上的困擾,同時也加劇了研發設計和測試的復雜性。因此產業界正在努力推廣采用唯一的Type-C接口,USB,DP,HDMI,Thunderbolt 等標準均支持這一接口。如下為一個完整的測試方案:

圖 8 Type-C 接口測試方案框圖

如上圖,采用N7015A Type-C 夾具和 N7018A 控制器,配合交換矩陣,完成所有連接后,運行在示波器上的N7018A 控制軟件會自動設置 Type-C Alt Mode,切換 Type-C 接口為為 USB,DP或TBT 模式,N7018A 控制器可以輸出LFPS 信令,配置 DUT 發出USB3.x 標準的測試碼型,針對 Thunderbolt 和 DP 則分別需要Wilder 和 Unigraf 控制器配置測試碼型。被測信號從 N7015A 夾具連接到交換矩陣,然后再連接到示波器上,示波器會通過網口控制切換交換矩陣切換不同鏈路的信號到示波器上。如果需要測試不同的被測設備,也只需將設備連接到N7015 夾具上即可。

總結

本文討論了發送端物理層一致性測試的含義,要素及目標和趨勢,囿于篇幅無法就許多細節進行詳細說明。除了發送端之外,近幾年接收端的一致性測試隨著信號速率的飛速提升也開始成為各種標準必須考慮的測試內容,請留意更多論述和分享。

-

物理層

+關注

關注

1文章

152瀏覽量

34412 -

一致性測試

+關注

關注

0文章

30瀏覽量

12025

原文標題:【干貨】詳述高速串行總線的物理層一致性(Compliance)測試

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MIPI D-PHY物理層自動一致性測試

探討發送端物理層一致性測試的含義,要素及目標和趨勢

探討發送端物理層一致性測試的含義,要素及目標和趨勢

評論